크레이-1

Cray-1| 크레이-1 | |

|---|---|

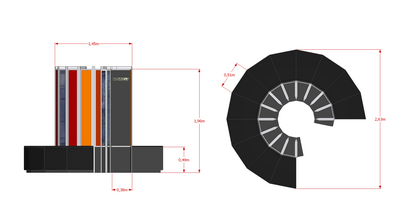

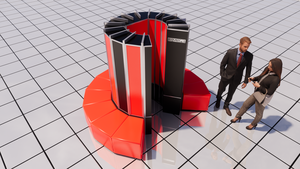

2개의 숫자를 축척으로 한 Cray-1의 3D 렌더링 | |

| 설계. | |

| 제조원 | 크레이 리서치 |

| 디자이너 | 시모어 크레이 |

| 발매일 | 1975 |

| 판매대수 | 100 이상 |

| 가격. | 1977년 790만달러(2021년 3530만달러 상당) |

| 케이스 | |

| 치수 | 높이: 196cm(77인치)[1] 디아 (베이스): 263 cm (104 인치)[1] 디아(칼럼): 145cm(57인치)[1] |

| 체중 | 5.5톤 (Cray-1A) |

| 힘 | 115kW(208V 400Hz시[1]) |

| 시스템. | |

| 프런트 엔드 | 데이터 일반 이클립스 |

| 운영 체제 | COS 및 UNICOS |

| CPU | 64비트 프로세서(80MHz시[1]) |

| 기억 | 8.39 MB (최대 1,048,576 워드)[1] |

| 보관소 | 303 MB (DD19 유닛)[1] |

| 플로피 | 160 MFLOPS |

| 후계자 | Cray X-MP |

Cray-1은 Cray Research에서 설계, 제조 및 판매한 슈퍼 컴퓨터입니다.1975년에 발표된 최초의 Cray-1 시스템은 1976년에 로스 알라모스 국립 연구소에 설치되었습니다.결국 100대 이상의 Cray-1이 판매되어 역사상 가장 성공적인 슈퍼컴퓨터 중 하나가 되었습니다.이것은 아마도 독특한 형태로 가장 잘 알려져 있을 것입니다. 비교적 작은 C자형 캐비닛으로 전원 공급 장치와 냉각 시스템을 덮는 외부 둘레에 벤치가 둘러져 있습니다.

Cray-1은 벡터 프로세서 설계를 성공적으로 구현한 최초의 슈퍼 컴퓨터입니다.이러한 시스템은 메모리 및 레지스터를 배열하여 대용량 데이터 세트에 대해 단일 연산을 신속하게 수행함으로써 연산 성능을 향상시킵니다.CDC STAR-100이나 ASC와 같은 이전 시스템에서는 이러한 개념이 구현되어 있었지만 퍼포먼스가 크게 제한되었습니다.Cray-1은 이러한 문제를 해결하고 유사한 설계보다 몇 배 더 빠르게 작동하는 기계를 생산했습니다.

Cray-1의 설계자는 Seymour Cray였고, 수석 엔지니어는 Cray Research의 공동 설립자 Lester [2]Davis였습니다.그들은 계속해서 동일한 기본 개념을 사용하여 몇 개의 새로운 기계를 설계했고, 1990년대에도 최고의 성능을 유지했습니다.

역사

1968년부터 1972년까지 제어 데이터 코퍼레이션(CDC)의 Seymour Cray는 이전 CDC 6600 및 CDC 7600 설계의 후속 모델인 CDC 8600을 개발했습니다.8600은 기본적으로 4개의 7600이 상자에 들어 있고 SIMD 방식으로 잠금 스텝을 작동할 수 있는 추가 특수 모드로 구성되어 있습니다.

이전에 Cray의 엔지니어링 파트너였던 Jim Thornton은 CDC STAR-100으로 알려진 보다 급진적인 프로젝트를 시작했습니다.퍼포먼스에 대한 8600의 강력한 접근과는 달리 STAR는 전혀 다른 경로를 택했습니다.STAR의 메인 프로세서는 7600보다 성능이 낮았지만 하드웨어와 명령을 추가하여 일반적인 슈퍼컴퓨터 작업을 고속화합니다.

1972년에 8600은 막다른 골목에 다다랐습니다. 기계는 너무 복잡해서 제대로 작동하는 것이 불가능했습니다.단 하나의 불량 컴포넌트라도 기계를 동작시킬 수 없게 됩니다.Cray는 Control Data의 CEO인 William Norris에게 가서 처음부터 재설계가 필요하다고 말했습니다.당시 회사는 심각한 재정난에 빠졌고, STAR도 진행 중이어서 노리스는 그 돈을 투자할 수 없었다.

그 결과 Cray는 CDC를 떠나 CDC 랩에 매우 가까운 곳에서 Cray Research를 시작했습니다.치페와폭포에 매입한 토지 뒷마당에서 크레이와 CDC 전직 직원들은 아이디어를 찾기 시작했다.처음에는 슈퍼컴퓨터를 하나 더 만드는 것이 불가능해 보였지만, Cray Research의 최고기술책임자(CTO)가 월스트리트를 방문하여 Cray를 지원하는 투자자들의 라인업을 찾은 후, 필요한 것은 디자인뿐이었다.

Cray Research는 4년간 최초의 컴퓨터를 [3]설계했다.1975년에 80MHz Cray-1이 발표되었습니다.첫 번째 기계는 Lawrence Livermore National Laboratory와 Los Alamos National Laboratory 사이에 입찰전이 벌어졌고, Lawrence Livermore National Laboratory는 결국 1976년 6개월간의 시험으로 일련번호 001을 획득하고 수령했습니다.국립대기연구센터(NCAR)는 1977년 Cray Research의 첫 공식 고객으로 시리얼 번호 3에 대해 미화 886만 달러(790만 달러 + 디스크 값 100만 달러)를 지불했습니다.NCAR 기계는 [4]1989년에 해체되었다.이 회사는 이 기계를 12대 정도 판매하고 그에 따라 판매 가격을 책정할 것으로 예상했지만, 최종적으로 모든 유형의 Cray-1이 80대 이상 판매되었으며 가격은 500만 달러에서 800만 달러까지 책정되었습니다.이 기계는 Seymour Cray와 그의 회사를 유명인사로 만들어 1990년대 초 슈퍼컴퓨터가 고장날 때까지 지속시켰다.

윌리엄 페리의 연구에 의한 권고에 따라 NSA는 암호 분석 이론 연구를 위해 Cray-1을 구입했다.Budiansky에 따르면, "Cray Research의 표준 역사가 수십 년 동안 지속되기는 했지만, 회사의 첫 고객은 Los Alamos National Laboratory였고, 사실은 [5]NSA였습니다."

160 MFLOPS Cray-1은 1982년 최초의 Cray 멀티프로세서 컴퓨터인 800 MFLOPS Cray X-MP에 의해 성공했습니다.1985년 1.9 GFLOPS 피크 성능을 갖춘 매우 진보된 Cray-2는 처음 두 모델을 성공시켰지만 실제 애플리케이션에서 지속적인 성능을 생산하는 데 문제가 있어 다소 제한적인 상업적 성공을 거두었습니다.따라서 Cray-1과 X-MP 모델의 보다 보수적으로 설계된 진화적 후속 모델은 Cray Y-MP라는 이름으로 만들어졌으며 1988년에 출시되었습니다.

이에 비해 Google Nexus 10이나 HTC One과 같은 일반적인 2013년형 스마트 디바이스의 프로세서는 [6]약 1GFLOPS의 성능을 발휘하는 반면 2020년형 iPhone 11의 A13 프로세서는 154.9GFLOPS의 [7]성능을 발휘하는데, 이는 Cray-1의 뒤를 잇는 마크 슈퍼컴퓨터가 1994년에 이르러야 달성할 수 있을 것이다.

배경

일반적인 과학적 워크로드는 대규모 데이터 세트를 읽고 어떤 식으로든 변환한 후 다시 쓰는 것으로 구성됩니다.일반적으로 적용되는 변환은 세트 내의 모든 데이터 포인트에서 동일합니다.예를 들어, 프로그램은 백만 개의 숫자 집합의 모든 숫자에 5를 더합니다.

전통적인 컴퓨터에서는 이 프로그램이 모든 백만 개의 숫자를 루프하고 다섯 개를 더하면 백만 개의 명령을 실행하여 다음과 같은 명령을 실행합니다.a = add b, c내부적으로는, 이 순서를 몇개의 스텝으로 해결합니다.먼저 메모리에서 명령을 읽고 디코딩한 다음 필요한 추가 정보(이 경우 숫자 b와 c)를 수집하고 마지막으로 작업을 실행하여 결과를 저장합니다.결과적으로 컴퓨터는 이러한 작업을 수행하기 위해 수천 또는 수억 번의 사이클을 필요로 합니다.

벡터 머신

STAR 에서는, 새로운 지시에 의해서, 유저의 루프가 기술되고 있습니다.사용자는 메모리에 번호 목록이 저장된 위치를 기계에 알린 다음 단일 명령으로 입력했습니다.a(1..1000000) = addv b(1..1000000), c(1..1000000)얼핏 보면 절약되는 비용은 제한적으로 보입니다.이 경우 기계는 1,000,000이 아닌 하나의 명령만 가져오고 디코딩하므로 전체 시간의 1/4에 해당하는 1,000,000개의 페치 및 디코딩을 절약할 수 있습니다.

진짜 저축은 그렇게 명백하지 않다.내부적으로 컴퓨터의 CPU는 예를 들어 번호 추가나 메모리에서 가져오기 등 단일 태스크 전용의 여러 개별 부품으로 구성됩니다.일반적으로 명령이 기계를 통해 흐르면 한 번에 한 부분만 활성화됩니다.즉, 전체 공정의 각 순차적 단계를 완료해야 결과를 저장할 수 있습니다.명령 파이프라인을 추가하면 이 내용이 변경됩니다.이러한 머신에서는, 현재의 명령어가 처리되고 있는 동안, CPU는 「앞을 내다보고」, 후속 명령의 취득을 개시합니다.이 조립 라인 방식에서는 하나의 명령이 완료되는 데 걸리는 시간은 여전히 길지만, 실행이 완료되는 즉시 다음 명령이 바로 뒤에 있으며, 실행에 필요한 대부분의 단계가 이미 완료되어 있습니다.

벡터 프로세서는 이 기술을 한 가지 추가 트릭과 함께 사용합니다.데이터 레이아웃은 알려진 형식(메모리에 순차적으로 배열된 숫자 집합)이므로 파이프라인을 조정하여 가져오기 성능을 향상시킬 수 있습니다.벡터 명령을 수신하면 특수 하드웨어가 어레이의 메모리 액세스를 설정하고 데이터를 가능한 한 빨리 프로세서에 넣습니다.

STAR에서의 CDC의 어프로치에서는, 현재의 메모리·메모리·아키텍쳐(architecture)라고 불리는 것을 사용했습니다.이것은 기계가 데이터를 수집하는 방법을 가리킵니다.메모리에서 직접 읽고 쓰도록 파이프라인을 설정합니다.이것에 의해, STAR는 레지스터의 길이에 의해서 제한되지 않는 길이의 벡터를 사용할 수 있게 되어, 매우 유연성이 높아졌습니다.불행하게도, 느린 기억을 만회하기 위해 비행 중에 충분한 지시를 받기 위해서는 파이프라인이 매우 길어야 했다.즉, 프로세싱 벡터에서 비벡터 오퍼랜드에 대한 연산을 수행할 때 기계가 높은 비용을 발생시켰습니다.또, 스칼라 퍼포먼스가 낮기 때문에, 스칼라 명령어를 실행하고 나서, 스칼라 명령어를 실행한 후에는 퍼포먼스가 매우 저하하고[citation needed] 있었습니다.그 결과는 Amdahl의 법칙에 의해 예측될 수 있는 실제 환경에서 다소 실망스러운 결과를 낳았다.

크레이의 접근법

Cray는 STAR의 고장을 연구했고 그것으로부터[citation needed] 배웠다.그는 빠른 벡터 처리와 더불어 뛰어난 전방위 스칼라 성능을 필요로 한다고 판단했습니다.그러면 기계가 모드를 전환해도 여전히 뛰어난 성능을 제공할 수 있습니다.또한 대부분의 경우 레지스터를 사용하여 워크로드를 획기적으로 개선할 수 있음을 알게 되었습니다.

이전 기계가 대부분의 작업이 많은 데이터 포인트에 적용된다는 사실을 무시했듯이 STAR는 동일한 데이터 포인트가 반복적으로 작동한다는 사실을 무시했습니다.STAR는 데이터 세트에 5개의 벡터 연산을 적용하기 위해 동일한 메모리를 5회 읽고 처리하지만 CPU 레지스터에 데이터를 한 번 읽고 5개의 연산을 적용하는 것이 훨씬 빠릅니다.그러나 이 접근법에는 한계가 있었다.레지스터는 회로 측면에서 훨씬 더 비쌌기 때문에 제한된 수 밖에 제공되지 않았습니다.이는 Cray의 디자인이 벡터 크기 측면에서 유연성이 떨어진다는 것을 암시합니다.Cray-1은 STAR와 같은 크기의 벡터를 여러 번 읽는 대신 한 번에 벡터의 일부만 읽으면 되지만 결과를 메모리에 다시 쓰기 전에 해당 데이터에 대해 몇 가지 연산을 실행할 수 있습니다.일반적인 워크로드를 고려할 때, Cray는 대규모 순차적 메모리 액세스를 세그먼트로 분할해야 하는 적은 비용이 지불할 가치가 있는 비용이라고 생각했습니다.

전형적인 벡터 연산은 작은 데이터 집합을 벡터 레지스터에 로드하고 그 위에서 여러 연산을 실행하는 것을 포함하므로, 새로운 설계의 벡터 시스템은 그것 자체의 별도의 파이프라인을 가지고 있었다.예를 들어 곱셈 및 덧셈 유닛은 별도의 하드웨어로 구현되었기 때문에 하나의 유닛의 결과는 다음 유닛으로 내부적으로 파이프라인될 수 있으며 명령 디코딩은 이미 머신의 메인 파이프라인에서 처리되었습니다.Cray는 이 개념을 체인이라고 불렀는데, 이는 프로그래머들이 여러 명령어를 "체인"하고 더 높은 성능을 추출할 수 있게 해주었기 때문입니다.

묘사

새로운 기계는 집적회로(IC)를 사용한 최초의 크레이 설계였다.IC는 1960년대부터 사용 가능했지만, 고속 애플리케이션에 필요한 성능에 도달한 것은 1970년대 초반이었다.Cray-1은 4가지 IC 타입, ECL 듀얼 5-4 NOR 게이트(각각 차동 출력 포함),[8] 주소 팬아웃에 사용되는 또 다른 느린 MECL 10K 5-4 NOR 게이트, 레지스터에 사용되는 16×4비트 고속(6ns) 스태틱 RAM(SRAM) 및 1×241 ns만을 사용했습니다.이들 집적회로는 페어차일드 반도체와 모토로라가 공급했다.모두 합쳐서, 크레이-1에는 약 20만 개의 게이트가 있었다.

IC는 대형 5층 프린트 회로 기판에 장착되었으며, 기판당 최대 144개의 IC가 있습니다.그런 다음 보드를 냉각하기 위해 등을 맞대고 장착하고(아래 참조), 72개의 더블 보드가 포함된 24개의 28인치(710mm) 랙에 배치했습니다.일반적인 모듈(구별 처리 장치)에는 1개 또는 2개의 보드가 필요했습니다.모든 기계에는 113가지 종류의 1,662개의 모듈이 포함되어 있었다.

모듈 간의 각 케이블은 꼬임 쌍으로, 신호가 정확한 시간에 도착하고 전기 반사를 최소화하기 위해 특정 길이로 절단되었습니다.ECL 회로에 의해 생성되는 각 신호는 차동 쌍이었기 때문에 신호의 밸런스는 유지되었습니다.이것에 의해, 전원 장치의 요구가 일정하게 되어, 스위칭 노이즈가 감소하는 경향이 있습니다.전원장치의 부하가 매우 균등하게 분산되어 있기 때문에 Cray는 전원장치가 규제되어 있지 않다고 자랑했습니다.전원장치에서는 컴퓨터 시스템 전체가 단순한 저항처럼 보였다.

고성능 ECL 회로는 상당한 열을 발생시켰으며, Cray의 설계자들은 나머지 기계 설계와 마찬가지로 냉동 시스템 설계에 많은 노력을 기울였습니다.이 경우, 각 회로 기판은 두 번째 회로 기판과 짝을 이루어 구리판을 사이에 두고 등을 맞대고 배치되었습니다.구리 시트는 케이지의 가장자리에 열을 전달하고 스테인리스강 파이프에 흐르는 액체 프레온이 기계 아래의 냉각 장치로 열을 끌어냈습니다.첫 번째 Cray-1은 냉각 시스템의 문제로 인해 6개월 지연되었습니다. 일반적으로 컴프레서를 계속 작동시키기 위해 Freon과 혼합된 윤활유가 씰을 통해 누출되어 최종적으로 보드가 단락될 때까지 오일을 도포합니다.튜브를 적절히 밀봉하기 위해 새로운 용접 기술이 사용되어야 했다.

기계에서 최대한의 속도를 내기 위해 섀시 전체를 큰 C자 모양으로 구부렸습니다.시스템의 속도 의존 부분은 와이어 길이가 짧은 섀시의 "내부 가장자리"에 배치되어 있습니다.이것에 의해, 사이클 타임을 12.5 ns(80 MHz)로 단축할 수 있었습니다.이는 포기한 8 ns 8600만큼 빠르지는 않지만 CDC 7600과 STAR를 이길 수 있을 만큼 빠릅니다.NCAR는 시스템의 전체 throughput이 CDC [10]7600의 4.5배라고 추정했습니다.

Cray-1은 64비트 시스템으로 구축되었으며, 이는 60비트 머신이었던 7600/6600에서 출발한 것입니다(8600에서도 변경이 계획되었습니다).어드레싱은 24비트로, 최대 1,048,576개의 64비트 워드(1메가워드)의 메인 메모리로, 각 워드에는 8개의 패리티 비트가 있으며,[11] 워드당 총 72비트의 패리티 비트가 있습니다.64개의 데이터 비트와 8개의 체크 비트가 있었습니다.메모리는 16개의 인터리브 메모리 뱅크에 분산되어 있으며 각각 50ns의 사이클 타임을 가지며 사이클당 최대 4개의 워드를 읽을 수 있습니다.소형 구성에서는 0.25 또는 0.5메가워드의 메인메모리를 가질 수 있습니다.최대 집약 메모리 대역폭은 638 Mbit/[11]s였습니다.

메인 레지스터 세트는 8개의 64비트 스칼라(S) 레지스터와 8개의 24비트 주소(A) 레지스터로 구성됩니다.이들은 각각 T와 B로 알려진 S와 A 임시 스토리지에 대해 64개의 레지스터 세트에 의해 지원되었으며, 기능 장치에서는 이러한 레지스터를 볼 수 없었습니다.벡터 시스템은 64비트 벡터(V) 레지스터 8개와 벡터 길이(VL) 및 벡터 마스크(VM)를 추가했습니다.마지막으로 시스템은 64비트 실시간 클럭 레지스터와 각각 64비트 명령을 저장하는 4개의 64비트 명령 버퍼를 포함했습니다.주소 레지스터와 스칼라 레지스터는 2 사이클이 필요한 반면, 벡터 레지스터는 사이클당 1 워드로 공급되도록 하드웨어가 설정되었습니다.반면 16단어 명령 버퍼는 4주기로 모두 채울 수 있습니다.

Cray-1에는 12개의 파이프라인 기능 유닛이 있습니다.24비트 주소 산술은 덧셈 단위와 곱셈 단위로 수행되었습니다.시스템의 스칼라 부분은 덧셈 단위, 논리 단위, 모집단 수, 선행 제로 카운트 단위 및 시프트 단위로 구성되었습니다.벡터 부분은 add, logical 및 shift 단위로 구성됩니다.부동소수점 함수 단위는 스칼라와 벡터 부분 간에 공유되었으며, 이들은 덧셈, 곱셈 및 역수 근사 단위로 구성되었다.

그 시스템은 제한된 병렬성을 가지고 있었다.그것은 시계주기당 대략 80MIPS의 이론적 성능을 위하여, 그러나 벡터 부동 소수 점 곱셈과 병렬 덧셈 이론적인 성능에서 일어났다 160[12]MFLOPS. 상호 근사 유닛은 병렬로,라 진정한 부동 소수 점 결과-2개의 추가 mu을 하지 않는다면 작동할 수 있는 명령을 발행할 수 있다.lti완전한 분할을 실현하기 위해서는 응용 프로그램이 필요했습니다.)

이 기계는 대규모 데이터 세트에서 작동하도록 설계되었기 때문에 I/O 전용 회로도 상당했습니다.CDC의 이전 Cray 설계에는 이 태스크 전용 컴퓨터가 포함되어 있었지만 더 이상 필요하지 않았습니다.대신 Cray-1에는 4개의 6채널 컨트롤러가 포함되어 있으며, 각 컨트롤러는 4사이클에 한 번씩 메인 메모리에 액세스할 수 있습니다.채널 폭은 16비트이고 오류 수정을 위해 3개의 제어 비트와 4비트를 포함하므로 최대 전송 속도는 100ns당 1워드, 즉 기계 전체에서 초당 500,000워드였습니다.

초기 모델인 Cray-1A의 무게는 프레온 냉동 시스템을 포함하여 5.5톤이었다.100만 워드의 메인 메모리로 구성된 이 머신과 그 전원 장치는 약 115kW의 전력을 소비했습니다.냉각과 스토리지 용량은 이 수치를 [citation needed]2배 이상 웃돌고 있습니다.Data General SuperNova S/200 미니컴퓨터는 부팅 시 시스템에 Cray 운영체제를 공급하고 사용 중 CPU를 감시하며 옵션으로 프런트 엔드 컴퓨터로서 사용되는 메인터넌스 컨트롤 유닛(MCU) 역할을 했습니다.전부는 아니더라도 대부분의 Cray-1A는 후속 Data General Eclipse를 MCU로 사용하여 제공되었습니다.

Cray-1S

1979년에 발표된 Cray-1S는 개량된 Cray-1로, 1, 200만 또는 400만 워드의 더 큰 메인 메모리를 지원합니다.더 큰 메인 메모리는 액세스 시간이 [13]25ns인 4,096 x 1비트 바이폴라 RAM IC를 사용함으로써 가능했습니다.Data General 미니컴퓨터는 옵션으로 80 MIPS로 실행되는 사내 16비트 설계로 대체되었습니다.I/O 하위 시스템은 6 Mbit/s 제어 채널과 100 Mbit/s 고속 데이터 채널을 통해 메인 시스템에 연결되어 메인 기계와 분리되었습니다.이 분리를 통해 1S는 몇 피트 떨어진 두 개의 "하프 크레이"처럼 보이게 되어 필요에 따라 I/O 시스템을 확장할 수 있게 되었습니다.시스템은 I/O가 없는 S/500에서 4개의 I/O 프로세서와 400만 워드의 메모리를 탑재한 S/4400까지 다양한 구성으로 구입할 수 있습니다.

크레이-1M

1982년에 발표된 Cray-1M은 Cray-1S를 [14]대체했다.12ns의 사이클 타임이 더 빨랐고 메인 메모리에서 더 저렴한 MOS RAM을 사용했습니다.1M은 8개 뱅크에 100만 워드를 탑재한 M/1200 또는 16개 뱅크에 200만 또는 400만 워드를 탑재한 M/2200 및 M/4200의 3가지 버전만으로 공급되었습니다.이들 머신에는 모두 2개, 3개 또는 4개의 I/O 프로세서가 탑재되어 있어 두 번째 고속 데이터 채널이 옵션으로 추가되었습니다.사용자는 800만~3200만 워드의 MOS RAM을 탑재한 솔리드 스테이트 스토리지 디바이스를 추가할 수 있습니다.

소프트웨어

1978년 Cray-1의 첫 번째 표준 소프트웨어 패키지가 출시되었으며, 세 가지 주요 제품으로 구성되어 있습니다.

- Cray 운영체제(COS) (나중에 나온 머신은 UNICOS, Cray의 UNIX 플레이버)를 실행합니다.

- Cray 어셈블리 언어(CAL)

- 최초의 자동 벡터화 Fortran 컴파일러인 Cray Fortran(CFT)

Lawrence Livermore National Laboratory, Los Alamos Scientific Laboratory, Sandia National Laboratory 및 National Science Foundation 슈퍼컴퓨터 센터(고에너지 물리용)로부터 자금을 지원받은 미국 에너지부는 LLL의 Cray Time Sharing System(CTS)을 사용하여 두 번째로 큰 블록이었습니다.처음에 LRLTRAN이라는 이름의 amic 메모리 Fortran은 CDC 7600s에서 실행되었으며 Cray-1에 대한 벡터화가 추가되었을 때 CVC ("Civic"으로 발음됨)로 이름이 변경되었습니다.Cray Research는 이에 따라 이들 사이트를 지원하려고 시도했다.이러한 소프트웨어 선택은 "crayette"라고도 불리는 최신 미니 슈퍼컴퓨터에 영향을 미쳤다.

NCAR은 자체 운영 체제(NCAROS)를 가지고 있습니다.

National Security Agency는 자체 운영 체제(Folklore)와 언어(Cray Pascal 및 C 및 Fortran 90 [15]이후 포트를 사용한 IMP)를 개발했습니다.

라이브러리는 Cray Research의 자체 제품과 Netlib에서 시작되었습니다.

다른 운영체제가 존재했지만 대부분의 언어는 Fortran 또는 Fortran 기반이었습니다.Bell Laboratories는 휴대성의 개념과 회로 설계의 증거로서 최초의 C 컴파일러를 Cray-1(비벡터라이징)로 옮겼습니다.이 법령은 나중에 CRI에게 Cray-2 Unix 포트의 6개월을 ETA Systems의 손해와 Lucasfilm의 첫 컴퓨터 제작 테스트 영화인 The Adventures of Andre & Wally B의 손해를 입힐 것이다.

애플리케이션 소프트웨어는 일반적으로 분류(예: 핵 코드, 암호 분석 코드) 또는 독점(예: 석유 저장고 모델링)되는 경향이 있다.이는 고객과 대학 고객 사이에 공유되는 소프트웨어가 거의 없었기 때문입니다.NSF가 일본의 제5세대 컴퓨터 시스템 프로젝트에 대응하여 슈퍼 컴퓨터 센터를 설립하기 전까지는 기후 및 기상 프로그램이 거의 예외였다.그때도 작은 암호는 공유되었다.

Cray가 홍보에 관심이 있었기 때문에 그들은 1983년과 1984년 북미 컴퓨터 체스 챔피언십뿐만 아니라 제4회(1983년)와 제5회(1986년) 세계 컴퓨터 체스 챔피언십에서 우승한 Cray Blitz의 개발을 지원했다.1970년대에 지배적이었던 체스라는 프로그램은 Control Data Corporation의 슈퍼컴퓨터에서 실행되었다.

박물관

Cray-1은 다음 장소에 전시되어 있습니다.

- 뉴멕시코 주 로스앨러모스에 있는 브래드베리 과학 박물관

- 위스콘신주 치페와 폴스에 있는 치페와 폴스 산업·기술 박물관

- 미네소타주 세인트 폴에 있는 크레이 플라자에 있는 크레이 회사 사무실

- 캘리포니아[16] 마운틴 뷰 컴퓨터 역사 박물관

- 미국 조지아주[17] 로즈웰, 컴퓨터 박물관

- 디지반 컴퓨터 박물관[18]

- 뮌헨의 독일 박물관

- ETH 취리히 - Eidgenössische Technische Hochschule 취리히(스위스)

- 가동 중인 컴퓨터: 워싱턴주[19] 시애틀에 있는 Museum + Labs

- 콜로라도 볼더[20] 국립대기연구센터

- 워싱턴 D.C.[21] 국립항공우주박물관

- 스위스 로잔의 볼로 박물관

- 블렛클리[22] 공원 국립컴퓨팅박물관

- 런던의[23] 과학 박물관

- 스웨덴[24] 스톡홀름에 있는 스웨덴 국립과학기술박물관

- 조지아주 로즈웰에 있는 미국 컴퓨터 박물관에는 4대의 Cray-1과 다른 Cray 컴퓨터가 있습니다.

Cray-1의 기타 이미지

Cray-1(EPFL에서 내부 노출 포함)

컴퓨터 역사 박물관의 Cray-1

컴퓨터 역사 박물관의 Cray-1

독일 박물관의 Cray-1

런던 과학 박물관의 크레이-1

미국 조지아주 로즈웰의 컴퓨터 박물관 Cray-1

레퍼런스

- ^ a b c d e f g Cray-1 컴퓨터 시스템 하드웨어 레퍼런스 매뉴얼 2240004, Rev C, 출판물: 1977년 11월 4일, Cray Research, Inc.

- ^ C.J. Murray, "최고의 팀 플레이어" 2008년 10월 28일 Wayback Machine Design News, 1995년 3월 6일 아카이브.

- ^ Swaine, Michael (October 5, 1981). "Tom Swift Meets the Big Boys: Small Firms Beware". InfoWorld. p. 45. Retrieved January 1, 2015.

- ^ "SCD Supercomputer Gallery". NCAR. Archived from the original on June 7, 2015. Retrieved June 3, 2010.

- ^ Budiansky, Stephen (2016). Code Warriors. New York: Alfred A. Knopf. pp. 298–300. ISBN 9780385352666.

- ^ Rahul Garg (June 2, 2013). "Exploring the Floating Point Performance of Modern ARM Processors". Anandtech.

- ^ "Apple A13 Bionic Specs".

- ^ Fairchild Semiconductor, "Fairchild 11C01 ECL Dual 5-4 Input OR/NOR Gate", Fairchild ECL Databook, 1972.

- ^ RM 러셀, "CRAY-1 컴퓨터 시스템" 통신사 ACM, 1978년 1월, 페이지 63-72.

- ^ "SCD Supercomputer Gallery: CRAY1-A". National Center for Atmospheric Research. Archived from the original on March 3, 2016. Retrieved January 30, 2016.

- ^ a b "The Cray-1 Computer System" (PDF). Cray Research Inc.

- ^ "Company History - Cray". Archived from the original on July 12, 2014.

- ^ J.S. Kolodzey, "CRAY-1 컴퓨터 테크놀로지", IEEE 트랜스. 부품, 하이브리드, 제조 기술, 제4권, 제3호, 1981년, 페이지 181–186.

- ^ "Cray Cuts Price". The New York Times. September 14, 1982.

- ^ Frontiers of Supercomputing II. Retrieved February 8, 2014.

- ^ Cray 1A. Computer History Museum. 1976. Retrieved May 15, 2012.

- ^ "Computer Museum of America - THE collection of computer artifacts". Computer Museum of America.

- ^ "Cray-1 Supercomputer (#38) and Memorabilia at the DigiBarn". DigiBarn Computer Museum. Retrieved May 15, 2012.

- ^ "Two Cray Supercomputers Join Living Computers". Archived from the original on April 26, 2019. Retrieved April 26, 2019.

- ^ "Cray 1". National Center for Atmospheric Research. Archived from the original on December 27, 2012. Retrieved May 15, 2012.

- ^ "National Air and Space Museum". Retrieved January 21, 2010.

This object is on display in the Beyond The Limits exhibition at the National Mall building.

- ^ "A Cray 1 Arrives". The National Museum of Computing. Archived from the original on March 4, 2014. Retrieved February 27, 2014.

- ^ "Cray 1A supercomputer, serial number 11, c 1979". NMSI. Retrieved May 15, 2012.

- ^ TM44354 Dator Cray Research, Inc. Cray Research, Inc. 1976 SAB Aerospace Archive 2011년 1월 6일 Wayback Machine, 페이지 52, Datorföremöl+pö+에서 보관TM.pdf. 2012년 5월 15일 취득.

외부 링크

- CRAY-1 컴퓨터 시스템 하드웨어 레퍼런스 매뉴얼, 간행물 No.2240004 Rev.C 11/77 (첫 3장)– DigiBarn / Ed Thelen에서

- CRAY-1 컴퓨터 시스템 하드웨어 레퍼런스 매뉴얼, 간행물 No. 2240004 Rev.C 11/77 (풀, 스캔, PDF)

- 온라인 Cray 매뉴얼 및 매뉴얼 수집 @ Bitsavers

- Cray Channels 매거진 @ 컴퓨터 역사 센터

- 컴퓨터 역사 센터에서의 Cray 매뉴얼 및 문서

- Cray Users Group 출판물 @ The Center for Computing History

- NCAR 슈퍼컴퓨터 갤러리

- Cray-1A CPU 로직의 정의 확인