크레파스-3

Cray-3크레이-3는 벡터 슈퍼컴퓨터였으며, 세이모어 크레이는 크레이-2의 후계자로 지명되었다.이 시스템은 1세제곱피트(0.028m3) CPU에 포장된 수백 개의 주문 제작 IC를 사용하여 컴퓨팅에서 갈륨 비소화(GaAs) 반도체를 최초로 적용한 주요 용도 중 하나였으며, 설계 목표는 크레용-2의 약 12배인 16 GFLOPS에 대한 성능이었다.

1988년 위스콘신 치페와 폭포에 있는 CRI(Crey Research)의 개발 연구소에서 크레파스-3에 대한 작업이 시작되었다.연구소의 다른 팀들은 비슷한 성능을 가진 디자인을 연구하고 있었다.그 팀들에 초점을 맞추기 위해, Cray-3의 노력은 그 해 말에 콜로라도 스프링스에 있는 새로운 연구소로 옮겨졌다.그 직후 미니애폴리스의 기업 본사는 또 다른 디자인인 Cray C90을 위해 Cray-3에 대한 작업을 끝내기로 결정했다.1989년 Cray-3의 노력은 CCC(Crey Computer Corporation)라는 새로 설립된 회사로 분리되었다.

론칭 고객인 Lawrence Livermore National Laboratory는 1991년 주문을 취소했고 그 직후 많은 회사 임원들이 떠났다.첫 번째 기계는 1993년에 마침내 준비되었지만, 발사 고객이 없어, 대신 인근 볼더에 있는 국립 대기 연구 센터에 시범 유닛으로 대여되었다.1995년 5월 회사가 파산했고, 기계는 공식적으로 해체되었다.

시모어 크레이는 첫 번째 크레이-3의 납품과 함께 즉시 유사하지만 개선된 크레이-4 설계로 넘어갔지만, 회사는 완전히 테스트되기 전에 파산했다.[1]크레이-3는 CCC가 파산하면서 SRC 컴퓨터를 만들어 병렬 설계에 집중했지만 1996년 이 작품이 전달되기 전 교통사고로 사망했다.[2]

역사

배경

시모어 크레이는 크레용-2가 생산에 이르자 1985년에 크레용-3의 디자인을 시작했다.[3]크레이는 일반적으로 이전 모델보다 10배 높은 성능으로 새로운 기계를 생산하겠다는 목표를 세웠다.기계들이 항상 이 목표를 달성한 것은 아니지만, 이것은 프로젝트를 정의하고 그것을 충족시키기 위해 어떤 종류의 프로세스 개선이 필요한지를 명확히 하는 데 유용한 기술이었다.[4]크레이-3의 경우 크레이-2보다 12배 높은 성능 향상 목표를 세우기로 했다.[5]

크레이는 항상 세 가지 동시 진전으로 속도가 빨라지는 문제를 공격했다. 즉, 시스템에 더 높은 병렬성을 부여하기 위한 실행 유닛의 증가, 신호 지연을 줄이기 위한 더 엄격한 포장, 더 높은 클럭 속도를 허용하기 위한 더 빠른 구성품이다.그 세 가지 중에서, 크레용은 보통 마지막에 가장 덜 공격적이었다; 그의 디자인은 최첨단 디자인과는 반대로 이미 널리 사용되고 있는 요소들을 사용하는 경향이 있었다.[4]

크레용-2에 대해서는 고밀도를 허용하기 위해 집적회로용 3D포장 시스템을 새로 도입했고,[6] 이 과정에서 어느 정도 개선의 여지가 있는 것으로 보였다.새로운 설계의 경우, 그는 모든 와이어가 최대 길이 1피트(0.30m)로 제한될 것이라고 말했다.이를 위해서는 프로세서가 약 1입방 피트(0.028 m3) 블록에 들어갈 수 있어야 한다.Cray-2 CPU의 ½ ½이것은 성능을 높일 뿐만 아니라 시스템을 27배 더 작게 만들 것이다.[7]

12배 성능 향상을 위해서는 포장만으로는 충분하지 않을 것이며 칩 자체의 회로도 속도를 높여야 할 것이다.크레용-2는 실리콘 기반 트랜지스터의 속도 제한을 4.1ns(244MHz)로 밀어붙이고 있는 것으로 보이며, 2배 이상의 속도도 가능할 것으로 보이지 않았다.12배라는 목표를 달성하려면 좀 더 급진적인 변화가 필요하며, "첨단 기술" 접근법을 사용해야 할 것이다.[8]

크레이는 갈륨 비소 회로를 크레용-2에 사용하려고 했는데, 갈륨 비소 회로를 사용하는 것은 훨씬 더 빠른 전환 속도를 제공할 뿐만 아니라 에너지를 덜 사용했기 때문에 더 시원하게 달릴 수 있었다.크레용-2가 설계되고 있을 당시 가아스 제조 상태는 단순히 슈퍼컴퓨터 공급의 임무를 감당하지 못하고 있었다.[9]1980년대 중반에 이르러 상황은 달라졌고 크레용은 그것이 앞으로 나아갈 유일한 길이라고 결정했다.[10]크레이는 대형 칩 제조사 쪽에 대한 투자 부족을 감안해 가아스 칩 제조 스타트업인 기가비트 로직(GigaBit Logic)에 투자해 내부 공급사로 활용하기로 했다.[11]

크레이는 1988년 11월 이 시스템을 설명하면서 12배 성능 증가는 GaAs 회로로 인해 3배, 프로세서를 더 많이 사용하게 되어 4배가 증가하게 될 것이라고 밝혔다.Cray-2의 문제점 중 하나는 프로세서 간 대역폭이 제한되어 있어 멀티프로세싱 성능이 떨어지는 것으로, 이를 해결하기 위해 Cray-3는 Cray Y-MP에서 사용되는 훨씬 빠른 아키텍처를 채택할 것이다. 이는 8000 MIPS 즉 16 GFLOPS의 설계 성능을 제공할 것이다.[7]

개발

크레이-3는 원래 1991년에 인도될 예정이었다.[12]이는 슈퍼컴퓨터 시장이 1980년 연간 50% 성장에서 1988년 10% 성장으로 급속히 위축되던 시기였다.[10]동시에 크레이 리서치는 원래의 크레이-1까지 그것의 조상을 추적하는 시스템 아키텍처의 더 빠른 다중 프로세서 버전인 Y-MP에 대해서도 연구하고 있었다.Y-MP와 Cray-3 그룹에 초점을 맞추기 위해, 그리고 Cray의 개인적인 지원으로 Cray-3 프로젝트는 콜로라도 스프링스의 새로운 연구 센터로 옮겨갔다.[13][3]

1989년까지 Y-MP는 배달을 시작하고 있었고, 위스콘신 치페와 폭포의 주요 CRI 연구소는 C90으로 옮겨갔으며, 이는 Y-MP 시리즈가 더욱 개선되었다.[14][15]크레용-2가 25대밖에 팔리지 않은 상황에서 경영진은 크레용-3를 '낮은 우선순위' 개발에 나서야 한다고 결정했다.1988년 11월 콜로라도 스프링스 연구소는 CCC(Cray Computer Corporation)로 분리되었고, CRI는 신규 회사 주식의 10%를 보유했으며, 개발 자금으로 8500만 달러의 약속 어음을 제공했다.[3]크레이 자신은 새 회사의 주주가 아니었고, 계약직으로 일했다.[16][17]CRI가 원건물에 대한 임대차 계약을 유지하면서 신규 업체는 다시 한 번 이사를 해야 해 추가 지연이 발생했다.[3][6]

1991년까지 개발은 예정보다 늦어졌다.[18]Lawrence Livermore National Laboratory가 C90에 유리하게 [19]첫 번째 기계에 대한 주문을 취소했을 때 개발은 더욱 둔화되었다.대표이사를 포함한 여러 임원이 회사를 떠났다.[16]그 후, 그 회사는 4~8개의 프로세서를 가진 더 작은 버전의 기계가 필요한 고객을 찾을 것이라고 발표했다.[20]

최초의 (그리고 유일한) 생산 모델(시리얼 번호 S5, 그레이울프라는 이름)은 1993년 5월에 시범 시스템으로 NCAR에 대여되었다.NCAR의 버전은 4개의 프로세서와 128 MWord(64비트 워드, 1GB)의 공통 메모리로 구성되었다.[21]서비스에서 정적 램은 문제가 있는 것으로 판명되었다.또한 제곱근 코드에 버그가 포함되어 있어 1백만 번의 계산이 틀리는 결과를 초래한 것으로 밝혀졌다.게다가, 네 개의 CPU 중 한 개는 신뢰성 있게 실행되지 않고 있었다.[22]

CCC는 약 3억 달러의 자금을 지출한 후 1995년 3월에 파산선고를 했다.NCAR의 기계는 다음 날 공식적으로 해체되었다.[23]7개의 시스템 캐비닛, 즉 "탱크" 즉, 일련번호 S1에서 S7까지가 Cray-3 기계를 위해 지어졌다.대부분은 소형 2CPU 기계를 위한 것이었다.크레파스-4 프로젝트에 세 개의 작은 탱크가 사용되었는데,[24] 기본적으로 크레파스-3는 1ns(1GHz)에서 64개의 더 빠른 CPU를 가동하고 더 작은 공간에 포장을 했다.[25]또 다른 것은 크레파스-3/SSS 프로젝트에 사용되었다.[26]

크레파스 3호의 실패는 정치적, 기술적 풍토가 변화한 탓이 컸다.이 기계는 바르샤바 협정이 붕괴되고 냉전이 종식되는 동안 설계되어 슈퍼컴퓨터 구매가 대폭 축소되었다.[20][27]동시에, 시장에서는 대규모 병렬(MP 또는 MPP) 설계에 대한 투자가 증가하고 있었다.크레이는 이 접근방식에 비판적이었으며 월스트리트저널은 MPP 시스템이 벡터 컴퓨터에 대한 우월성을 아직 입증하지 못했다고 보도하면서 많은 사용자들이 대형 병렬 기계에 대한 프로그래밍을 해왔던 어려움을 지적했다."나는 그들이 적어도 내 생전에 성공하지는 못할 것이라고 생각한다."[27]

건축

논리설계

Cray-3 시스템 아키텍처는 전경 처리 시스템, 최대 16개의 백그라운드 프로세서와 최대 2기가와드(16GB)의 공통 메모리를 구성했다.전방 시스템은 입출력 및 시스템 관리 전용이었다.여기에는 주로 HiPPI 채널을 통해 대용량 스토리지 및 네트워크 장치를 위한 32비트 프로세서와 4개의 동기식 데이터 채널이 포함되었다.[28]

각 백그라운드 프로세서는 계산 섹션, 제어 섹션 및 로컬 메모리로 구성되었다.계산 섹션은 64비트 스칼라, 부동 소수점, 벡터 산술을 수행했다.제어 섹션은 명령 버퍼, 메모리 관리 기능, 실시간 클럭을 제공했다.임시 스크래치 메모리로 사용하기 위해 각 백그라운드 프로세서에 고속 로컬 메모리의 16kbytes를 통합했다.[29]

공통 메모리는 실리콘 CMOS SRAM으로 구성되었으며, 각각 64개 은행의 옥탄트로 구성되었으며, 최대 8개의 옥탄트가 가능하다.단어 크기는 64비트 + 8개의 오류 수정 비트였으며, 총 메모리 대역폭은 초당 128 기가바이트의 정격을 받았다.[30]

CPU 설계

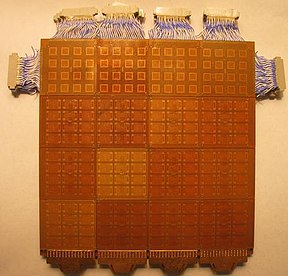

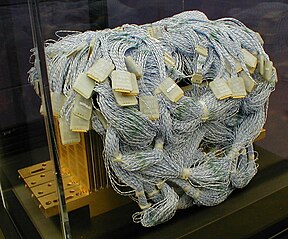

이전의 설계와 마찬가지로, Cray-3의 코어는 여러 개의 모듈로 구성되었으며, 각 모듈에는 부품으로 채워진 여러 개의 회로 기판이 포함되어 있다.밀도를 높이기 위해 개별 GaAs 칩을 포장하지 않고, 그 대신 여러 개를 약 1인치(25mm) 정사각형 모양의 보드에 초음파 금 본딩으로 직접 장착했다.그런 다음 보드를 뒤집어서 전기 배선을 운반하는 두 번째 보드에 연결했고, 이 카드의 와이어는 본딩된 칩 캐리어의 "하단"(칩 반대쪽) 쪽으로 구멍을 통해 연결되며, 따라서 두 보드의 층 사이에 칩이 샌드위치된다.그리고 나서 이 하위조종들은 Cray-2에서와 같이, 3D 회로를 만들기 위해 서로 연결되었다.[21]

크레이-2와는 달리 크레이-3 모듈에도 에지 커넥터가 포함됐다.그러한 16개의 하위 모듈을 4×4배열로 연결하여 121 X 107 X 7 밀리미터의 단일 모듈(× 0.28인치 4.76 in × 4.21 in)을 만들었다.이 진보된 포장에도 불구하고 회로 밀도는 1990년대 기준에도 불구하고 세제곱인치당 약 96,000 게이트로 낮았다.[31]현대의 CPU는 1평방인치당 수백만 개의 게이트 수를 제공하며, 3D 회로로의 이동은 2017년[update] 현재에도 여전히 고려되고 있다.[32]

그런 모듈 32개를 한 개의 프로세서에 꼬인 쌍선 덩어리와 함께 쌓고 배선했다.기본 사이클 타임은 2.11ns, 즉 474MHz로 각 프로세서가 약 0.948 GFLOPS에 도달할 수 있도록 했고, 16개 프로세서 머신은 이론적으로 15.17 GFLOP. 고성능의 핵심은 메인 메모리에 대한 고속 접근으로 각 프로세스가 최대 8 GB/s까지 폭발할 수 있도록 했다.[33]

기계 설계

이 모듈들은 "브릭"이라고 알려진 알루미늄 섀시에 함께 고정되었다.이 벽돌들은 Cray-2에서와 같이 식히기 위해 액체 불소에 담갔다.64개의 메모리 모듈을 갖춘 4-프로세서 시스템은 약 88kW의 전력을 소모했다.[21]전체 4개 프로세서 시스템의 높이는 약 20인치(510mm)로 앞뒤로, 폭은 약 2피트(0.61m)가 넘는다.[34]

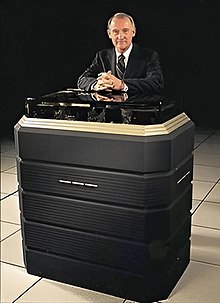

최대 4개의 프로세서가 장착된 시스템의 경우 프로세서 어셈블리는 폭이 42인치(1.1m)이고 깊이 28인치(0.71m) 및 높이 50인치(1.3m)인 캐비닛 상단에 있는 반투명 동상 아크릴 커버 아래에 앉아 있었고,[34] 그 아래에 메모리가 있는 다음 전원 공급기와 냉각 시스템이 아래에 있었다.여덟 개와 열여섯 개의 프로세서가 더 큰 팔각형 캐비닛에 들어 있었을 것이다.전체적으로 Cray-3는 Cray-2에 비해 상당히 작았고, 그 자체도 다른 슈퍼컴퓨터에 비해 상대적으로 작았다.[34]

시스템 캐비닛 외에도 Cray-3 시스템은 전력 및 냉각 제어 장비가 포함된 시스템 제어 포드(또는 "C-Pods"), 52.5인치(1.33m) 정사각형 및 55.3인치(1.40m)[34] 높이의 하나 또는 두 개의 (프로세서 수에 따라 다름) 시스템 제어 장치도 필요했다.

시스템 구성

다음과 같은 가능한 Cray-3 구성이 공식적으로 지정되었다.[35]

| 이름 | CPU | 메모리(Mwords) | I/O 모듈 |

|---|---|---|---|

| 크레용-3/1-256 | 1 | 256 | 1 |

| 크레파스-3/2-256 | 2 | 256 | 1 |

| 크레파스-3/4-512 | 4 | 512 | 3 |

| 크레용-3/4-1024 | 4 | 1024 | 3 |

| 크레파스-3/4-2048 | 4 | 2048 | 3 |

| 크레용-3/8-1024 | 8 | 1024 | 7 |

| 크레용-3/8-2048 | 8 | 2048 | 7 |

| 크레용-3/16-2048 | 16 | 2048 | 15 |

소프트웨어

크레용-3는 크레용 리서치의 유니코스 운영체제 버전 5.0을 기반으로 한 콜로라도 스프링스 운영체제(CSOS)를 운영했다.CSOS와 UNICOS의 주요한 차이점은 CSOS가 UNICOS에서 사용된 모든 PCC 확장자를 제거하고 표준 C에 포팅되었다는 것이다.[36]

Cray-3에 따라 이용할 수 있는 많은 소프트웨어는 Cray Research에서 파생되었으며, 예를 들어 FORTRAN과 C 컴파일러, NFS 및 TCP/IP 스택을 벡터화하는 X 윈도우 시스템을 포함하고 있다.[37][36]

참조

인용구

- ^ "CCC 1994 Annual Report".

- ^ "Obituary – Seymour Cray, Father of supercomputing". Archived from the original on 2008-05-07.

- ^ a b c d 2012년 245페이지.

- ^ a b 맥켄지 1998, 페이지 141.

- ^ 맥켄지 1998, 페이지 153.

- ^ a b 판독치 2000, 페이지 10.

- ^ a b Trew 2012, 페이지 246.

- ^ 맥켄지 1998, 페이지 153–154.

- ^ 판독치 2000, 페이지 9.

- ^ a b 맥켄지 1998, 페이지 154.

- ^ Peltz, James (23 January 1990). "GigaBit Logic Negotiating Sale With Cray Computers". Los Angeles Times.

- ^ "CRAY COMPUTER CORPORATION, Form 8-K, Current Report, Filing Date Mar 26, 1996". secdatabase.com. Retrieved May 14, 2018.

- ^ 머레이 1997, 페이지 195.

- ^ Trew 2012, 페이지 243.

- ^ 맥켄지 1998, 페이지 154–155.

- ^ a b "Chief Executive Quits At Cray Computer". The New York Times. 17 April 1992.

- ^ 머레이 1997, 페이지 190.

- ^ "Cray Computer Is Behind Schedule". The New York Times. 17 December 1991.

- ^ "Cray Loses Only Order For Product". The New York Times. 24 December 1991.

- ^ a b "Cold War's End Hits Cray Computer". The New York Times. 21 February 1992.

- ^ a b c 1993년 레스터

- ^ Anthes, Gary (1 August 1994). "Research lab sizes up slew of supercomputers". Computerworld. p. 55.

- ^ "CRAY-3 (graywolf): 1993–1995". SCD Supercomputer Gallery. Archived from the original on 2016-10-10. Retrieved 2016-10-20.

- ^ "Seymore R. Cray". Computerworld. 18 July 1994. p. 20.

- ^ Stedman, Craig (3 April 1995). "Cray Computer ends its quest". Computerworld. p. 32.

- ^ Wobst, Reinhard (2007). Cryptology Unlocked. John Wiley & Sons. p. 150. ISBN 9780470060643.

- ^ a b Allen, Michael (1998). "Pushing Big Iron: Seymour Cray's Woes Reflect Tough Times for Supercomputers". Wall StreetJournal. Archived from the original on 17 March 2012.

- ^ 브로셔 1993, 페이지 6

- ^ 브로셔 1993, 페이지 4

- ^ 1993 페이지 5의 브로셔

- ^ 브로셔 1993, 페이지 8.

- ^ Newman, Jared (5 May 2011). "Intel's 3D Transistor: Why It Matters". PCWorld.

- ^ van der Steen, Aad (14 November 1995). "Short Description of Architectures in the TOP500: The Cray Computer Corporation Cray-3". TOP500. Archived from the original on 28 March 2012.

- ^ a b c d 브로셔 1993, 페이지 15.

- ^ 브로셔 1993, 페이지 10.

- ^ a b CRAY-3 Software Introduction Manual (PDF). Cray Computer Corporation. 1991.

- ^ 브로셔 1993, 페이지 14.

참고 문헌 목록

- CRAY-3 Supercomputer Systems (PDF) (brochure). Cray Computer Corporation. 1993.

- Hill et all, Mark Donald (2000). Readings in computer architecture. Gulf Professional Publishing. ISBN 9781558605398.

- Lester, Lynda (June 1993). "The making of a CRAY-3". Ninth SCD User Conference. Archived from the original on 30 June 2007.

- MacKenzie, Donald (1998). Knowing machines: essays on technical change. MIT Press. ISBN 9780262631884.

- Murray, Charles (1997). The Supermen: the story of Seymour Cray and the technical wizards behind the supercomputer. John Wiley. ISBN 9780471048855.

- Trew, Arthur (2012). "Vector Supercomputers: It's Never too Late to Parallelise". In Trew, Arthur; Wilson, Greg (eds.). Past, Present, Parallel: A Survey of Available Parallel Computer Systems. Springer Science & Business. p. 245. ISBN 9781447118428.