CDC 6600

CDC 6600| CDC 6600 | |

|---|---|

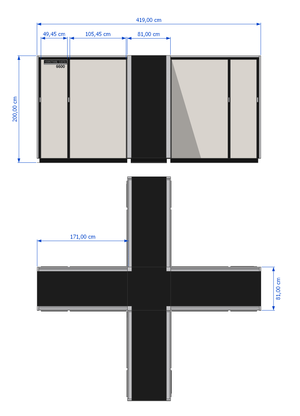

그림을 축척으로 하는 3D 렌더링 | |

| 설계. | |

| 제조원 | 컨트롤 데이터 코퍼레이션 |

| 디자이너 | 시모어 크레이 |

| 발매일 | 1964년 9월[1] |

| 판매대수 | 100+ |

| 가격. | 2,370,000달러[2](2021년 2,0,710,000달러 상당) |

| 케이스 | |

| 치수 | 높이: 2,000mm(79인치) 캐비닛 폭: 810mm(32인치)[3] 캐비닛 길이: 1,710 mm (67 인치)[3] 전폭: 4,190mm(165인치)[3] |

| 체중 | 약 12,000파운드(6.0 쇼트톤, 5.4t)[4] |

| 힘 | 30 kW (208 V 400[5][2] Hz시) |

| 시스템. | |

| 운영 체제 | 스코프, KRONOS[6] |

| CPU | 60비트 프로세서(10MHz시[7]) |

| 기억 | 최대 982 킬로바이트 (131000 x 60비트)[1] |

| MIPS | 2 MIPS[7] |

| 전임자 | CDC 1604 |

| 후계자 | CDC 7600 |

CDC 6600은 Control Data [8][9]Corporation이 제조한 6000 시리즈 메인프레임 컴퓨터 시스템의 플래그십이었습니다.일반적으로 최초의 성공적인 슈퍼컴퓨터로 간주되는 이 제품은 업계의 이전 기록 보유자인 IBM 7030 Stretch보다 [10][11]3배 더 높은 성능을 보였습니다.최대 3메가 FLOPS의 성능을 갖춘 CDC [12][13]6600은 1964년부터 1969년까지 세계에서 가장 빠른 컴퓨터였으며, 이후 CDC 7600에 [14]그 지위를 양도했습니다.

최초의 CDC 6600은 1965년에 리버모어와 로스앨러모스에 [15]납품되었습니다.Courant Institute of Mathematical Sciences, [16][17]CERN, Lawrence Radiation [18]Laboratory 및 기타 많은 기관에 시스템이 제공되면서 하이엔드 과학 및 수학 컴퓨팅의 필수 시스템이 되었습니다.총 [19]100개 이상이 배달되었습니다.

CDC 6600은 캘리포니아 마운틴 뷰의 컴퓨터 역사 박물관에 전시되어 있습니다.실행 중인 유일한 CDC 6000 시리즈 머신이 Living Computers에 의해 복원되었습니다. Museum + Labs.

역사와 영향

CDC의 첫 번째 제품은 ERA에서 설계된 머신에 기반을 두고 있으며, Seymour Cray는 CDC로 옮긴 후 업데이트를 요청받았습니다.리틀 [20]캐릭터로 알려진 실험적인 기계 이후, 1960년에 그들은 최초의 상업용 트랜지스터 기반 컴퓨터 중 하나이자 시장에서 가장 빠른 기계 중 하나인 CDC 1604를 출시했다.경영진은 매우 기뻐하며 비즈니스 용도에 맞는 새로운 시리즈 머신의 계획을 세웠습니다.예를 들어, 캐릭터 처리나 기록 보관에 관한 지시 등이 포함됩니다.크레이는 그런 프로젝트에 관심이 없었고 1604보다 50배 더 빠른 새로운 기계를 만들겠다는 목표를 세웠다.향후 1년, 5년 후의 계획에 대한 상세한 보고서를 작성하도록 요구받았을[when?] 때, 그는 5년간의 목표는 "세계에서 가장 큰 컴퓨터를 생산하는 것"이었고, 그 당시 "가장 빠른 것"과 동의어인 "가장 큰 것"이었으며, 1년간의 계획은 "5분의 1이 되는 것"이라고 답했다.

그의 핵심 팀을 원래의 CDC 본사 근처에 있는 새로운 사무실로 데리고 가서, 그들은 크레이가 1604년에 [when?]사용했던 "싼" 트랜지스터의 고품질 버전을 실험하기 시작했다.많은 실험 후에, 그들은 게르마늄 기반의 트랜지스터가 1604년에 사용된 것보다 훨씬 더 빨리 실행될 수 있는 방법이 없다는 것을 발견했다.경영진이 당초 원하던 「비즈니스 머신」이, 현재는 CDC 3000 시리즈로 형성되고 있기 때문에, 경영진은 최대한의 노력을 기울일 수 있었습니다.그 후 Cray는 당시 Fairchild Semiconductor의 새로운 실리콘 기반 트랜지스터와 함께 작업하는 것이 해결책이라고 판단했습니다.이 트랜지스터는 시장에 막 출시되어 스위칭 성능이 극적으로 향상되었습니다.

이 기간 동안 CDC는 신생기업에서 대기업으로 성장했고 Cray는 터무니없는 관리 요건에 점점 더 불만을 품게 되었습니다.1962년 새로운 CDC 3600이 생산 품질에 근접하기 시작하면서 상황은 상당히 긴박해졌고 경영진이 원하는 대로 이루어졌습니다.Cray는 결국 CDC의 CEO인 William Norris에게 무언가 변화가 없으면 회사를 떠날 것이라고 말했다.노리스는 자신이 너무 중요해서 잃을 수 없다고 느꼈고 크레이가 원하는 곳에 새로운 실험실을 세울 수 있도록 허락했다.

짧은 수색 후에, 크레이는 그의 고향인 위스콘신주 치페와 폴스로 돌아가기로 결심했고, 그곳에서 그는 한 블록의 땅을 구입하고 새로운 [when?]실험실을 시작했다.

이 과정으로 인해 그의 새 기계 설계가 상당히 오래 지연되었지만, 일단 새로운 실험실에 들어오면 경영진의 간섭 없이 일이 빠르게 진행되기 시작했습니다.이때까지, 새로운 트랜지스터는 매우 신뢰성이 높아졌고, 이 트랜지스터로 만들어진 모듈은 한 번에 제대로 작동하는 경향이 있었습니다.6600은 시스템 설계자이자 6600의 "숨겨진 천재"인 Jim Thornton과 함께 Cray가 작업하면서 형태를 갖추기 시작했습니다.

CDC 6600은 기계 수명 [when?]동안 100대 이상 판매되었습니다.이들 중 상당수는 다양한 핵무기 관련 연구소에 갔고 상당수는 대학 컴퓨터 연구소에 들어갔다.Cray는 즉시 CDC 7600으로 제공되는 6600의 10배에 달하는 성능을 목표로 그 교체에 관심을 기울였습니다.최신 CDC Cyber 70 및 170 컴퓨터는 전체[when?] 설계에서 CDC 6600과 매우 유사하며 거의 역호환성이 있었습니다.

6600은 이전 기록 보유자인 IBM 7030 Stretch보다 3배 더 빨랐습니다. IBM은 이에 놀라움을 금치 못했습니다.당시 CEO였던 Thomas Watson Jr.는 직원들에게 [when?]다음과 같은 메모를 남겼습니다. "지난 주에 Control Data가 6600 시스템을 발표했습니다.시스템을 개발하는 연구실에는 관리인을 포함해 34명밖에 없는 것으로 알고 있습니다.이 중 14명은 엔지니어, 4명은 프로그래머...이 정도의 노력과 우리의 방대한 개발 활동을 비교해보면, 왜 우리가 세계에서 가장 강력한 컴퓨터를 다른 사람에게 제공하게 함으로써 업계 선두 자리를 잃었는지 이해할 수 없습니다."크레이의 대답은 냉소적이었다. "왓슨 씨가 자신의 [21][22]질문에 답한 것 같다."

묘사

당시의[when?] 일반적인 기계들은 시스템 [23]전체를 구동하기 위해 하나의 중앙 처리 장치(CPU)를 사용했습니다.일반적인 프로그램에서는 먼저 데이터를 메모리에 로드하고(종종 사전 롤된 라이브러리 코드를 사용하여), 처리한 후 다시 씁니다.따라서 CPU가 호출되는 모든 명령을 처리하기 위해서는 CPU가 상당히 복잡해야 했습니다.CPU가 복잡하면 CPU가 커지기 때문에 각각의 모듈 간에 정보가 흐르는 동안 시그널링 지연이 발생합니다.기계는 신호 시간이 다음 모듈에 도달하는 주기 속도로만 작동할 수 있기 때문에 이러한 지연은 성능의 최대 상한을 설정합니다.

크레이는 다른 방법을 택했다.그 [when?]시점에서는, CPU는 통상, 접속되어 있는 메인 메모리보다 동작이 느렸습니다.예를 들어 프로세서가 두 숫자를 곱하는 데 15주기가 걸리는 반면 각 메모리 액세스에는 1~2주기가 걸립니다.이는 메인 메모리가 유휴 상태였던 상당한 시간이 있었다는 것을 의미합니다.6600이 착취한 것은 이 유휴시간이었다.

CDC 6600에서는 가능한 한 신속하게 수학 및 논리 연산을 실행할 수 있도록 설계된 심플화된 중앙 프로세서(CP)를 사용했습니다.이것에 의해, 배선 길이와 관련되는 시그널링 지연을 줄이기 위해서, 가능한 한 작게 구축할 필요가 있습니다.그 결과 CPU용 회로기판이 중앙 가까이에 배치된 기계의 (일반적으로) 십자형 메인섀시가 되어 CPU가 훨씬 작아졌습니다.실리콘 트랜지스터의 고속 스위칭 속도와 조합하여 새로운 CPU는 시판되고 있는 다른 기계보다 약 10배 빠른 10MHz(100ns 사이클 타임)로 동작했습니다.심플한 프로세서는 클럭 사이클이 빠를 뿐만 아니라 명령어를 적은 클럭 사이클로 실행했습니다.예를 들어 CPU는 10 사이클로 곱셈을 완료할 수 있었습니다.

CPU를 지원하는 것은 12비트 4KiB 페리페럴 프로세서(PP) 10개입니다.각각 12개의 입출력(I/O) 채널의 공통 풀에 액세스 할 수 있어 입력과 출력을 처리할 수 있을 뿐만 아니라 CP가 처리하기 위해 중앙 메모리에 송신하는 데이터를 제어합니다.PP는 CPU가 작업을 수행하는 동안 메모리에 액세스하도록 설계되었습니다.이것에 의해, 중앙 처리 시간의 관점에서 입출력을 기본적으로 무료로 실시할 수 있게 되어, CPU는 가능한 한 비지 상태가 됩니다.

6600의 CP는 60비트 워드와 1의 정수 보완 표현을 사용했는데, 이는 이후 CDC 기계가 1980년대 후반까지 사용되기 때문에 일부 디지털 신호 프로세서를 제외하고 이 [24]아키텍처를 사용하는 마지막 시스템이 되었습니다.

나중에 [when?]CDC는 CP, PP 및 채널의 수와 유형에 대한 옵션을 제공했습니다. 예를 들어 CDC 6700은 6400 CP와 6600 CP를 가지고 있습니다.

주변기기 프로세서

CPU는 한정된 수의 간단한 명령만 실행할 수 있었습니다.그 시대의 일반적인 CPU에는 메모리 액세스나 입출력 등 일반적인 "하우스키핑" 작업을 모두 처리하는 복잡한 명령 세트가 있었습니다.대신 Cray는 이러한 명령어를 이들 태스크 전용의 개별적이고 심플한 프로세서로 구현하여 CPU에 훨씬 작은 명령어 세트를 남겨두었습니다.이것은 후에 RISC(Reduced Instruction Set Computer) 설계라고 불리는 최초의 것이었다[when?].

CPU, 주변 프로세서(PP) 및 I/O가 병렬로 동작하도록 함으로써 기계의 성능을 크게 향상시켰습니다.통상적인 상황에서는 프로세서가 여러 개 있는 기계도 비용이 많이 듭니다.6600 설계의 핵심은 페리페럴 프로세서(PP)라고 불리는 I/O 프로세서를 최대한 심플하게 만드는 것이었습니다.PP는 CPU보다 훨씬 느리게 실행되는 단순한 12비트 CDC 160-A를 기반으로 데이터를 수집하여 전용 하드웨어를 통해 고속으로 메인 메모리에 버스트 형태로 전송합니다.

10개의 PP는 가상으로 구현되었으며, 단일 [25]: pp.4-3 thru 4-4 PP에만 CPU 하드웨어가 있었습니다.이 CPU 하드웨어는 10개의 PP 상태를 각각 나타내는 10개의 PP 레지스터 세트로 공유되어 작동되었습니다(현대 멀티스레딩 프로세서와 유사).PP 레지스터 배럴은 실제 PP CPU가 점유한 "슬롯"에 각 PP 레지스터 세트를 제시하면서 "회전"합니다.공유 CPU는 PP 명령의 전부 또는 일부를 실행하며, 이에 따라 배럴이 다시 "회전"하여 다음 PP의 레지스터 세트(상태)를 표시합니다.명령을 완료하려면 배럴의 "회전"이 여러 번 필요했습니다.1000나노초(PP당 100나노초) 만에 완전한 배럴의 "회전"이 발생했으며, 명령을 완료하려면 배럴의 "회전"이 1~5회, 데이터 전송 명령일 경우 더 걸릴 수 있습니다.

명령 집합 아키텍처

6600 CPU의 기본은 나중에 RISC 시스템이라고 불리게 되는 것입니다.이 시스템에서는 프로세서가 비교적 심플하고 메모리에 대한 접근이 제한적이고 명확하게 정의되어 있는 명령을 실행하도록 조정되어 있습니다.다른 많은 기계들의 철학은 복잡한 명령어를 사용하는 것이었습니다. 예를 들어, 하나의 명령어로 메모리에서 오퍼랜드를 가져와 레지스터의 값에 추가하는 것입니다.6600 에서는, 메모리로부터 값을 로드하려면 , 1개의 순서가 필요합니다.그 값을 추가하려면 , 2번째 순서가 필요합니다.추가 메모리 액세스로 인해 이론적으로는 느리지만, 잘 예약된 코드에서는 여러 명령이 병렬로 처리될 수 있다는 사실이 이 비용을 낮췄습니다.이러한 단순화로 인해 프로그래머들은 메모리 액세스를 매우 의식하게 되었고, 따라서 가능한 [citation needed][dubious ]한 메모리 액세스를 줄이기 위해 의도적으로 코드를 작성하게 되었습니다.

모델

CDC 6000 시리즈에는 CDC 6400, CDC 6500, CDC 6600 및 CDC 6700의 [when?]4가지 기본 모델이 포함되어 있습니다.6000 시리즈의 모델은 6400 CPU와 6600 CPU의 2종류의 CPU에서만 차이가 있었습니다.6400 CPU에는 개별 기능 유닛이 아닌 통합 연산 유닛이 탑재되어 있었습니다.따라서 명령 실행 시간을 겹칠 수 없습니다.예를 들어 6400 CPU에서는 add 명령이 multiply 명령 뒤에 바로 있으면 multiply 명령이 완료될 때까지 add 명령을 시작할 수 없기 때문에 두 명령의 순 실행 시간은 각각의 개별 실행 시간의 합이 됩니다.6600 CPU는 동시에 동작할 수 있는 복수의 기능 유닛을 갖추고 있어 명령어 실행 시간을 중복시킬 수 있습니다.예를 들어, 6600 CPU는 다중 명령의 시작 후에 다음 CPU 사이클에서 추가 명령 실행을 시작할 수 있습니다(물론 다중 명령의 결과가 추가 명령의 피연산자가 아니라고 가정함). 따라서 두 명령의 순 실행 시간은 단순히 m의 (더 긴) 실행 시간이 됩니다.궁극의 지시또한 6600 CPU에는 명령 캐시의 일종인 명령 스택이 있어 메모리가 명령 가져오기 요구에 응답할 때까지 기다리는 CPU 유휴 시간을 줄임으로써 CPU 스루풋을 높이는 데 도움이 되었습니다.두 종류의 CPU는 명령어 호환성이 있기 때문에 어떤 종류의 CPU에서도 실행되는 프로그램은 다른 종류의 CPU에서도 동일하게 동작하지만 6600 CPU에서는 더 빠르게 동작합니다.실제로 6000 시리즈의 모든 모델은 완전히 상호 호환성이 있습니다.CDC 6400에는 CPU가 1개(6400 CPU), CDC 6500에는 CPU가 2개(모두 6400 CPU), CDC 6600에는 CPU가 1개, CDC 6700에는 CPU가 2개(6600 CPU와 6400 CPU)가 있습니다.

중앙 프로세서(CP)

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

6400, 6500 및 6600 머신의 Central Processor(CP)와 메인 메모리는 60비트 워드 길이였습니다.센트럴 프로세서는 8개의 범용 60비트 레지스터 X0~X7, 8개의 18비트 주소 레지스터 A0~A7, 8개의 18비트 "증분" 레지스터 B0~B7을 가지고 있었습니다.B0은 하드웨어에 의해 영속적으로 0으로 유지되었습니다.많은 프로그래머들이 B1을 1로 설정하고 마찬가지로 그것을 신성불가침으로 취급하는 것이 유용하다는 것을 알았다.

CP에는 입력과 출력에 대한 지시가 없었습니다.이 지시는 Peripheral Processor(아래)를 통해 이루어집니다.메모리 로드 또는 저장 전용의 opcode는 없었습니다.이것은 특정 A 레지스터에 할당되었을 때의 부작용입니다.A1에서 A5를 설정하면 해당 주소의 워드가 각각 X1에서 X5로 로드되고, A6 또는 A7을 설정하면 X6 또는 X7에서 워드가 저장됩니다.A0과 관련된 부작용은 없었다.스턴트 박스라고 불리는 별도의 하드웨어 로드/스토어 유닛은 실제 데이터 이동을 명령 스트림의 작동과 독립적으로 처리하여 메모리에 액세스하는 동안 다른 작업을 완료할 수 있으며, 이 작업은 최적의 경우 8주기가 필요했습니다.

6600 CP에는 10개의 병렬 기능 장치가 포함되어 있어 동시에 여러 명령을 수행할 수 있습니다.오늘날 [timeframe?]이것은 슈퍼스칼라 프로세서 설계로 알려져 있지만 당시에는 독특했습니다.대부분의 최신 CPU 설계와는 달리 기능 유닛은 파이프라인으로 연결되어 있지 않았습니다.지시가 발행되면 기능 유닛은 비지 상태가 되어, 그 명령을 실행하는 데 필요한 모든 시간 동안 비지 상태가 됩니다.(반면 CDC 7600에서는 기능 유닛에 파이프 라이닝이 도입되었습니다).최선의 경우 100ns 클럭사이클마다 기능 유닛에 명령을 발행할 수 있습니다.시스템은 메모리에서 명령을 가능한 한 빨리 읽고 디코딩했으며, 일반적으로 명령어를 완료할 수 있는 속도보다 더 빨랐으며, 처리를 위해 장치에 전달했습니다.단위는 다음과 같습니다.

- 부동 소수점 배수(2부)

- 부동 소수점 분할

- 부동 소수점 가산

- "긴" 정수 덧셈

- 인크리먼트(2개의 복사본, 메모리 로드/스토어 실행)

- 교대하다

- 부울 논리

- 분점

이 아키텍처에서는 부동소수점 연산이 가장 중요한 역할을 했습니다.CDC 6600(및 kin)은 프로그램 브랜치에 버금가는 시간에 60비트의 부동소수점 곱셈을 실행할 수 있는 사실상 단독입니다.James Thornton의 저서 "Design of a Computer"의 Mitch Alsup의 최근 분석에 따르면 6600의 부동 소수점 유닛은 2단계 파이프라인 설계입니다.

60비트 숫자의 고정 소수점 덧셈과 뺄셈은 Long Add Unit에서 처리되었으며 음수에 대한 1개의 보수를 사용했습니다.고정 소수점 곱셈은 부동 소수점 곱셈 단위로 특별한 경우로 수행되었습니다.지수가 0일 경우 FP 유닛은 단정도 48비트 부동 소수점 곱셈을 수행하고 상위 지수 부분을 클리어하여 48비트 정수 결과를 얻습니다.정수 나눗셈은 매크로에 의해 수행되며 부동 [26]소수점 간에 변환됩니다.

이전에 실행된 명령은 "스택"이라고 불리는 8단어 캐시에 저장되었습니다.메모리를 가져올 필요가 없었기 때문에 스택 내 점프보다 스택 내 점프 속도가 빨랐습니다.스택은 무조건 점프 명령에 의해 플러시되었으므로, 루프 끝의 무조건 점프는 항상 성공하는 조건부 점프로 기록되었다.

시스템은 10MHz 클럭과 4상 신호를 사용했습니다.부동소수점 곱셈에는 10 사이클, 나눗셈에는 29 사이클이 소요되었으며 메모리 지연 및 기타 문제를 고려한 전체 성능은 약 3 MFLOPS였습니다.FORTRAN 프로그램은 머신 역사 후반기에 이용 가능한 최고의 컴파일러를 사용하여 약 0.5메가플롭스를 유지할 것으로 예상됩니다.

메모리 구성

사용자 프로그램은 메인 메모리의 인접 영역만 사용하도록 제한됩니다.실행 중인 프로그램이 액세스할 수 있는 메모리 부분은 사용자 프로그램이 액세스할 수 없는 RA(Relative Address) 및 FL(Field Length) 레지스터에 의해 제어됩니다.사용자 프로그램이 주소 a에 있는 중앙 메모리의 워드를 읽거나 쓰려고 하면 프로세서는 먼저 가 0과 FL-1 사이인지 확인합니다.이 경우 프로세서는 주소 RA+a의 중앙 메모리 내의 워드에 액세스한다.이 프로세스는 베이스 바운드 재배치라고 불립니다.각 사용자 프로그램은 코어 메모리를 주소 0으로 시작하는 길이가 FL인 연속 블록 워드로 간주합니다.실제로 이 프로그램은 물리 메모리 내의 임의의 위치에 있을 수 있습니다.이 기술을 사용하면 RA 레지스터가 메모리 내의 위치를 반영하고 있는 한 운영체제에 의해 각 사용자 프로그램을 메인 메모리로 이동("위치 변경")할 수 있습니다.사용자 프로그램이 허용된 범위(즉, FL 이상의 주소를 가진)를 벗어나 메모리에 액세스하려고 하면 인터럽트가 트리거되어 운영체제에 의해 종료됩니다.이 경우 운영체제는 프로그램 메모리의 내용을 기록하고 파일에 등록하는 코어 덤프를 생성하여 프로그램 개발자가 무슨 일이 일어났는지 알 수 있도록 한다.가상 메모리 시스템과의 구별에 주의해 주세요.이 경우 프로세스의 주소 지정 가능한 공간 전체가 코어 메모리에 있어야 하며, 연속되어야 하며, 사이즈는 실제 메모리 용량보다 클 수 없습니다.

최초의 7대의 CDC 6000 시리즈 머신을 제외한 모든 머신에 옵션의 확장 코어 스토리지(ECS) 시스템을 설정할 수 있습니다.ECS는 중앙 메모리에서 사용되는 것과는 다른 종류의 코어 메모리에서 구축되었습니다.이 메모리는 더 느리지만 훨씬 더 클 수 있을 만큼 저렴했다.주된 이유는 ECS 메모리가 코어당 와이어가 2개뿐이기 때문입니다(중앙 메모리용 와이어는 5개).매우 광범위한 전송을 수행했기 때문에 순차 전송 속도는 소형 코어 메모리와 동일했습니다.6000 CPU는 사용자의 프로그램(또는 운영 체제)과 ECS 장치 간에 블록 메모리 전송을 직접 실행할 수 있습니다.광범위한 데이터 경로가 사용되었기 때문에 매우 빠른 작업이었습니다.메모리 경계는 중앙 메모리와 유사한 방식으로 유지되었으며, RA/FL 메커니즘은 운영 체제에 의해 유지되었습니다.ECS는 중앙 메모리에 비해 너무 큰 사용자 데이터 어레이를 포함하는 것, 자주 사용되는 파일 보유, 스왑, 그리고 멀티 메인프레임 복합체의 통신 경로로도 사용할 수 있습니다.

페리페럴 프로세서(PP)

다른 설계에서는 CPU에 할당되어 있던 「하우스키핑」작업을 처리하기 위해서, Cray는 10개의 다른 프로세서를 탑재했습니다.이 프로세서는 이전 컴퓨터인[when?] CDC 160-A에 부분적으로 기반을 두고 있었습니다.Peripheral Processors(PP; 페리페럴 프로세서)라고 불리는 이 기계들은 그 자체로 완전한 컴퓨터였지만 I/O 작업을 수행하고 운영 체제를 실행하도록 조정되었다.(운영 체제의 상당 부분이 PP 상에서 실행되었기 때문에 Central Processor의 대부분의 파워는 사용자 프로그램에서 사용할 수 있습니다.)PP만이 I/O 채널에 액세스할 수 있었습니다.PP(PP0) 중 하나는 메인 CPU에서 실행되는 프로그램의 제어를 포함한 머신의 전체적인 제어이며, 다른 하나는 다양한 I/O 태스크 전용입니다.PP9은 시스템 콘솔 전용입니다.CP 프로그램은 운영체제 기능을 수행해야 할 때 PP0에 의해 모니터링되는 알려진 위치(기준 주소 + 1)에[27] 요청을 넣습니다.필요한 경우 PP0은 다른 PP를 할당하여 필요한 코드를 로드하고 요청을 처리합니다.PP는 작업이 완료되었음을 CP 프로그램에 알리기 위해 RA+1을 클리어합니다.

기계를 제어하는 데 PP0의 고유한 역할은 잠재적인 단일 장애 지점이었습니다. 다른 9개의 PP와 CPU가 정상적으로 작동하더라도 여기에서 발생한 오작동으로 인해 전체 머신이 정지될 수 있습니다.Cray는 이것을 후계기 7600의 설계로 수정했습니다.그 때, 어느 하나의 PP가 컨트롤러가 되어, CPU는 어느 하나의 PP를 이 [when?]역할에 재할당할 수 있었습니다.

각 PP에는 4096개의 12비트 워드 메모리가 포함되어 있습니다.이 메모리는 I/O 버퍼링과 프로그램 스토리지 모두에 사용되었지만 실행 유닛은 배럴과 슬롯이라고 불리는 구성에서 10개의 PP에 의해 공유되었습니다.즉, 실행 유닛('슬롯')은 첫 번째 PP에서 하나의 명령 사이클을 실행한 후 두 번째 PP에서 하나의 명령 사이클 등을 라운드 로빈 방식으로 실행한다는 것을 의미합니다.이는 비용을 절감하기 위해 이루어졌으며, CP 메모리에 대한 액세스에는 10 PP 클럭 사이클이 필요했기 때문에 PP가 CP 메모리에 액세스하면, 데이터는 다음에 PP가 슬롯 시간을 수신할 때 사용할 수 있습니다.

워드 길이, 문자

중앙 CPU에는 60비트 워드가 있고 주변 CPU에는 12비트 워드가 있습니다.CDC는 주변기기의 프로세서가 사용하는12비트 엔티티를 나타내기 위해 바이트라는 용어를 사용했습니다.문자는 6비트, 중앙 프로세서의 명령어는 15비트 또는 30비트이며 18비트 주소 필드가 서명이 있는 경우, 후자는 중앙 메모리의 128K 워드의 직접 주소 지정 가능한 메모리 공간(8비트 바이트, t로 변환됨)을 사용할 수 있습니다.0.94 MB).주소 레지스터의 서명은 개개의 프로그램을 128,000 워드로 제한했습니다.(나중의 CDC 6000 호환 머신은 예산에 따라 256,000 워드의 중앙 메모리를 사용할 수 있지만 개별 사용자 프로그램은 여전히 128,000 워드의 CM로 제한됩니다.) 중앙 프로세서의 명령은 그것들이 타깃이 되었을 때 워드 경계에서 시작되었습니다.점프 스테이트먼트 또는 서브루틴 리턴 점프 명령어, 따라서 단어의 마지막 15비트, 30비트 또는 45비트를 입력하기 위해 no-op 명령이 필요할 수 있습니다.경험이 풍부한 어셈블러 프로그래머는 프로그램 후반부에 필요한 misc 명령으로 이러한 no-op 공간을 채움으로써 프로그램을 미세 조정할 수 있습니다.

CDC 표시 [28][29][30]코드라고 불리는 인코딩의 6비트 문자를 사용하여 단어에 최대 10자를 저장할 수 있습니다.64자의 문자 세트를 사용할 수 있습니다.이는 모든 대문자, 숫자 및 일부 구두점을 사용할 수 있습니다.FORTRAN을 작성하거나 재무 또는 과학 보고서를 인쇄하는 데 충분했습니다.CDC 디스플레이 코드 문자 세트에는 실제로는 64 문자와 63 문자의 2종류가 사용되고 있었습니다.64 문자 세트에서는, 「:」(콜론) 문자가 워드의 마지막 문자인 경우, 무시(제로 채우기)되는 단점이 있었습니다.6/12 디스플레이 코드라고 불리는 보완적인 변형도 Kronos 및 NOS 타임셰어링 시스템에서 사용되어 오래된 [31]소프트웨어와 어느 정도 호환되는 방식으로 ASCII 문자 세트를 완전히 사용할 수 있게 되었습니다.

바이트 주소 지정 명령이 전혀 없는 상태에서, 문자를 단어로 묶고 전환하기 위해 코드를 작성해야 했습니다.매우 큰 워드와 비교적 적은 양의 메모리는 프로그래머들이 데이터를 비트 레벨의 워드로 패킹함으로써 메모리를 자주 절약한다는 것을 의미했다.

단어 크기가 크고 한 단어당 10자이므로 대부분의 경우 한 번에 한 개의 문자를 처리하는 것이 풀어서 처리/재포장하는 것보다 더 빨랐습니다.예를 들어 CDC COBOL 컴파일러는 실제로 이 기술을 사용하여 10진수 필드를 처리하는 데 매우 능숙했습니다.이러한 종류의 기술은 현재 프로세서의 "멀티미디어" 명령에서 일반적으로 사용됩니다[when?].

물리 설계

기계는 4개의 암 각각에서 가장 바깥쪽 18인치(46cm)에 펌프와 열 교환기가 있는 플러스 기호 모양의 캐비닛에 제작되었습니다.냉각은 기계 내에서 Freon이 순환하여 외부 냉각수 공급기로 열을 교환하는 방식으로 수행되었습니다.각 암에는 약 20cm 두께의 섀시가 4개 들어 있고 중앙 부근에 힌지가 있어 책처럼 약간 열 수 있습니다."플러스"의 교차로에는 섀시를 상호 연결하는 케이블이 채워져 있었습니다.섀시의 번호는 1부터16까지입니다(10개의 PPU와 그 메모리 및 12개의 비교적 작은 I/O채널을 모두 포함합니다).CPU의 메인 메모리는 많은 섀시에 분산되어 있었습니다.64K개의 메인 메모리만 있는 시스템에서는 "플러스"의 암 중 하나가 생략되었습니다.

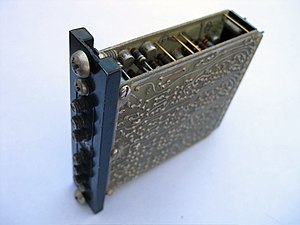

기계의 로직은 약 2.5인치(64mm) 정사각형과 약 2.5cm 두께의 모듈로 패키지화되었습니다.각 모듈에는 한쪽 끝에 커넥터(30핀, 15개의 세로줄 2개)가 있고 반대쪽 끝에 6개의 테스트 포인트가 있습니다.모듈은 열을 제거하기 위해 두 개의 알루미늄 냉판 사이에 배치되었습니다.모듈은 두 개의 병렬 인쇄 회로 기판으로 구성되었으며, 두 개의 기판 중 하나에 또는 두 개의 기판 사이에 컴포넌트가 장착되어 있습니다.이것은 매우 밀도가 높은 패키지를 제공했습니다.일반적으로 수리가 불가능하지만 열전달 특성이 우수합니다.그것은 코드우드 건설로 알려져 있었다.

운영 체제 및 프로그래밍

6600 operating system의 서포트에는, 스케줄이 늦어지는 단점이 있었습니다.이 기계들은[when?] 원래 COS(Chippewa Operating System)라고 불리는 매우 단순한 작업 제어 시스템을 실행했는데, 이 시스템은 이전 CDC 3000 운영 체제를 기반으로 신속하게 "함께 사용"되어 시스템 전달을 테스트하기 위해 실행되었습니다.그러나 이 기계들은 SIPROS(Simultaneous Processing Operating System: 동시 처리 운영 체제)라고 알려진 훨씬 더 강력한 시스템을 사용하여 제공되도록 고안되었습니다. SIPROS는 로스앤젤레스에 있는 회사의 시스템 과학 부서에서 개발되었습니다.고객들은 SIPROS의 기능 목록에 감명을 받았고, 많은 고객들이 SIPROS를 배송 계약에 기재했습니다.

SIPROS는 대실패로 판명되었다.개발 일정이 계속 어긋나 CDC는 납품 지연 패널티 형태로 막대한 이익을 얻었습니다.기계를 출하할 준비가 된 상태로 몇 달 동안 기다린 후, 프로젝트는 결국 취소되었습니다.COS에 종사했던 프로그래머들은 SIPROS에 대한 믿음이 거의 없었고 COS 개선에 계속 노력해 왔습니다.

그 후, operating system의 개발은 2개의 진영으로 분할됩니다.CDC가 허가한 COS의 진화는 캘리포니아의 Sunnyvale 소프트웨어 개발 연구소에서 실시되었습니다.많은 고객이 결국 이 소프트웨어를 사용하여 시스템을 인도받았습니다.이 소프트웨어는 SCOPE(Supervisorary Control Of Program Execution)로 알려져 있습니다.SCOPE 버전1은 기본적으로 분해된 COS입니다.SCOPE 버전2에는 새로운 디바이스와 파일시스템 지원이 포함되어 있습니다.SCOPE 버전3에는 영속적인 파일지원, EI/200 리모트배치 지원 및 INTERCOM 시분할 지원이 포함되어 있습니다.SCOPE는 항상 신뢰성과 유지보수의 큰 문제를 안고 있었습니다.

지하에서 발생한 COS의 진화는 미네소타 주 아덴 힐스 조립 [when?]공장에서 이루어졌다.MCE([Greg] Mansfield And [Dave] Cahlander Executive)는 주로 기계가 사용 가능한 시간 외 시간에 한 명의 프로그래머에 의해 작성되었습니다.이 기능 세트는 기본적으로 COS 및 SCOPE 1과 동일했습니다. 이전 COS 파일 시스템을 유지했지만 코드 모듈러성이 크게 향상되어 시스템 신뢰성과 새로운 스토리지 장치에 대한 적응성이 향상되었습니다.많은 고객들이 CDC에서 복사본을 받아낼 수 있었지만, MACE는 결코 공식 제품이 아니었다.

비공식적인 MCE 소프트웨어는 나중에 그리스의 시간의 신에서 이름을 딴 다음 CDC 운영체제 크로노스(Kronos)의 기반으로 공식 SCOPE 제품보다 선택되었습니다.이[when?] 이야기는 데이브 맨스필드가 미네소타 대학 도서관에 전화를 걸어 "시간"을 뜻하는 고대어를 요청했다고 한다.그는 크로노스 대신 크로노스라고 적었다.TELEX의 시분할 기능과 BATCHIO 리모트 배치 기능의 개발이 주된 마케팅 이유였습니다.Kronos는 영구 파일 기능을 추가하여 COS/SCOPE 1 파일 시스템을 계속 사용했습니다.

SCOPE와 Kronos 운영체제 제품을 통합하려고 하면 NOS(Network Operating System)[when?]가 생성되었습니다.NOS는 모든 CDC 머신의 유일한 운영체제로 의도되어 있었습니다.CDC는 크게 홍보되고 있었습니다.많은 SCOPE 고객은 SCOPE 아키텍처에 계속 의존하기 때문에 CDC는 단순히 이름을 NOS/BE(Batch Environment)로 변경했을 뿐이며, 모든 고객이 NOS를 실행하고 있다고 주장할 수 있었습니다.실제로는 Kronos 코드 베이스를 변경하여 SCOPE 기능을 추가하는 것이 그 반대보다 훨씬 쉬웠습니다.

조립 공장 환경에서는, 고객 [when?]전용이 아닌 다른 operating system도 생산되고 있습니다.여기에는 하드웨어 테스트를 위한 엔지니어링 도구 SMM과 소프트웨어 스모크 테스트를 위한 KALLEIDOSCOPE가 포함되어 있습니다.CDC 필드 엔지니어에게 테스트 중에 일반적으로 사용되는 또 다른 도구는 MALET(Maintenance Application Language for Equipment Testing)로, 엔지니어가 수리 또는 수리한 후 컴포넌트와 디바이스를 테스트하는 데 사용되었습니다.테스트 조건에서는 많은 경우 하드 디스크 팩과 자기 테이프를 사용하여 MALET과 엔지니어가 오류를 검출할 수 있는지 여부를 판단합니다.

CDC는 CDC 6000 시리즈(6600 포함)와 CDC 3000 시리즈 모두에서 SCOPE 및 COMPASS라는 이름을 사용했습니다.

- CDC에서 두 [33][34]패밀리의 어셈블리 언어를 위해 COMPASS라는 이름을 사용했습니다.

- SCOPE라는 [35]이름은 3000 및 6000 시리즈에서의 실장용으로 사용되었습니다.

CDC 7600

CDC 7600은 원래 기존의 6000 시리즈머신과도 완전히 호환되도록[when?] 설계되어 있었습니다.CDC 6800으로 알려진 제품 라인업을 시작했습니다.그러나 설계자는 설계 과정에서 기존 6000 시리즈 머신과의 완벽한 호환성을 유지하면 성능 향상에 한계가 있다고 판단하고 성능 향상을 위해 호환성을 희생하기로 결정했습니다.CDC 7600의 CPU는 기본적으로 6400 및 6600의 CPU와 호환성이 있기 때문에 상위 언어의 소스 코드 수준에서 코드 이식성이 가능하지만 CDC 7600의 하드웨어, 특히 Peripheral Processor Unit(PPU)의 하드웨어는 상당히 달랐고 CDC 7600에는 다른 운영 체제가 필요했습니다.이것은 설계자가 CPU를 포함한 컴퓨터 시스템 전체의 동작을 제어하기 위해 Peripheral Processor(PP0; 페리페럴 프로세서)에 완전히 의존하는 것과 같은 6000 시리즈 설계의 일부 특성을 개선할 수 있었기 때문에 다소 우연한 것으로 판명되었다.6600 CPU와 달리 CDC 7600의 CPU는 모든 레지스터 콘텐츠를 코어 메모리와 스왑하는 Central Exchange Jump(XJ) 명령을 통해 자체 동작을 제어할 수 있습니다.실제로 6000 시리즈 머신에는 이 기능이 새로 장착되었습니다.

「 」를 참조해 주세요.

메모들

- ^ a b 애덤스 서베이 1968

- ^ a b 컴퓨터 디렉토리 및 구매자 가이드 1967

- ^ a b c 6000 시리즈 사이트 준비, 65년 9월

- ^ "Control Data 6600: The Supercomputer Arrives". Dr. Dobb's. Archived from the original on 2017-06-05. Retrieved 2018-10-06.

- ^ CDC 6400 Central Processor 트레이닝 매뉴얼, 67년 2월

- ^ Cyber 70 제품 발표

- ^ a b 숫돌 벤치마크 이력 및 결과

- ^ Cayton, Andrew R. L.; Sisson, Richard; Zacher, Chris (2006). The American Midwest: An Interpretive Encyclopedia. ISBN 0253003490.

- ^ "CDC 6600 – Historical Interlude: From the Mainframe to the Minicomputer Part 2, IBM and the Seven Dwarfs – They Create Worlds". November 8, 2014.

- ^ "Seymour Cray가 설계한 CDC 6600은 당대 두 번째로 빠른 기계인 IBM 7030 Stretch보다 거의 3배 더 빨랐습니다."

- ^ 1964년 Cray의 CDC 6600은 Stretch를 제치고 지구상에서 가장 빠른 컴퓨터가 되었습니다.

- ^ Anthony, Sebastian (April 10, 2012). "The History of Supercomputers". ExtremeTech. Retrieved 2015-02-02.

- ^ "CDC 6600". Encyclopædia Britannica. Retrieved 2015-02-02.

- ^ "7600 설계는 다른 어떤 슈퍼컴퓨터 설계보다 오래 지속되었습니다.1969년 출시된 이후 1976년 Cray 1이 출시될 때까지 모든 컴퓨터 중 최고의 성능을 발휘했습니다."

- ^ N. Lewis, IEEE 컴퓨팅 역사 제39호(2017년): 25-40호, 2017년 1호, "로스앨러모스의 슈퍼컴퓨터 선택에서의 구매력: 경쟁, 반대, 컴퓨팅 전략"

- ^ "The CDC 6600 arrives at CERN". CERN Timelines.

- ^ Compagnie Lyonnaise de Cinéma (14 Jan 1965). "The Contral Data 6600 computer arrives at CERN, the European Organisation for Nuclear Research". CDS Videos.

- ^ "Bumper Crop". Research Review. Lawrence Berkeley Laboratory. 1981. Archived from the original on 2018-01-18. Retrieved 2017-05-04.

- ^ "Control Data 6600: The Supercomputer Arrives". Archived from the original on 7 July 2019.

- ^ "Control Data Corporation, "Little Character" Prototype". Computer History Museum. Retrieved 21 April 2016.

- ^ Mark D. Hill; Norman P. Jouppi; Gurindar S. Sohi, eds. (September 23, 1999). Readings in Computer Architecture. Morgan Kaufmann. p. 11. ISBN 978-1558605398.

- ^ 메모의 정확한 이미지는 다음과 같습니다.

- ^ Smotherman, Mark; Spicer, Dag. "IBM's Single-Processor Supercomputer Efforts".

- ^ UNIVAC 1100/2200 시리즈는 여전히 1개의 보완 환경을 제공하지만 2개의 보완 하드웨어를 사용합니다.

- ^ Control Data 6000 Series Hardware Reference Manual (PDF). 1978.

- ^ "Archived copy". Archived from the original on 2014-01-02. Retrieved 2005-06-13.

{{cite web}}: CS1 maint: 제목으로 아카이브된 복사(링크) - ^ 이 설명에서는 CDC 소프트웨어의 초기 버전에 대해 설명합니다.이후 버전은 Central Exchange Jump(XJ) 명령을 사용하여 CP에서 완전히 실행할 수 있는 기능의 오버헤드를 줄입니다.

- ^ "EBCDIC"이 IBM과 *원래* 관련되었던 것처럼 "표시 코드"라는 용어는 CDC와 많이 관련되었습니다.업계에서 사용되는 다른 용어로는 BCD와 SIXB가 있습니다.IT(후자는 DEC가 선호)

- ^ "DEC/PDP Character Codes".

- ^ "SIXBIT Character Code Reference". Archived from the original on 2016-11-24. Retrieved 2017-10-15.

- ^ "CDC Kronos" (PDF).

- ^ 컴퓨터의 이해: 속도와 파워 1990, 페이지 17.

- ^ "COMPASS for 24 bit machines" (PDF). Archived from the original (PDF) on 2012-09-10. Retrieved 2017-10-15.

- ^ "COMPASS for 48 bit machines" (PDF).

- ^ "CDC는 3600용 SCOPE 운영 체제의 초기 버전을 제공했습니다."

레퍼런스

- 그리쉬만, 랄프(1974년).Control Data 6000 시리즈 및 Cyber 70 시리즈용 어셈블리 언어 프로그래밍뉴욕, 뉴욕: 알고리즘 프레스.[2]

- Control Data 6400/6500/6600 컴퓨터 시스템 레퍼런스 매뉴얼

- 손튼, J. (1963년)컴퓨터 설계에 관한 고려사항– Control Data 6600까지 [3]

- 손튼, J.(1970).컴퓨터 설계 -Control Data 6600.Glenview, IL: Scott, Foresman and Co.[4]

- (1990) 컴퓨터의 이해: 속도와 파워, 타임 라이프 시리즈 ISBN 0809475863

외부 링크

- Neil R. Lincoln은 컴퓨터 아키텍처 및 디자인 분야의 컨트롤 데이터 코퍼레이션(CDC) 엔지니어 18명으로 미네소타 대학교 찰스 배비지 연구소 소속입니다.엔지니어에는 Robert Moe, Wayne Specker, Dennis Greenna, Tom Rowan, Maurice Hutson, Curt Alexander, Don Pagelkopf, Maris Bergmanis, Dolan Toth, Chuck Hawley, Larry Krueger, Mike Pavlov, Dave Resnick, Hawnick, Hawnick, Ha, Khard Bhen, Khen, Ha, Hutson 등이 있습니다.링컨.토론 주제로는 CDC 1604, CDC 6600, CDC 7600, CDC 8600, CDC STAR-100 및 Seymour Cray가 있습니다.

- 제어 데이터 6600의 병렬 작동, James Thornton

- CDC 6600 및 C의 Seymour Cray가 설계한 기타 기계에 대한 프레젠테이션.Microsoft Research의 Gordon Bell(구 DEC)

- "CDC 6600's Five Year Reign". Computer History Museum. 2003.

The 6600 had 400,000 transistors and more than 100 miles of wiring.

– 개요 (사진 포함)