ARM Cortex-M

ARM Cortex-MARM Cortex-M은 Arm Holdings에서 라이선스를 취득한32비트 RISC ARM 프로세서코어 그룹입니다이러한 코어는 수백억 개의 소비자 [1]장치에 내장되어 있는 저비용 에너지 효율 집적 회로에 최적화되어 있습니다.마이크로컨트롤러 칩의 주성분인 경우가 많지만 다른 칩에도 내장되어 있는 경우도 있습니다.Cortex-M 패밀리는 Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M7, Cortex-M23, Cortex-M33,[2][3][4][5][6][7][8] Cortex-M35P, Cortex-M55로 구성되어 있다.Cortex-M4 / M7 / M33 / M35P / M55 코어에는 FPU 실리콘 옵션이 있습니다.실리콘에 포함되어 있는 경우, 이러한 코어는 「Cortex-Mx with FPU」 또는 「Cortex-MxF」라고 불리기도 합니다.여기서 「x」는 코어 바리안트입니다.

개요

| 32비트 | |

|---|---|

| 연도 | 핵심 |

| 2004 | 코텍스-M3 |

| 2007 | 코텍스-M1 |

| 2009 | 코텍스-M0 |

| 2010 | 코텍스-M4 |

| 2012 | Cortex-M0+ |

| 2014 | 코텍스-M7 |

| 2016 | 코텍스-M23 |

| 2016 | 코텍스-M33 |

| 2018 | Cortex-M35P |

| 2020 | 코텍스-M55 |

| 2022 | 코텍스-M85 |

ARM Cortex-M 패밀리는 마이크로 컨트롤러, ASIC, ASSP, FPGA 및 SoC에서 사용하도록 설계된 ARM 마이크로프로세서 코어입니다.Cortex-M 코어는 일반적으로 전용 마이크로 컨트롤러 칩으로 사용되지만 전원 관리 컨트롤러, I/O 컨트롤러, 시스템 컨트롤러, 터치 스크린 컨트롤러, 스마트 배터리 컨트롤러 및 센서 컨트롤러로 SoC 칩 내부에 "숨겨져" 있습니다.

Cortex-A 코어와의 주된 차이점은 메모리 관리 유닛(MMU)이 없다는 것입니다.통상, 이 클래스의 프로세서에서는, 완전한 operating system은 동작하지 않습니다.

과거 8비트 마이크로컨트롤러가 큰 인기를 끌었지만 보급형 Cortex-M 칩 가격이 하락하면서 Cortex-M은 8비트 시장을 서서히 잠식해 왔다.Cortex-M은 32비트 연산에서 혜택을 받는 응용 프로그램에서 8비트 칩을 대체하고 ARM7 및 ARM9과 같은 오래된 ARM 코어를 대체하기 위해 널리 사용되고 있습니다.

면허증.

Arm Holdings는 독자적인 설계에 근거해 CPU 디바이스를 제조 또는 판매하지 않고, 관계자에게 프로세서 아키텍처를 라이선스합니다.Arm에서는 비용 및 성과물에 따라 다양한 라이센스 조건을 제공합니다.모든 라이선스 계약자에게 Arm은 ARM 코어에 대한 통합 가능한 하드웨어 설명과 소프트웨어 개발 도구 세트 및 ARM CPU를 포함한 제조된 실리콘을 판매할 권리를 제공합니다.

실리콘 커스터마이즈

Integrated Device Manufacturers(IDM; 통합 디바이스 제조업체)는 ARM 프로세서 IP를 합성 가능한 RTL(Verilog로 작성)로 받습니다.이 형식에서는 아키텍처 수준의 최적화 및 확장을 수행할 수 있습니다.이를 통해 제조사는 높은 클럭 속도, 매우 낮은 전력 소비량, 명령 집합 확장(부동소수점 포함), 크기 최적화, 디버깅 지원 등 맞춤형 설계 목표를 달성할 수 있습니다.특정 ARM CPU 칩에 탑재되어 있는 컴포넌트를 확인하려면 , 제조원의 데이터 시트 및 관련 메뉴얼을 참조해 주세요.

Cortex-M 코어의 실리콘 옵션은 다음과 같습니다.

- SysTick 타이머:프로세서와 Negrated Vectored Interrupt Controller(NVIC; 네스트 벡터 인터럽트 컨트롤러)의 양쪽 기능을 확장하는 24비트 시스템타이머존재하는 경우 설정 가능한 추가 우선순위가 SysTick [9][10][11]인터럽트도 제공됩니다.SysTick 타이머는 옵션이지만 Cortex-M 마이크로컨트롤러가 없는 경우는 거의 없습니다.Cortex-M33 마이크로 컨트롤러에 Security Extension 옵션이 있는 경우, SysTicks 2개(Secure와 Non-Secure)가 있습니다.

- 비트 밴드: 메모리 전체 단어를 비트 밴드 영역의 단일 비트에 매핑합니다.예를 들어, 에일리어스 워드에 쓰면 비트 밴드 영역의 대응하는 비트가 설정 또는 클리어 됩니다.이를 통해 비트 밴드 영역의 모든 비트에 워드 정렬 주소에서 직접 액세스할 수 있습니다.특히 [9][10][11]명령의 읽기-수정-쓰기 시퀀스를 수행하지 않고 개별 비트를 C/C++에서 설정, 클리어 또는 전환할 수 있습니다.비트밴드는 옵션이지만 Cortex-M3 및 Cortex-M4 마이크로컨트롤러가 없는 경우는 거의 없습니다.일부 Cortex-M0 및 Cortex-M0+ 마이크로 컨트롤러는 비트 밴드를 가지고 있습니다.

- Memory Protection Unit (MPU) :특권 및 접근규칙을 적용하여 메모리 영역을 보호합니다.최대 8개의 서로 다른 영역을 지원하며, 각 영역은 8개의 동일한 크기의 하위 [9][10][11]영역으로 분할할 수 있습니다.

- 긴밀하게 결합된 메모리(TCM): 중요한 루틴, 데이터, 스택을 보관하기 위해 사용되는 저지연 RAM.캐시를 제외하고 일반적으로 마이크로 컨트롤러에서 가장 빠른 RAM입니다.

| ARM 코어 | 코텍스 M0[2] | 코텍스 M0+[3] | 코텍스 M1[4] | 코텍스 M3[5] | 코텍스 M4[6] | 코텍스 M7[7] | 코텍스 M23[8] | 코텍스 M33[12] | 코텍스 M35P |

|---|---|---|---|---|---|---|---|---|---|

| SysTick 24비트타이머 | 선택적. (0,1) | 선택적. (0,1) | 선택적. (0,1) | 네. (1) | 네. (1) | 네. (1) | 선택적. (0,1,2) | 네. (1,2) | 네. (1,2) |

| 싱글 사이클 I/O 포트 | 아니요. | 선택적. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. |

| 비트 밴드 메모리 | 아니요[13]. | 아니요[13]. | 아니요* | 선택적. | 선택적. | 선택적. | 아니요. | 아니요. | 아니요. |

| 메모리 보호 유닛(MPU) | 아니요. | 선택적. (0,8) | 아니요. | 선택적. (0,8) | 선택적. (0,8) | 선택적. (0,8,16) | 선택적. (0,4,8,12,16) | 선택적. (0,4,8,12,16) | 선택적. * |

| 보안 속성 유닛(SAU) 및 스택 제한 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. (0,4,8) | 선택적. (0,4,8) | 선택적. * |

| 지침 TCM | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 아니요. |

| 데이터 TCM | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 아니요. |

| 명령 캐시 | 아니요[14]. | 아니요[14]. | 아니요[14]. | 아니요[14]. | 아니요[14]. | 선택적. | 아니요. | 아니요. | 선택적. |

| 데이터 캐시 | 아니요[14]. | 아니요[14]. | 아니요[14]. | 아니요[14]. | 아니요[14]. | 선택적. | 아니요. | 아니요. | 아니요. |

| 벡터 테이블 간격띄우기 레지스터(VTOR) | 아니요. | 선택적. (0,1) | 선택적. (0,1) | 선택적. (0,1) | 선택적. (0,1) | 선택적. (0,1) | 선택적. (0,1,2) | 네. (1,2) | 네. (1,2) |

- 주의: 대부분의 Cortex-M3 및 M4 칩은 비트밴드와 MPU를 갖추고 있습니다.비트밴드 옵션은 Cortex-M System Design [13]Kit를 사용하여 M0/M0+에 추가할 수 있습니다.

- 주의: 소프트웨어는 [11]기능을 사용하기 전에 기능의 존재를 확인해야 합니다.

- 참고: Cortex-M35P의 테크니컬 레퍼런스 매뉴얼이 공개될 때까지 공개 정보가 한정되어 있습니다.

- 데이터 엔디안: 리틀 엔디안 또는 빅 엔디안.기존 ARM 코어와 달리 Cortex-M은 이러한 선택 사항 중 하나로 실리콘에 영구적으로 고정되어 있습니다.

- 인터럽트: 1~32(M0/M0+/M1), 1~240(M3/M4/M7/M23), 1~480(M33/M35P)

- 웨이크업 인터럽트 컨트롤러:선택적.

- 벡터 테이블 오프셋 레지스터:선택적.(M0에서는 사용할 수 없습니다).

- 명령 가져오기 폭: 16비트만 또는 대부분 32비트입니다.

- 사용자/권한 지원: 옵션.

- 모든 레지스터를 리셋합니다(옵션).

- 싱글 사이클 I/O 포트: 옵션 (M0+/M23)

- 디버깅 액세스 포트(DAP): 없음, SWD, JTAG 및 SWD(모든 Cortex-M 코어의 경우 옵션)

- 디버깅 지원 중지: 옵션.

- 워치포인트 비교기 수: 0 ~2(M0/M0+/M1), 0 ~4(M3/M4/M7/M23/M33/M35P)

- 브레이크 포인트 비교기 수: 0 ~4(M0/M0+/M1/M23) 및 0 ~8(M3/M4/M7/M33/M35P)

명령어 세트

Cortex-M0/M0+/M1은 ARMv6-M [9]아키텍처를 [10]구현하고, Cortex-M3는 ARMv7-M 아키텍처를 구현하며, Cortex-M4/[10]Cortex-M7은 ARMv7E-M 아키텍처를 구현하고, Cortex-M23/M33P는 ARMv를 구현합니다.아키텍처는 ARMv6-M, ARMv7-M, ARMv7E-M에 대한 바이너리 명령어 상향 호환입니다.Cortex-M0 / Cortex-M0+ / Cortex-M1에서 사용할 수 있는 바이너리 명령은 Cortex-M3 / Cortex-M4 / Cortex-M7 / M33에서 수정 없이 실행할 수 있습니다.Cortex-M 아키텍처에서는 Thumb-1 및 Thumb-2 명령어 세트만 지원됩니다.기존 32비트 ARM 명령어 세트는 지원되지 않습니다.

모든 Cortex-M 코어는 32비트 결과 배수를 포함한 대부분의 Thumb-1, 일부 Thumb-2로 구성된 명령어 서브셋을 구현합니다.Cortex-M0 / Cortex-M0+ / Cortex-M1 / Cortex-M23은 가장 작은 실리콘 다이를 만들도록 설계되었으며, 따라서 Cortex-M 패밀리 중 가장 적은 명령어를 가집니다.

Cortex-M0/M0+/M1에는 Tumb-1 명령어가 포함되어 있습니다.단, ARMv7-M 아키텍처에 추가된 새로운 명령어(CBZ, CBNZ, IT)는 제외됩니다.Cortex-M0 / M0+ / M1에는 Thumb-2 명령의 마이너 서브셋(BL, DMB, DSB, ISB, MRS, MSR)[9]이 포함되어 있습니다.Cortex-M3/M4/M7/M33/M35P에는 기본 엄지-1 및 엄지-2 명령이 모두 있습니다.Cortex-M3에는 Thumb-1 명령어, 모든 Thumb-2 명령어, 하드웨어 정수분할 명령어, 포화 산술 명령어 3개가 추가되어 있습니다.Cortex-M4에는 DSP 명령과 옵션의 Single-Precision Floating Point Unit(VFPv4-SP; 단정도 부동소수점 유닛)이 추가됩니다.Cortex-M7은 옵션의 배정밀 FPU(VFPv5)[7][10]를 추가합니다.Cortex-M23/M33은 TrustZone 명령을 추가합니다.

| 암 코어 | 코텍스 M0[2] | 코텍스 M0+[3] | 코텍스 M1[4] | 코텍스 M3[5] | 코텍스 M4[6] | 코텍스 M7[7] | 코텍스 M23[8] | 코텍스 M33[12] | 코텍스 M35P | 코텍스 M55 |

|---|---|---|---|---|---|---|---|---|---|---|

| ARM 아키텍처 | ARMv6-M[9] | ARMv6-M[9] | ARMv6-M[9] | ARMv7-M[10] | ARMv7E-M[10] | ARMv7E-M[10] | ARMv8-M 베이스라인[15] | ARMv8-M 메인라인[15] | ARMv8-M 메인라인[15] | 암v8.1-M |

| 컴퓨터 아키텍처 | 폰 노이만 | 폰 노이만 | 폰 노이만 | 하버드 | 하버드 | 하버드 | 폰 노이만 | 하버드 | 하버드 | 하버드 |

| 명령 파이프라인 | 3단계 | 2단계 | 3단계 | 3단계 | 3단계 | 6 스테이지 | 2단계 | 3단계 | 3단계 | 4 ~ 5 스테이지 |

| 엄지손가락-1 지침 | 대부분의. | 대부분의. | 대부분의. | 전체 | 전체 | 전체 | 대부분의. | 전체 | 전체 | 전체 |

| 엄지손가락-2 지침 | 몇개 | 몇개 | 몇개 | 전체 | 전체 | 전체 | 몇개 | 전체 | 전체 | 전체 |

| 명령의 곱셈 32x32 = 32비트 결과 | 네. | 네. | 네. | 네. | 네. | 네. | 네. | 네. | 네. | 네. |

| 명령의 곱셈 32x32 = 64비트 결과 | 아니요. | 아니요. | 아니요. | 네. | 네. | 네. | 아니요. | 네. | 네. | 네. |

| 명령 분할 32/32 = 32비트 비율 | 아니요. | 아니요. | 아니요. | 네. | 네. | 네. | 네. | 네. | 네. | 네. |

| 포화 명령 | 아니요. | 아니요. | 아니요. | 몇개 | 네. | 네. | 아니요. | 네. | 네. | 네. |

| DSP의 순서 | 아니요. | 아니요. | 아니요. | 아니요. | 네. | 네. | 아니요. | 선택적. | 선택적. | 선택적. |

| 단정도(SP) 부동 소수점 명령 | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. | 아니요. | 선택적. | 선택적. | 선택적. |

| Double Precision (DP; 더블 정밀도) 부동 소수점 명령 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 아니요. | 선택적. |

| 하프 정밀도(HP) | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. |

| Trust Zone 명령 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. | 선택적. | 선택적. |

| 코프로세서 명령 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. | 선택적. |

| 헬륨 기술 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. |

| 인터럽트 레이텐시 (제로 대기 상태의 RAM인 경우) | 16 사이클 | 15 사이클 | 23(NMI의 경우 26(IRQ의 경우 | 12 사이클 | 12 사이클 | 12 사이클 14 최악의 경우 | 15 보안 확장 없음 27 보안 확장 | 12 보안 확장 없음 보안 확장 | 미정 | 미정 |

- 주의: Cortex-M0/M0+/M1에는 CBZ, CBNZ, [9][10]IT의 16비트 Thumb-1 명령어가 포함되어 있지 않습니다.

- 주의: Cortex-M0/M0+/M1에는 BL, DMB, DSB, ISB, MRS, MSR의 [9][10]32비트 Thumb-2 명령만 포함되어 있습니다.

- 참고: Cortex-M0/M0+/M1/M23에는 32비트 곱셈 명령(32비트 × 32비트 = 32비트)만 있습니다.Cortex-M3/M4/M7/M33/M35P에는 32비트 곱셈 명령과 64비트 곱셈 명령(32비트)이 포함되어 있습니다.Cortex-M4/M7(옵션 M33/M35P)에는 (16비트=32비트), (32비트×16비트=상위32비트), (32비트×32비트=상위32비트) [9][10]곱셈에 대한 DSP 명령이 포함되어 있습니다.

- 주의: 곱셈 및 나누기 명령을 완료하는 사이클 수는 ARM Cortex-M 코어 설계에 따라 다릅니다.일부 코어에는 빠른 속도 또는 작은 크기(저속) 중 하나를 선택할 수 있는 실리콘 옵션이 있기 때문에 코어에는 더 적은 실리콘을 사용하고 더 많은 사이클 수를 사용할 수 있습니다.나눗셈 명령 또는 느린 반복 곱셈 명령 실행 중에 인터럽트가 발생하면 프로세서가 명령을 포기한 후 인터럽트가 반환된 후 다시 시작합니다.

- 다중 명령 "32비트 결과" – Cortex-M0/M0+/M23은 1 또는 32사이클 실리콘 옵션, Cortex-M1은 3 또는 33사이클 실리콘 옵션, Cortex-M3/M4/M33/M35P는 1사이클 실리콘 옵션입니다.

- 곱셈 명령 "64비트 결과" – Cortex-M3는 3~5사이클(값에 따라 다름), Cortex-M4/M7/M33/M35P는 1사이클입니다.

- 분할 명령 – Cortex-M3/M4는 2–12 사이클(값에 따라 다름), Cortex-M7은 3–20 사이클(값에 따라 다름), Cortex-M23은 17 또는 34 사이클 옵션, Cortex-M33은 2–11 사이클(값에 따라 다름), Cortex-M35P는 TBD입니다.

- 주의: Cortex-M4/M7/M33/M35P는 FPU 또는 단정밀(SP) FPU 중 하나를 선택할 수 있으며, Cortex-M7에는 단정밀(SP)과 2정밀(DP)을 모두 지원하는 세 번째 실리콘 옵션이 추가되었습니다.Cortex-M4/M7/M33/M35P에 FPU가 있으면 Cortex-M4F/Cortex-M7F/Cortex-M33F/[9][10]Cortex-M35PF로 알려져 있습니다.

- 주의: Cortex-M 시리즈에는 sleep 모드용 새로운 16비트 Thumb-1 명령어 SEV, WFE, WFI가 포함되어 있습니다.

- 주의: 인터럽트 레이텐시 사이클 카운트는 1) 스택이 제로웨이트 상태의 RAM에 배치되어 2) 다른 인터럽트 기능이 현재 실행되지 않고 3) 보안 확장 옵션이 존재하지 않는 것을 전제로 하고 있습니다.이는 추가 사이클이 추가되기 때문입니다.하버드 컴퓨터 아키텍처의 Cortex-M 코어는 Von Neumann 컴퓨터 아키텍처의 Cortex-M 코어보다 인터럽트 레이텐시가 짧습니다.

| 그룹. | 인스톨 비트 | 지침들 | 코텍스 M0, M0+, M1 | 코텍스 M3 | 코텍스 M4 | 코텍스 M7 | 코텍스 M23 | 코텍스 M33, M35P | 코텍스 M55 |

|---|---|---|---|---|---|---|---|---|---|

| 엄지손가락 | 16 | ADC, ADD, ADR 및 ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSH, LDR, LDR, LSH | 네. | 네. | 네. | 네. | 네. | 네. | 네. |

| 엄지손가락 | 16 | CBNZ, CBZ | 아니요. | 네. | 네. | 네. | 네. | 네. | 네. |

| 엄지손가락 | 16 | IT부문 | 아니요. | 네. | 네. | 네. | 아니요. | 네. | 네. |

| 엄지손가락-2 | 32 | BL, DMB, DSB, ISB, MRS, MSR | 네. | 네. | 네. | 네. | 네. | 네. | 네. |

| 엄지손가락-2 | 32 | SDIV, UDIV, MOVT, MOVW | 아니요. | 네. | 네. | 네. | 네. | 네. | 네. |

| 엄지손가락-2 | 32 | ADC, ADD, ADR 및 ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ, CMN, CMP, DBG, EOR, LDC, LDM, LDRB, LDRBTSSAT, STC, STM, STR, STRBT, STRD, STREX, STREXB, STREXH, STRH, STRT, SUB, SXTB, SXTH, TBTH, TEQ | 아니요. | 네. | 네. | 네. | 아니요. | 네. | 네. |

| DSP | 32 | PKH, QADD, QADD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB, QSUB8, SADD16, SEL, SHADD16, SHADD16, SHADD16, SHADD8, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHASX8, UHSAX16, UHSUB16, UHSUB16, UHSUB16, UHSUB, UHSUB, UHSB, UHSUB, UHSB, UHSB | 아니요. | 아니요. | 네. | 네. | 아니요. | 선택적. | 네. |

| SP 플로트 | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMR, VMUL, VNM, VNM | 아니요. | 아니요. | 선택적. | 선택적. | 아니요. | 선택적. | 선택적. |

| DP 플로트 | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | 아니요. | 아니요. | 아니요. | 선택적. | 아니요. | 아니요. | 선택적. |

| 트러스트 존 | 16 | BLXNS, BXNS | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. | 선택적. |

| 트러스트 존 | 32 | SG, TT, TTT, TTA, TTAT | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. | 선택적. |

| 코프로세서 | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRC2, MRC2 | 아니요. | 아니요. | 아니요. | 아니요. | 아니요. | 선택적. | 선택적. |

- 주의: MOVW는 32비트의 "와이드" MOV 명령을 의미하는 에일리어스입니다.

- 주의: Cortex-M1의 경우 WFE/WFI/SEV 명령이 존재하지만 NOP 명령으로 실행합니다.

- 메모: 단정도(SP) FPU 명령은 SP FPU 옵션이 실리콘에 존재하는 경우에만 Cortex-M4/M7/M33/M35P에서 유효합니다.

- 주의: DP FPU 명령은 DP FPU 옵션이 실리콘에 존재하는 경우에만 Cortex-M7에서 유효합니다.

폐지

ARM Cortex-M 시리즈용 ARM 아키텍처는 오래된 레거시 [9][10]코어에서 일부 기능을 제거했습니다.

- 32비트 ARM 명령 세트는 Cortex-M 코어에 포함되어 있지 않습니다.

- Endianness는 Cortex-M 코어의 실리콘 구현에서 선택됩니다.레거시 코어를 사용하면 데이터 엔디안 모드를 "즉각" 변경할 수 있습니다.

- 보조 프로세서는 ARM Cortex-M33/M35P 코어의 "ARMv8-M 메인라인"에서 실리콘 옵션이 다시 도입될 때까지 Cortex-M 코어에서 지원되지 않았습니다.

32비트 ARM 명령어세트의 기능은 Thumb-1 명령어세트와 Thumb-2 명령어세트에 의해 여러 면에서 중복되지만 일부 ARM 기능에는 유사한 기능이 없습니다.

- SWP 및 SWPB(swap) ARM 명령에는 Cortex-M에는 유사한 기능이 없습니다.

16비트 Thumb-1 명령 세트는 ARMv4T 아키텍처와 함께 레거시 ARM7T 코어로 처음 출시된 이후 시간이 지남에 따라 발전해 왔습니다.각 레거시 ARMv5 / ARMv6 / ARMv6T2 아키텍처가 출시됨에 따라 새로운 Thumb-1 명령이 추가되었습니다.Cortex-M 코어에서 일부 16비트 Thumb-1 명령이 삭제되었습니다.

- "BLX <immediate> 명령어는 Thumb-1 명령어세트에서 ARM 명령어세트로 전환하기 위해 사용되었기 때문에 존재하지 않습니다."BLX <register>" 명령은 Cortex-M에서도 사용할 수 있습니다.

- 데이터 엔디안 모드의 온 더 플라이 전환이 더 이상 지원되지 않으므로 SETEND가 존재하지 않습니다.

- ARM Cortex-M33/M35P 코어의 "ARMv8-M 메인라인"에 실리콘 옵션이 다시 도입될 때까지 Cortex-M 코어에서는 공동 프로세서 명령이 지원되지 않았습니다.

- 명령어 바이너리 코딩은 동일하지만 SWI 명령어는 SVC로 이름이 변경되었습니다.단, 예외 모델이 변경되었기 때문에 SVC 핸들러 코드는 SWI 핸들러 코드와 다릅니다.

코텍스-M0

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv6-M |

| 명령 집합 | 엄지 1(대부분), 엄지 2 (일부) |

Cortex-M0 코어는 실리콘 다이 크기가 작아 최저가 칩에 사용할 수 있도록 최적화되어 있습니다.

Cortex-M0 코어의 주요 특징은 다음과 같습니다.[2]

- ARMv6-M 아키텍처[9]

- 3단 파이프라인

- 명령 집합:

- Thumb-1(대부분), CBZ, CBNZ, IT 누락

- Thumb-2 (일부), BL, DMB, DSB, ISB, MRS, MSR만

- 32비트 하드웨어 정수에 32비트 결과 곱셈

- 1~32 인터럽트 및 NMI

실리콘 옵션:

- 하드웨어 정수 곱셈 속도: 1 또는 32 사이클.

칩스

다음 마이크로컨트롤러는 Cortex-M0 코어를 기반으로 합니다.

- ABOV AC30M1x64

- Cypress PSoC 4000, 4100, 4100M, 4200, 4200DS, 4200L, 4200M

- Infineon XMC1100, XMC1200, XMC1300, XMC1400, TLE984x

- 대화상자 DA1458x, DA1468x

- 북유럽어 nRF51

- NXP LPC1100, LPC1200

- Nuvoton NuMicro

- Sonix SN32F700

- 세인트 STM32 F0

- 도시바 TX00

- Vorago VA10800(극한 온도), VA10820(방사선 경화)

다음 칩에는 보조 코어로 Cortex-M0이 있습니다.

- NXP LPC4300(Cortex-M4F×1+Cortex-M0×1)

- Texas Instruments SimpleLink Wireless MCUs CC1310 및 CC2650 (프로그래밍 가능한 Cortex-M3 프로세서x 1 + Cortex-M0 네트워크 프로세서x 1 + 전용 센서 컨트롤러 엔진x 1 )

Cortex-M0+

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv6-M |

| 명령 집합 | 엄지 1(대부분), 엄지 2 (일부) |

Cortex-M0+는 Cortex-M0의 최적화된 슈퍼셋입니다.Cortex-M0+는 Cortex-M0과 완전한 명령어셋 호환성을 가지고 있기 때문에 동일한 컴파일러와 디버깅툴을 사용할 수 있습니다.Cortex-M0+ 파이프라인은 3단계에서 2단계로 축소되어 전력 사용량이 감소하였습니다.기존 Cortex-M0의 디버깅 기능과 더불어 간단한 명령 트레이스 버퍼를 제공하는 Micro Trace Buffer(MTB)라고 불리는 실리콘 옵션을 Cortex-M0+에 추가할 수 있습니다.또한 Cortex-M0+는 메모리 보호 장치(MPU) 및 벡터 테이블 [3]재배치 등의 실리콘 옵션으로 추가할 수 있는 Cortex-M3 및 Cortex-M4 기능을 받았습니다.

Cortex-M0+ 코어의 주요 특징은 다음과 같습니다.[3]

- ARMv6-M 아키텍처[9]

- 2단계 파이프라인(Cortex-M0보다 1개 적음)

- 명령어 세트: (Cortex-M0과 동일)

- Thumb-1(대부분), CBZ, CBNZ, IT 누락

- Thumb-2 (일부), BL, DMB, DSB, ISB, MRS, MSR만

- 32비트 하드웨어 정수에 32비트 결과 곱셈

- 1~32 인터럽트 및 NMI

실리콘 옵션:

- 하드웨어 정수 곱셈 속도: 1 또는 32 사이클

- 8 지역 메모리 보호 유닛(MPU) (M3 및 M4와 동일)

- 벡터 테이블 재배치(M3, M4와 동일)

- 싱글 사이클 I/O 포트(M0+/M23 지원)

- Micro Trace Buffer(MTB)(M0+/M23/M33/M35P에서 사용 가능)

칩스

다음 마이크로컨트롤러는 Cortex-M0+ 코어를 기반으로 합니다.

- ABOV 반도체 A31G11x, A31G12x, A31G314

- Cypress PSoC 4000S, 4100S, 4100S+, 4100PS, 4700S, FM0+

- Epson S1C31W74, S1C31D01, S1C31D50

- Holtek HT32F52000

- 마이크로칩(Atmel) SAM C2, D0, D1, D2, DA, L2, R2, R3

- NXP LPC800, LPC11E60, LPC11U60

- NXP(Freescale) Kinetis E, EA, L, M, V1, W0

- Rasberry Pi RP2040 (M0+코어x 2 )

- 르네사스 S124, S128, RE, RE01

- Silicon Labs ( Energy Micro ) EFM32 제로, 해피

- ST STM32 L0, G0

다음 칩에는 보조 코어로 Cortex-M0+가 있습니다.

가장 작은 ARM 마이크로컨트롤러는 Cortex-M0+ 타입입니다(2014년 기준, 칩 스케일 패키지에서 1.6mm x 2mm로 가장 작은 것은 Kinetis KL03).[16]

6월 21일 2018년에는,"세계에서 가장 작은 컴퓨터의"또는 컴퓨터 장치는 2018년 Symposia VLSI기술에 미시간 대학 연구원과 전기 회로까지 서류를 "0.04mm3 16nW 무선과 Batteryless 슬과 ARMCortex-M0+(, RAM과 무선 송신기와 수신기에 기반한 태양 전지)–에 따라 – 발표되었다.n통합 Cortex-M0+ 프로세서를 탑재한 sor 시스템 및 세포 온도 측정을 위한 광통신."이 장치는 몇 달 전인 2018년 3월 IBM의 세계 기록 크기 컴퓨터의 10분의 1 크기로 소금 한 알보다 작습니다.

코텍스-M1

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv6-M |

| 명령 집합 | 엄지 1(대부분), 엄지 2 (일부) |

Cortex-M1은 FPGA 칩에 로드되도록 특별히 설계된 최적화된 코어입니다.

Cortex-M1 코어의 주요 특징은 다음과 같습니다.[4]

- ARMv6-M 아키텍처[9]

- 3단 파이프라인

- 명령 집합:

- 엄지 1(대부분), CBZ, CBNZ, IT가 없습니다.

- 썸-2(일부), BL, DMB, DSB, ISB, MRS, MSR만.

- 32비트 하드웨어 정수에 32비트 결과를 곱합니다.

- 1 ~ 32 인터럽트 및 NMI.

실리콘 옵션:

- 하드웨어 정수 곱셈 속도: 3 또는 33 사이클.

- TCM (옵션) : 0 ~1 MB 명령-TCM, 0 ~1 MB 데이터-TCM (옵션의 ECC 탑재)

- 외부 인터럽트: 0, 1, 8, 16, 32.

- 디버깅: none, reduced, full.

- 데이터 엔디안: 리틀 엔디안 또는 BE-8 빅 엔디안.

- OS 확장: 있음 또는 없음.

칩스

다음 벤더는 FPGA 칩의 소프트코어로 Cortex-M1을 지원하고 있습니다.

- 알테라 사이클론 II, 사이클론 III, 스트래틱스 II, 스트래틱스 III

- 고윈 M1

- Actel/Microsemi/Microchip Fusion, IGLU/e, ProASIC3L, ProASIC3/E

- Xilinx Spartan-3, Virtex-2, Virtex-3, Virtex-4, Artix-7[18]

코텍스-M3

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv7-M |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태(일부), 분할 |

Cortex-M3 코어의 주요 특징은 다음과 같습니다.[5][19]

- ARMv7-M 아키텍처[10]

- 지점 투기가 있는 3단계 파이프라인

- 명령 집합:

- 엄지 1(완료)

- 엄지 2(완료).

- 32비트의 하드웨어 정수는 32비트 또는 64비트의 결과와 곱합니다.서명 또는 부호 없이 곱셈 후에 덧셈 또는 뺄셈합니다.32비트의 곱셈은 1사이클이지만 64비트의 곱셈 및 MAC 명령에는 추가 사이클이 필요합니다.

- 32비트 하드웨어 정수 분할(2~12 사이클).

- 포화 산술 지원.

- 1~240 인터럽트 및 NMI.

- 12 사이클 인터럽트 지연

- 통합 sleep 모드

실리콘 옵션:

- 옵션인 Memory Protection Unit(MPU): 0 또는 8 지역

칩스

다음 마이크로컨트롤러는 Cortex-M3 코어를 기반으로 합니다.

- ABOV AC33Mx128, AC33Mx064

- Actel/Microsemi/Microchip SmartFusion, SmartFusion 2(FPGA)

- 아날로그 디바이스 ADUCM360, ADUCM361, ADUCM3029

- Broadcom Wi-Fi 칩 BCM4319XKUBG

- Cypress PSoC 5000, 5000LP, FM3

- Holtek HT32F

- Infineon TLE9860, TLE987x

- 마이크로칩(Atmel) SAM 3A, 3N, 3S, 3U, 3X

- NXP LPC1300, LPC1700, LPC1800

- 점등 반도체 Q32M210

- Realtek RTL8710

- Silicon Labs Precision 32

- Silicon Labs ( Energy Micro ) EFM32 Tiny, Gecko, Leopard, Giant

- ST STM32 F1, F2, L1, W

- TDK-Micronas HVC4223F

- Texas Instruments F28, LM3, TMS470, OMAP4, SimpleLink Wireless MCU(CC1310 Sub-GHz 및 CC2650 BLE+ZigBee+6LoWPAN)

- 도시바 TX03

다음 칩에는 보조 코어로 Cortex-M3가 있습니다.

- Apple A9(내장 M9 모션 공동 프로세서로서의 Cortex-M3)

- CSR Quatro 5300 (코프로세서로서의 Cortex-M3)

- Samsung Exynos 7420 (DVS 마이크로 컨트롤러로서의 [20]Cortex-M3)

- Texas Instruments F28, LM3, TMS470, OMAP 4470(Cortex-A9 x 1 + Cortex-M3 x 2 )

- XMOS XS1-XA (xCORE x 7 + Cortex-M3 x 1 )

다음 FPGA에는 Cortex-M3 코어가 포함되어 있습니다.

- Microsemi SmartFusion 2 SoC

다음 벤더는 FPGA 칩의 소프트코어로 Cortex-M3를 지원하고 있습니다.

- 알테라 사이클론 II, 사이클론 III, 스트래틱스 II, 스트래틱스 III

- Xilinx Spartan-3, Virtex-2, Virtex-3, Virtex-4, Artix-7[21]

코텍스-M4

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv7E-M |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태, DSP, 분할, FPU(SP) |

개념적으로 Cortex-M4는 Cortex-M3와 DSP 명령 및 옵션 부동소수점 유닛(FPU)입니다.FPU를 가진 코어는 Cortex-M4F로 알려져 있습니다.

Cortex-M4 코어의 주요 특징은 다음과 같습니다.[6]

실리콘 옵션:

- 옵션의 부동소수점 유닛(FPU): 단정도 IEEE-754에 준거.이것은 FPv4-SP 확장이라고 불립니다.

- 옵션 메모리 보호 유닛(MPU): 0 또는 8 지역

칩스

다음 마이크로컨트롤러는 Cortex-M4 코어를 기반으로 합니다.

- 아날로그 디바이스 ADSP-CM40x

- 마이크로칩(Atmel) SAM 4L, 4N, 4S

- NXP(프리스케일) Kinetis K, W2

- Texas Instruments SimpleLink Wi-Fi CC32xx, CC32xxMOD

다음 마이크로 컨트롤러는 Cortex-M4F(M4 + FPU) 코어를 기반으로 합니다.

- 아날로그 디바이스 ADUCM4050

- Cypress 6200(Cortex-M4F×1+Cortex-M0+×1), FM4

- 인피니온 XMC4000

- 막심 다윈

- 마이크로칩(Atmel) SAM4C(듀얼코어: Cortex-M4F×1+Cortex-M4×1), SAM4E, SAMG5, SAMD5/E5x

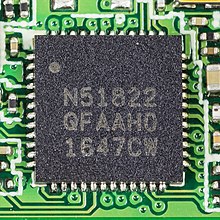

- 노르딕 nRF52

- Nuvoton NuMicro M480

- NXP LPC4000, LPC4300(Cortex-M4F×1+Cortex-M0×1), LPC54000

- NXP(프리스케일) Kinetis K, V3, V4

- 르네사스 S3, S5, S7, RA4, RA6

- Silicon Labs ( Energy Micro

- ST STM32 F3, F4, L4, L4+, G4, WB(Cortex-M4F 1개 + Cortex-M0+ 1개)

- Texas Instruments LM4F, TM4C, MSP432, CC13x2R, CC1352P, CC26x2R

- 도시바 TX04

다음 칩에는 보조 코어로 Cortex-M4 또는 M4F가 있습니다.

- NXP(Freescale) 바이브리드 VF6(Cortex-A5×1+Cortex-M4F×1

- NXP(Freescale) i.MX 6 SoloX(Cortex-A9×1+Cortex-M4F×1)

- NXP(Freescale) i.MX 7 Solo/Dual (1개 또는 2개의 Cortex-A7 + 1개의 Cortex-M4F)

- NXP(Freescale) i.MX 8 (2개의 Cortex-A72 + 4개의 Cortex-A53 + 2개의 Cortex-M4F)

- NXP(Freescale) i.MX 8M 및 8M Mini (Cortex-A53 x 4 + Cortex-M4F x 1 )

- NXP(Freescale) i.MX 8X (4개의 Cortex-A35 + 1개의 Cortex-M4F)

- ST STM32MP1 (1개 또는 2개의 Cortex-A7 + 1개의 Cortex-M4)

- Texas Instruments OMAP 5 (2개의 Cortex-A15s + 2개의 Cortex-M4)

- Texas Instruments Sitara AM5700 (1개 또는 2개의 Cortex-A15s + 2개의 Cortex-M4를 이미지 처리 장치로 사용)

코텍스-M7

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv7E-M |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태, DSP, 분할, FPU(SP 및 DP) |

Cortex-M7은 구형 Cortex-M4보다 전력 효율이 거의 2배 높은 고성능 코어입니다.분기 예측 기능이 있는 6단계 슈퍼칼라 파이프라인과 옵션 부동소수점 유닛을 갖추고 있어 단정밀 및 옵션인 2정밀 [22][23]연산이 가능합니다.명령 및 데이터 버스는 이전 32비트 버스보다 64비트 폭까지 확장되었습니다.코어에 FPU가 포함되어 있으면 Cortex-M7F라고 하며, 그렇지 않으면 Cortex-M7이라고 합니다.

Cortex-M7 코어의 주요 특징은 다음과 같습니다.[7]

- ARMv7E-M 아키텍처

- 지점 투기가 있는 6단계 파이프라인모든 ARM Cortex-M 코어 중 가장 길다.

- 명령 집합:

- 1~240 인터럽트 및 NMI.

- 12 사이클 인터럽트 지연

- 통합 sleep 모드

실리콘 옵션:

- 옵션의 부동소수점 유닛(FPU): (단정밀) 또는 (단정밀 및 배정밀), 모두 IEEE-754-2008에 준거.이것은 FPv5 확장이라고 불립니다.

- 옵션 CPU 캐시: 0~64KB 명령 캐시, 0~64KB 데이터 캐시, 각각 옵션 ECC 탑재.

- TCM (옵션) : 0 ~16 MB 명령-TCM, 0 ~16 MB 데이터-TCM (옵션의 ECC 탑재)

- 옵션 메모리 프로텍션 유닛(MPU): 8 또는 16 지역

- 옵션의 임베디드 트레이스 매크로 셀(ETM): 명령 전용 또는 명령과 데이터.

- 슬립 모드용 옵션 유지 모드(암 전원 관리 키트 포함)

칩스

다음 마이크로컨트롤러는 Cortex-M7 코어를 기반으로 합니다.

코텍스-M23

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv8-M 기준선 |

| 명령 집합 | 엄지 1(대부분), 엄지 2(일부), 분할, 트러스트 존 |

Cortex-M23 core는 2016년 10월에[24] 발표되었으며 2015년 [25]11월에 발표된 새로운 ARMv8-M 아키텍처를 기반으로 합니다.개념적으로 Cortex-M23은 Cortex-M0+ 및 정수 분할 명령 및 TrustZone 보안 기능과 유사하며 2단계 명령 파이프라인이 있습니다.

Cortex-M23 코어의 주요 특징은 다음과 같습니다.[8][24]

- ARMv8-M 베이스라인 [15]아키텍처

- 2단계 파이프라인(Cortex-M0+와 유사)

- Trust Zone 보안 지침.(M23/M33/M35P에서만 사용 가능)

- 32비트 하드웨어 정수 분할(17 또는 34 사이클).(M0/M0+/M1에서는 이용 불가) (기타 모든 코어에서의 분할 속도보다 느림)

- 스택 제한 경계.(SAU 옵션에서만 사용 가능) (M23/M33/M35P에서 사용 가능)

실리콘 옵션:

- 하드웨어 정수 곱셈 속도: 1 또는 32 사이클.

- 하드웨어 정수 분할 속도: 최대 17 또는 34 사이클.제수에 따라 명령이 더 적은 사이클로 완료될 수 있습니다.

- 옵션 메모리 보호 유닛(MPU): 0, 4, 8, 12, 16 지역.

- 옵션의 보안 어트리뷰션 유닛(SAU): 0, 4, 8 지역.

- 싱글 사이클 I/O 포트(M0+/M23에서 사용 가능).

- Micro Trace Buffer(MTB)(M0+/M23/M33/M35P에서 사용 가능).

칩스

다음 마이크로컨트롤러는 Cortex-M23 코어를 기반으로 합니다.

코텍스-M33

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv8-M 메인라인 |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태, DSP, 분할, FPU(SP), Trust Zone, 코프로세서 |

Cortex-M33 코어는 2016년 10월에[24] 발표되었으며 2015년 [25]11월에 발표된 새로운 ARMv8-M 아키텍처를 기반으로 합니다.개념적으로 Cortex-M33은 Cortex-M4 및 Cortex-M23의 교배와 유사하며 3단계 명령 파이프라인이 있습니다.

Cortex-M33 코어의 주요 특징은 다음과 같습니다.[12][24]

- ARMv8-M 메인라인 [15]아키텍처

- 3단 파이프라인

- Trust Zone 보안 지침.(M23/M33/M35P에서만 사용 가능)

- 32비트 하드웨어 정수 분할(최대 11사이클)(M0/M0+/M1에서는 사용 불가)

- 스택 제한 경계.(SAU 옵션에서만 사용 가능) (M23/M33/M35P에서 사용 가능)

실리콘 옵션:

- 옵션의 부동소수점 유닛(FPU): 단정도 IEEE-754에 준거.이것은 FPv5 확장이라고 불립니다.

- 옵션 메모리 보호 유닛(MPU): 0, 4, 8, 12, 16 지역.

- 옵션의 보안 어트리뷰션 유닛(SAU): 0, 4, 8 지역.

- Micro Trace Buffer(MTB)(M0+/M23/M33/M35P에서 사용 가능).

칩스

다음 마이크로컨트롤러는 Cortex-M33 코어를 기반으로 합니다.

- 아날로그 디바이스 ADUCM410, ADUCM420

- 대화상자 DA1469x

- Giga Device GD32E50x, GD32W515

- Nordic nRF91, nRF5340

- NXP LPC5500, iMX RT600

- 르네사스 RA4, RA6

- ST STM32 L5, U5

- Silicon Labs Wireless Gecko 시리즈 2

Cortex-M35P

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv8-M 메인라인 |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태, DSP, 분할, FPU(SP), Trust Zone, 코프로세서 |

Cortex-M35P 코어는 2018년 5월에 발표되었습니다.개념적으로는 Cortex-M33 코어이며, 새로운 명령 캐시와 더불어 ARM SecurCore 패밀리에서 빌린 새로운 변조 방지 하드웨어 개념 및 구성 가능한 패리티 및 ECC [26]기능을 갖추고 있습니다.

현재 Cortex-M35P의 기술 참조 매뉴얼이 발표될 때까지 제한된 공개 정보를 이용할 수 있습니다.

칩스

다음 마이크로컨트롤러는 Cortex-M35P 코어를 기반으로 합니다.

- 2021년 7월 현재 칩은 발표되지 않았다.

코텍스-M55

| 아키텍처 및 분류 | |

|---|---|

| 마이크로아키텍처 | ARMv8.1-M 메인라인 헬륨 |

| 명령 집합 | 엄지-1, 엄지-2, 포화 상태, DSP, 분할, FPU(VFPv5) Trust Zone, 코프로세서, MBE |

Cortex-M55 코어는 2020년 2월에 발표되었으며, 앞서 2019년 2월에 발표된 Armv8.1-M 아키텍처를 기반으로 한다.4단계 명령 파이프라인도 갖추고 있습니다.

Cortex-M55 코어의 주요 특징은 다음과 같습니다.

- ARMv8.1-M 메인라인/헬륨 아키텍처.[15]

- 4단 파이프라인

- 스택 제한 경계(SAU 옵션에서만 사용 가능).

실리콘 옵션:

- 헬륨(M-프로파일 벡터 익스텐션, MVE

- 단정도 부동소수점 및 배정도 부동소수점

- Digital Signal Processing(DSP; 디지털 신호 처리) 확장 지원

- Trust Zone 보안 확장 지원

- 안전 및 신뢰성(RAS) 지원

- 코프로세서 지원

- 0, 4, 8, 12 또는 16 리젼의 시큐어 MPU 및 비시큐어 MPU

- 0, 4, 또는 8개 지역에서의 SAU

- 4KB, 8KB, 16KB, 32KB, 64KB 크기의 명령 캐시

- 4KB, 8KB, 16KB, 32KB, 64KB 크기의 데이터 캐시

- 캐시 및 TCM 상의 ECC

- 1회 인터럽트

- 3~8의 예외 priority 비트

- 내부 및 외부 WIC 옵션, CTI, ITM 및 DWT 옵션

- ARM 커스텀 순서(향후 릴리즈에서 이용 가능)

칩스

- Alif Semiconductor Ensemble 및 Crescendo MCU 패밀리는 각각 Ethos-U55 NPU와 짝을 이룬 싱글 또는 듀얼 Cortex-M55 코어를 제공합니다.

개발 도구

문서

ARM 칩에 대한 설명서는 광범위합니다.과거에는 8비트 마이크로컨트롤러 문서가 일반적으로 하나의 문서에 포함되었지만 마이크로컨트롤러가 발전함에 따라 마이크로컨트롤러 지원에 필요한 모든 것이 갖추어졌습니다.ARM 칩용 문서 패키지는 일반적으로 IC 제조원 및 CPU 코어 벤더(Arm Holdings)의 문서 모음으로 구성됩니다.

일반적인 하향식 문서 트리는 다음과 같습니다.

- 문서 트리(위에서 아래로)

- IC 제조원 웹사이트.

- IC 제조사의 마케팅 슬라이드.

- 정확한 물리 칩에 관한 IC 제조원의 데이터 시트.

- 일반적인 주변기기류 및 물리 칩 패밀리의 측면을 설명하는 IC 제조원 참조 매뉴얼.

- ARM 코어 웹사이트

- ARM 코어 범용 사용자 가이드

- ARM 코어 기술 참조 매뉴얼.

- ARM 아키텍처 참조 매뉴얼

IC 제조업체에는 평가판 사용자 설명서, 응용 프로그램 노트, 시작 가이드, 소프트웨어 라이브러리 문서, 에라타 등의 추가 문서가 있습니다.공식 암 문서에 대한 링크는 외부 링크 섹션을 참조하십시오.

「 」를 참조해 주세요.

레퍼런스

- ^ ARM Cortex-M 웹사이트; arm.com

- ^ a b c d Cortex-M0 기술 참조 매뉴얼 개정판 r0p0; 암 홀딩스.

- ^ a b c d e Cortex-M0+ 기술 참조 매뉴얼 개정판 r0p1, 암 홀딩스.

- ^ a b c d Cortex-M1 r1p0 기술 참조 매뉴얼, 암 홀딩스.

- ^ a b c d Cortex-M3 r2p1 기술 참조 매뉴얼, 암 홀딩스.

- ^ a b c d Cortex-M4 기술 참조 매뉴얼 개정판 r0p1, 암 홀딩스.

- ^ a b c d e Cortex-M7 기술 참조 매뉴얼, 암 홀딩스.

- ^ a b c d Cortex-M23 r1p0 기술 참조 매뉴얼, 암 홀딩스.

- ^ a b c d e f g h i j k l m n o p q r "ARMv6-M Architecture Reference Manual". Arm Holdings. 29 June 2018. Archived from the original on 22 January 2021.

- ^ a b c d e f g h i j k l m n o p q r "ARMv7-M Architecture Reference Manual". Arm Holdings. 15 February 2021.

- ^ a b c d Cortex-M3 Embedded Software Development, App Note 179, Arm Holdings.

- ^ a b c Cortex-M33 r0p3 기술 참조 매뉴얼, 암 홀딩스.

- ^ a b c Cortex-M 시스템 설계 키트, 암 홀딩스.

- ^ a b c d e f g h i j ARM Cortex-M 프로그래밍 가이드 메모리 장벽 지침; 섹션 3.6 시스템 구현 요건; AppNote 321; arm.com

- ^ a b c d e f g h ARMv8-M 아키텍처 레퍼런스 매뉴얼, Arm Holdings.

- ^ Fingas, Jon (25 February 2014). "Freescale makes the world's smallest ARM controller chip even tinier". Retrieved 2 October 2014.

- ^ GOWIN Semiconductor가 ARM Design Start에 참가하여 FPGA 제품 패밀리용으로 ARM Cortex-M1 프로세서를 무료로 제공

- ^ Cortex-M1 DesignStart FPGA XilinxEdition

- ^ Sadasivan, Shyam. "An Introduction to the ARM Cortex-M3 Processor" (PDF). Arm Holdings. Archived from the original (PDF) on July 26, 2014.

- ^ "The Samsung Exynos 7420 Deep Dive - Inside a Modern 14nm SoC". AnandTech. Retrieved 2015-06-15.

- ^ Cortex-M3 DesignStart FPGA XilinxEdition

- ^ "Cortex-M7 Processor". Arm Holdings. Retrieved 2014-09-24.

- ^ "ARM Supercharges MCU Market with High Performance Cortex-M7 Processor". arm.com (Press release). September 24, 2014.

- ^ a b c d 새로운 ARM Cortex-M 프로세서는 안전한 IoT를 위한 차세대 업계 표준인 Arm Holdings를 2016년 10월 25일에 제공합니다.

- ^ a b ARMv8-M 아키텍처 스마트 임베디드 디바이스의 보안 심플화, Arm Holdings, 2015년 11월 10일

- ^ "Cortex-M35P Processor". Arm Holdings. Retrieved 2018-06-04.

추가 정보

- 어셈블리 언어 및 C, 제3판, Yifeng Zhu, 738페이지, 2017년, ISBN 978-098262660을 탑재한 임베디드 시스템.

- Cortex-M 프로세서 패밀리 설계 가이드, 제2판, Trevor Martin, 490페이지, 2016년, ISBN 978-0081006290.

- 임베디드 애플리케이션용 ARM 어셈블리, 제3판, Daniel Lewis, 318페이지, 2017년, ISBN 978-1543908046.

- ARM Cortex-M0 및 Cortex-M0+ 프로세서 최종 가이드, 제2판, Joseph Yiu; 784페이지, 2015년, ISBN 978-0128032770.

- ARM Cortex-M3 및 Cortex-M4 프로세서 최종 가이드, 제3판, Joseph Yiu, 600페이지, 2013년, ISBN 978-0124080829.

- ARM Cortex-M4를 사용한 디지털 신호 처리 및 응용 프로그램, 제1판, Donald Reay, 250페이지, 2014년, ISBN 978-118859049.

- 임베디드 시스템: ARM Cortex-M 마이크로컨트롤러 소개; 제5판, Jonathan Valvano; 506페이지, 2012; ISBN 978-1477508992.

- 어셈블리 언어 프로그래밍: ARM Cortex-M3, 제1판, Vincent Mahout, 256페이지, 2012년, ISBN 978-1848213296.

외부 링크

- ARM Cortex-M 공식 문서

- ARM Cortex-M 공식 웹사이트

- 초보자용 Cortex-M – arm.com

- ARMv8-M 보안 확장– arm.com

- Cortex Microcontroller Software Interface Standard (CMSIS)– arm.com

팔

핵심조금

폭팔

웹 사이트ARM 범용

사용자 가이드ARM 기술

참조 매뉴얼ARM 아키텍처

참조 매뉴얼코텍스-M0 32 링크 링크 링크 ARMv6-M Cortex-M0+ 32 링크 링크 링크 ARMv6-M 코텍스-M1 32 링크 링크 링크 ARMv6-M 코텍스-M3 32 링크 링크 링크 ARMv7-M 코텍스-M4 32 링크 링크 링크 ARMv7E-M 코텍스-M7 32 링크 링크 링크 ARMv7E-M 코텍스-M23 32 링크 링크 링크 ARMv8-M 코텍스-M33 32 링크 링크 링크 ARMv8-M Cortex-M35P 32 링크 미정 미정 ARMv8-M 코텍스-M55 32 링크 미정 미정 ARMv8.1-M

- 퀵 레퍼런스 카드

- 이행

- 8051에서 Cortex-M3로의 이행– arm.com

- PIC에서 Cortex-M3로의 이행– arm.com

- ARM7로부터의 이행TDMI에서 Cortex-M3로– arm.com

- Cortex-M4에서 Cortex-M7로의 이행– keil.com

- 다른.