슈미트 트리거

Schmitt trigger전자공학에서 슈미트 트리거는 비교기 또는 차동증폭기의 비반전 입력에 양의 피드백을 가함으로써 히스테리시스가 구현되는 비교기 회로입니다.아날로그 입력 신호를 디지털 출력 신호로 변환하는 능동 회로입니다.회로는 입력을 충분히 변경하여 변경을 트리거할 때까지 출력이 값을 유지하므로 트리거라는 이름이 붙습니다.비반전 설정에서는 입력이 선택한 임계값보다 높을 경우 출력이 높아집니다.입력이 다른(낮은) 선택된 임계값보다 낮으면 출력이 낮으며, 입력이 두 레벨 사이에 있으면 출력이 값을 유지합니다.이 듀얼 임계값 액션은 히스테리시스라고 불리며 슈미트트리거가 메모리를 보유하여 쌍안정 멀티바이버레이터(래치 또는 플립플롭)로 동작할 수 있음을 의미합니다.두 종류의 회로 사이에는 밀접한 관계가 있습니다. 즉, 슈미트 트리거를 래치로 변환하고 래치를 슈미트 트리거로 변환할 수 있습니다.

슈미트 트리거 장치는 일반적으로 디지털 회로에서 사용되는 신호, 특히 스위치의 기계적 접점 바운스에서 노이즈를 제거하기 위해 신호 조절 애플리케이션에 사용됩니다.또한 폐루프 네거티브 피드백 구성에서 함수 발생기 및 스위칭 전원 공급기에 사용되는 완화 발진기를 구현하기 위해 사용됩니다.

발명.

슈미트 방아쇠는 대학원생 시절인 1934년 미국인 과학자 오토 H [1]슈미트에 의해 발명되었으며, 나중에 그의 박사 논문(1937)에서 열전자 [2]방아쇠로 묘사되었다.그것은 오징어 [2]신경의 신경충격 전파에 대한 슈미트의 연구의 직접적인 결과였다.

실행

기본 아이디어

히스테리시스가 있는 회로는 양의 피드백을 기반으로 합니다.루프 게인이 1개 이상 되도록 양의 피드백을 가함으로써 액티브 회로를 슈미트 트리거로 동작시킬 수 있습니다.양의 피드백은 출력 전압의 일부를 입력 전압에 추가하여 도입됩니다.이러한 회로에는 비교기 역할을 하는 증폭기 외에 감쇠기(오른쪽 그림의 B 상자)와 가산기(안쪽에 "+"가 있는 원)가 포함되어 있습니다.이 일반적인 아이디어를 구현하기 위한 세 가지 구체적인 기술이 있습니다.그 중 처음 두 가지는 일반적인 양의 피드백 시스템의 이중 버전(시리즈 및 병렬)입니다.이러한 구성에서 출력 전압은 '임계값 감소' 또는 '회로 입력 전압 증가'를 통해 비교기의 유효 차분 입력 전압을 증가시킵니다. 임계값 및 메모리 특성은 하나의 소자에 통합되어 있습니다.세 번째 기술에서는 문턱값과 메모리 특성이 분리된다.

동적 임계값(직렬 피드백): 입력 전압이 어떤 방향으로 임계값을 초과하면 회로 자체가 자체 임계값을 반대 방향으로 변경합니다.이를 위해 임계값에서 출력 전압의 일부를 뺍니다(입력 전압에 전압을 추가하는 것과 동일).따라서 출력은 임계값에 영향을 미치며 입력 전압에는 영향을 주지 않습니다.이러한 회로는 입력이 반전 입력에 연결되고 출력이 비반전 입력에 연결되는 '직렬 포지티브 피드백'이 있는 차동 앰프에 의해 구현됩니다.이 배치에서는 감쇠와 합계가 분리됩니다.분압기는 감쇠기로, 루프는 단순한 직렬 전압 섬머로 작동합니다.전형적인 트랜지스터 이미터 결합 슈미트 트리거, op-amp 반전 슈미트 트리거 등이 이에 해당합니다.

수정된 입력 전압(병렬 피드백): 입력 전압이 어떤 방향으로 임계값을 초과하면 회로가 동일한 방향으로 입력 전압을 변경합니다(이제 출력 전압의 일부를 입력 전압에 직접 추가).따라서 출력은 입력 전압을 증가시키며 임계값에는 영향을 주지 않습니다.이러한 회로는 입력 및 출력 소스가 저항을 통해 입력에 연결되는 '병렬 양의 피드백'을 가진 단일 엔드 비반전 증폭기에 의해 구현될 수 있습니다.두 개의 저항은 감쇠와 합계를 모두 포함하는 가중 병렬 여름을 형성합니다.예를 들어 덜 친숙한 수집기-베이스 결합 슈미트 트리거, op-amp 비반전 슈미트 트리거 등이 있습니다.

음의 저항을 나타내는 일부 회로 및 소자도 유사한 방식으로 작동할 수 있습니다. 음의 임피던스 변환기(NIC), 네온 램프, 터널 다이오드(예: 제1 사분면에 "N"자 모양의 전류-전압 특성이 있는 다이오드).마지막 경우 입력이 진동하면 입력이 상승 및 하강 스위칭 임계값을 통과할 때 다이오드가 "N"의 한 상승 레그에서 다른 상승 레그로 이동하고 다시 되돌아갑니다.

이 경우 2개의 다른 단방향 임계값이 쌍안정 멀티바이버레이터(래치) 또는 플립플랍을 구동하는2개의 다른 오픈루프 컴퍼레이터(히스테리시스 없음)에 할당됩니다.트리거는 입력 전압이 하이 임계값으로 넘어갈 때 하이로 전환되고 입력 전압이 로우 임계값으로 넘어갈 때 로우로 전환됩니다.이번에도 긍정적인 피드백이 있지만 지금은 메모리 셀에만 집중되어 있습니다.예를 들어 555 타이머와 스위치의 디바운스 [3]회선이 있습니다.

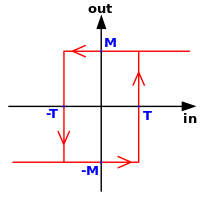

회로 다이어그램에서 슈미트 트리거의 기호는 이상적인 이력 곡선을 나타내는 기호가 내부에 있는 삼각형입니다.

트랜지스터 슈미트 트리거

기존의 이미터 결합 회로

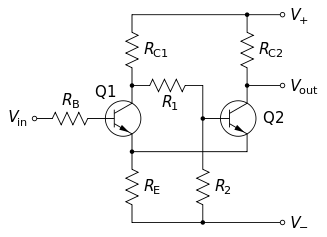

원래 슈미트 트리거는 전환 가능한 상부 레그(수집기 저항C1 R 및 RC2)와 안정된 하부 레그(RE)를 가진 분압기에 의해 구현되는 동적 임계값 아이디어를 기반으로 합니다.Q1은 반전(Q1 베이스) 입력과 비반전(Q1 이미터) 입력으로 이루어진 차분 입력(Q1 베이스-이미터 접합)과의 비교기로 기능한다.입력 전압은 반전 입력에 인가되고, 분압기의 출력 전압은 비반전 입력에 인가되어 임계값을 결정합니다.컴퍼레이터 출력은 전압분할기 R-R을12 통해 두 번째 공통 컬렉터 스테이지 Q2(이미터 팔로어)를 구동합니다.이미터 결합 트랜지스터 Q1 및 Q2는 실제로 분압기의 위쪽 레그 위를 전환하여 임계값을 다른 방향으로 변경하는 전자 이중 스로우 스위치를 구성합니다.

이 구성은 변환 프로세스를 강제하는 비반전 입력(Q2 베이스)과 출력(Q1 콜렉터) 사이에 직렬 양의 피드백이 있는 차동 증폭기로 간주할 수 있습니다.또, 이미터 저항E R에 의해서 발생하는 부피드백도 작아집니다.양의 피드백이 음의 것을 지배하고 히스테리시스를 얻기 위해 두 집전체 저항 사이의 비율을 R > R로C2 선택한다C1.따라서 Q1을 켜면 Q2를 켜는 경우보다 R을 통과하는E 전류가 적고 전압 강하가 줄어듭니다.그 결과 회로는 접지와 관련하여 2개의 다른 문턱값을 갖게 됩니다−(이미지에서는 V).

작동

초기 상태오른쪽에 표시된 NPN 트랜지스터의 경우 Q1 베이스-이미터 접합부가 역바이어스 되어 Q1이 전도하지 않도록 입력 전압이 공유 이미터 전압(구체성을 위한 높은 임계값)보다 낮다고 가정합니다.Q2 기본 전압은 Q2가 전도되고 트리거 출력이 로우 상태가 되도록 언급된 분할기에 의해 결정됩니다.2개의 저항C2 R과E R은 상한 임계값을 결정하는 또 다른 분압기를 형성합니다.V을 무시하면BE 상한 임계값은 약

- } = {} + }}} {

출력 전압이 낮지만 접지보다 훨씬 높습니다.이는 상한 임계값과 거의 같으며 다음 디지털 회선의 논리 0이 될 만큼 낮지 않을 수 있습니다.이 경우 트리거 회로에 이어 추가 시프트 회로가 필요할 수 있습니다.

높은 문턱을 넘고 있다.입력전압(Q1 베이스전압)이 이미터저항RE(고임계값)의 전압보다 약간 상승하면 Q1이 도통을 시작합니다.이제 분압기가 낮은 Q2 기본 전압을 제공하기 때문에 콜렉터 전압이 내려가고 Q2가 차단되기 시작합니다.공통 이미터 전압은 이 변화에 따라 저하되므로 Q1의 전도성이 높아집니다.전류가 회로의 오른쪽 레그에서 왼쪽 레그로 조향을 시작합니다.Q1은 전도성이 높지만 R을 통과하는E 전류는C2 적습니다C1(R > R 이후). 이미터 전압은 계속 떨어지고 유효 Q1 베이스 이미터 전압은 계속 증가합니다.이 눈사태와 같은 프로세스는 Q1이 완전히 켜지고 Q2가 꺼질 때까지 계속됩니다.트리거가 하이 상태로 전환되고 출력(Q2 수집기) 전압이 V+에 가깝습니다.이제 2개의 저항C1 R과E R이 하한 임계값을 결정하는 분압기를 형성합니다.그 가치는 대략

- L + C + {\ } = { {} + R_{\{C1}}}} {}}} {{}}}}}}}}}}}}}}}} {{V}.

하한 임계값을 넘어갑니다.트리거가 High 상태에 있는 상태에서 입력 전압이 충분히 낮아지면(Low Threshold 이하), Q1이 컷오프를 시작합니다.콜렉터 전류가 감소하기 때문에 공유 이미터 전압이 약간 낮아지고 Q1 콜렉터 전압이 크게 상승합니다.R-R12 분압기는 이 변화를 Q2 기본 전압으로 전달하고 도체를 시작합니다.R 전체의E 전압이 상승하여 같은 눈사태와 같은 방법으로 Q1 베이스 이미터 전위가 더욱 감소하며 Q1은 도체를 정지합니다.Q2가 완전히 온(포화)되어 출력 전압이 다시 낮아집니다.

바리에이션

비반전 회로기존의 비반전 슈미트 트리거는 Q2 수집기 대신 이미터에서 V를 취함으로써out 반전 트리거로 전환할 수 있습니다.이 구성에서는 출력전압은 동적 임계값(공유 이미터 전압)과 동일하며 양쪽 출력레벨은 공급레일에서 떨어져 있습니다.또 다른 단점은 부하에 의해 임계값이 변경되기 때문에 충분히 높아야 한다는 것입니다.베이스 저항B R은 Q1 베이스-이미터 접합을 통한 입력 전압이 이미터 전압에 미치는 영향을 방지하기 위해 필수적입니다.

직접 결합 회로회로를 단순화하기 위해 Q1 컬렉터를 Q2 베이스에 직접 연결하는 R-R2 분압기를1 생략할 수 있습니다.입력 전압 소스가 직접 Q1의 [4]베이스를 구동하도록 기본 저항B R도 생략할 수 있습니다.이 경우 공통 이미터 전압과 Q1 컬렉터 전압은 출력에 적합하지 않습니다.입력전압이 상한 임계값을 초과하여 Q1이 포화되면 베이스-이미터 접합부가 전방 바이어스되어 입력전압 변동을 직접 이미터로 전송하므로 Q2 컬렉터만 출력으로 사용해야 합니다.그 결과 공통 이미터 전압과 Q1 컬렉터 전압이 입력 전압을 따릅니다.이 상황은 일반적으로 과구동 트랜지스터 차동 증폭기 및 ECL 게이트에서 발생합니다.

콜렉터 베이스 커플링 회로

모든 래치와 마찬가지로 기본 컬렉터 베이스 결합 쌍안정 회로는 히스테리시스를 가진다.따라서 추가 기본 저항 R을 입력 중 하나에 연결하여 슈미트 트리거로 변환할 수 있습니다(그림의 Q1 기준).2개의 저항 R 및4 R은 출력(Q2 컬렉터) 전압과 입력 전압을 합한 병렬 전압 섬머(위의 블록 다이어그램의 원)를 형성하고 싱글 엔드 트랜지스터 "비교기" Q1을 구동합니다.베이스 전압이 문턱값(VBE0 65 0.65V)을 넘으면 Q2 컬렉터 전압의 일부가 입력 전압과 같은 방향으로 가산됩니다.따라서 출력은 병렬 양의 피드백에 의해 입력 전압을 변경하며 임계값(베이스 이미터 전압)에는 영향을 주지 않습니다.

이미터결합회선과 컬렉터결합회선의 비교

이미터 결합 버전은 입력 전압이 높은 임계값보다 훨씬 낮을 때 입력 트랜지스터가 역편향되므로 트랜지스터가 확실히 차단됩니다.회로를 구현하기 위해 게르마늄 트랜지스터가 사용되었을 때 중요했고 이 장점이 게르마늄 트랜지스터의 인기를 결정지었다.입력 베이스-이미터 접점이 전방 바이어스일 때 이미터 저항이 전류를 제한하므로 입력 베이스 저항을 생략할 수 있습니다.

이미터 결합 슈미트트리거 논리 제로 출력 레벨이 충분히 낮지 않을 수 있으며 추가 출력 시프트 회로가 필요할 수 있습니다.콜렉터 결합 슈미트트리거는 논리 0에서 출력이 매우 낮습니다(거의 제로).

Op-amp 구현

슈미트 트리거는 일반적으로 연산 증폭기 또는 전용 [nb 2]비교기를 사용하여 구현됩니다.오픈루프 op-amp 및 컴퍼레이터는 아날로그 입력과 그 두 [nb 3]입력 사이의 전압차이의 부호를 추출하는 디지털 출력을 가진 아날로그 디지털 디바이스로 간주할 수 있다.양의 피드백은 출력 전압의 일부를 직렬 또는 병렬 방식으로 입력 전압에 추가하여 적용됩니다.op-amp 게인이 매우 높기 때문에 루프 게인 또한 충분히 높아 눈사태와 같은 과정을 제공한다.

비반전 슈미트 트리거

이 회로에서는 2개의 저항1 R, R이2 병렬전압 서머를 형성한다.출력 전압의 일부를 입력 전압에 추가하여 결과 전압이 접지 부근에 있을 때 발생하는 전환 중 및 전환 후에 전압을 증가시킵니다.이 병렬 양의 피드백은 R과2 R의 저항1 사이의 비율에 의해 제어되는 필요한 이력을 생성합니다.병렬 전압 여름의 출력은 싱글 엔드(접지에 대한 전압을 생성)이므로 회로에 차동 입력이 있는 앰프가 필요하지 않습니다.기존의 op-amp에는 차동 입력이 있기 때문에 반전 입력은 접지되어 기준점이 0V가 됩니다.

출력 전압은 항상 op-amp 입력 전압과 같은 부호를 가지지만 회로 입력 전압과 항상 같은 부호를 가지는 것은 아닙니다(두 입력 전압의 부호는 다를 수 있습니다).회로 입력 전압이 상한 임계값을 초과하거나 하한 임계값을 밑돌면 출력 전압은 회로 입력 전압과 같은 부호를 가집니다(회로는 반전되지 않음).비교기의 출력이 높은지 낮은지에 따라 다른 포인트로 전환되는 비교기와 같은 기능을 합니다.회로 입력 전압이 임계값 사이에 있으면 출력 전압이 정의되지 않고 마지막 상태에 따라 달라집니다(회로는 기본 래치 역할을 함).

예를 들어, Schmitt 트리거가 현재 하이 상태이면 출력은 양극 전원 공급 레일(+VS)에 있습니다.저항성 여름의 출력 전압+ V는 중첩 정리를 적용하여 구할 수 있습니다.

V=0이면+ 비교기가 전환됩니다.으로 R 2 - V { (전류 보존 원리를 적용하면 같은 결과를 얻을 수 있다.)따라서 출력을 전환하려면 {\의V가 s {\ {\ { { 아래로 떨어져야 합니다.비교기 출력이 -V로S 전환되면 임계값은 + 1 s {\가 되어하이로 돌아갑니다.따라서 이 회로는 트리거 레벨 1 2 s {\}}{V_{s을(를) 0을 중심으로 스위칭 대역을 생성합니다.출력이 켜졌다가 다시 꺼지려면 입력 전압이 밴드 상단에서 상승한 다음 밴드 하단 아래로 상승해야 합니다.R이 0 또는2 R이 무한인 경우(즉, 개방 회로), 대역은1 0폭으로 축소되며 표준 비교기로 작동합니다.전송 특성은 왼쪽 그림과 같습니다.임계값 T의 은 R R s(\ { {로 지정되며 출력 M의 최대값은 전원 레일입니다.

병렬 포지티브 피드백이 있는 회로의 고유한 특성은 입력 [citation needed]소스에 대한 영향입니다.음의 병렬 피드백(예를 들어 반전 증폭기)을 가진 회로에서 반전 입력의 가상 접지는 입력 소스를 op-amp 출력으로부터 분리한다.여기에서는 가상접지가 없고 R-R12 네트워크를 통해 입력소스에 정상op-amp 출력전압이 인가됩니다.op-amp 출력은 입력 소스를 통해 반대 전류를 통과시킵니다(입력 전압이 양이면 전류를 소스로 주입하고 음이면 소스에서 전류를 끌어옵니다).

정확한 임계값을 가진 실용적인 슈미트 트리거가 오른쪽 그림에 나와 있습니다.전송 특성은 이전 기본 설정과 완전히 동일한 형상을 가지며 임계값도 동일합니다.한편, 이전 예에서는 출력 전압이 전원 공급 장치에 따라 달라졌지만, 현재는 Zener 다이오드로 정의됩니다(단일 이중 양극 Zener 다이오드로 대체 가능).이 구성에서 출력 레벨은 적절한 Zener 다이오드를 선택하여 변경할 수 있으며, 이러한 레벨은 전원 변동에 내성이 있습니다(즉, 비교기의 PSRR을 증가시킵니다).저항3 R은 다이오드를 통해 전류를 제한하고 저항 R은4 비교기의 입력 누출 전류로 인한 입력 전압 오프셋을 최소화합니다(실제 op-amp의 한계 참조).

슈미트 트리거 반전

반전 버전에서는 감쇠와 합계를 분리한다.두 개의 저항1 R 및2 R은 "순수한" 감쇠기(분압기)로만 작동합니다.입력 루프는 출력 전압의 일부를 회로 입력 전압에 직렬로 추가하는 직렬 전압 섬머 역할을 합니다.이 일련의 양의 피드백은 R의 저항과1 전체 저항(R1 및2 R) 사이의 비율로 제어되는 필요한 이력을 생성합니다.op-amp 입력에 인가되는 유효 전압은 부동이므로 op-amp에 차동 입력이 있어야 합니다.

출력 전압이 이력 사이클을 벗어날 때(입력 전압이 상한 임계값을 초과하거나 하한 임계값을 밑돌 때) 항상 입력 전압과 반대 부호가 있기 때문에 회로 이름이 반전됩니다.그러나 입력 전압이 히스테리시스 사이클(하이 임계값과 로우 임계값 사이) 내에 있는 경우 회로는 반전될 뿐만 아니라 비반전될 수도 있습니다.출력 전압은 정의되지 않았으며 마지막 상태에 따라 달라지기 때문에 회로가 기본 래치처럼 작동합니다.

두 버전을 비교하기 위해 회로 동작은 위와 같은 조건에서 고려됩니다.슈미트 트리거가 현재 하이 상태인 경우 출력은 양극 전원 공급 레일(+VS)에 있습니다.분압기의 출력 전압+ V는 다음과 같습니다.

비교기는 V+ = V일 때in 전환됩니다. 출력을 하려면 {\in의 가 이 전압을 초과해야 합니다.비교기 출력이 -V로S 전환되면 은 - R 1 + 2 s {\- + }} {s가 되어 하이로 돌아갑니다.따라서 이 회로는 0을으로 ± +R 2 s { 2}} s}} {V_{s}} {을(를1) 바이어스 전압에 연결하여 왼쪽 또는 오른쪽으로 이동할 수 있습니다.출력이 꺼졌다가 다시 켜지려면 입력 전압이 밴드 상단에서 위로 올라간 다음 밴드 하단 아래로 올라야 합니다.R이 0(즉, 단락 회로) 또는2 R이 무한대인 경우1, 대역은 0폭으로 축소되어 표준 비교기로 동작합니다.

병렬 버전과 달리 이 회로는 고op-amp 입력 차동 임피던스에 의해 소스가 분압 출력에서 분리되므로 입력 소스에 영향을 주지 않습니다.

저항간 반전증폭전압강하(R1)에서 인가된 입력신호와 비교하기 위한 기준전압, 즉 상한역치전압(V+)과 하한역치전압(V-)을 결정한다.이러한 전압은 출력 전압 및 저항 값이 고정됨에 따라 고정됩니다.

따라서 드롭 크로스(R1) 임계값 전압을 변경할 수 있습니다.저항(R1) 강하와 직렬로 바이어스 전압을 추가하면 전압 강하를 변경할 수 있으며, 임계값 전압을 변경할 수 있습니다.원하는 기준 전압 값은 다양한 바이어스 전압을 통해 얻을 수 있습니다.

위의 방정식은 다음과 같이 수정할 수 있습니다.

적용들

슈미트 트리거는 일반적으로 내소음성을 위한 개방 루프 구성과 함수 발생기를 구현하기 위한 폐쇄 루프 구성에서 사용됩니다.

- 아날로그-디지털 변환:슈미트 트리거는 사실상 디지털 변환기와 유사한 1비트입니다.신호가 특정 레벨에 도달하면 로우 상태에서 하이 상태로 전환됩니다.

- 레벨 검출:슈미트 트리거 회로는 레벨 검출이 가능합니다.이 응용 프로그램을 수행할 때는 회로가 필요한 전압을 켜도록 히스테리시스 전압을 고려해야 합니다.

- 회선 수신:노이즈를 로직 게이트로 픽업했을 가능성이 있는 데이터 라인을 실행할 때는 데이터가 변경되었을 때만 로직 출력 레벨을 변경할 필요가 있으며 픽업되었을 가능성이 있는 스플리어스 노이즈의 결과로 변경할 필요가 없습니다.슈미트 트리거를 광범위하게 사용하면 스플리어스 트리거가 발생하기 전에 피크 대 피크 노이즈가 이력 레벨에 도달할 수 있습니다.

소음 내성

슈미트 트리거의 한 가지 적용은 입력 임계값이 1개뿐인 회로에서 노이즈 내성을 높이는 것입니다.입력 임계값이 1개뿐일 경우 해당 임계값에 근접한 노이즈 입력 신호로 인해 노이즈만으로 출력이 빠르게 전환될 수 있습니다.노이즈가 있는 슈미트트리거 입력 신호가 1개의 임계값 부근에 있을 경우 출력값에서1개의 스위치밖에 발생하지 않습니다.그 후 다른 스위치를 발생시키려면 다른 임계값을 초과해야 합니다.

예를 들어 증폭된 적외선 포토다이오드는 절대 최저값과 절대 최고값 사이를 자주 전환하는 전기 신호를 생성할 수 있습니다.다음으로 이 신호는 로우패스필터링되어 스위칭신호가 온/오프되는 상대적인 시간에 따라 상승 및 하강하는 부드러운 신호를 형성합니다.필터링된 출력은 슈미트 트리거 입력으로 전달됩니다.결과적으로 슈미트 트리거의 출력은 수신된 적외선 신호가 포토다이오드를 알려진 기간보다 오랫동안 들뜨게 한 후에만 로우에서 하이로 통과하고 슈미트 트리거가 높으면 적외선 신호가 포토다이오드를 유사한 알려진 기간보다 오래 들뜨게 하지 않게 된 후에만 로우로 이동합니다.포토 다이오드는 환경 노이즈로 인해 스플리어스 스위칭이 발생하기 쉽지만 필터와 슈미트 트리거에 의해 추가된 지연에 의해 확실히 디바이스를 자극하는 입력이 있을 때만 출력이 스위칭됩니다.

슈미트 트리거는 유사한 이유로 많은 스위칭 회로에서 일반적입니다(스위치 디버깅 등).

다음 7400 시리즈 장치에는 입력에 슈미트 트리거가 포함되어 있습니다(7400 시리즈 집적회로 목록 참조).

- 7413: 듀얼 슈미트 트리거 4입력 NAND 게이트

- 7414: Hex Schmitt 트리거 인버터

- 7418: 듀얼 슈미트 트리거 4입력 NAND 게이트

- 7419: Hex Schmitt 트리거 인버터

- 74121: 슈미트 트리거 입력이 가능한 안정된 멀티바이버레이터

- 74132: 쿼드2 입력 NAND 슈미트 트리거

- 74221: 슈미트 트리거 입력 듀얼모노스터블 멀티바이브레이터

- 74232: 쿼드 NOR 슈미트 트리거

- 74310: 슈미트트리거 입력이 있는 옥탈버퍼

- 74340: 슈미트 트리거 입력 및 3스테이트 반전 출력이 있는 옥탈 버퍼

- 74341: 슈미트 트리거 입력 및 3스테이트 비반전 출력을 사용하는 옥탈 버퍼

- 74344: 슈미트 트리거 입력 및 3스테이트 비반전 출력을 사용하는 옥탈 버퍼

- 74(HC/HCT)7541 옥탈버퍼(슈미트트리거 입력 및 3스테이트 비반전 출력 포함

- SN74LV8151은 3스테이트 출력을 가진 10비트 유니버설 슈미트 트리거 버퍼입니다.

다수의 4000 시리즈 장치에는 입력에 슈미트 트리거가 포함되어 있습니다(4000 시리즈 집적회로 목록 참조).

- 4017: 디코딩된 출력이 있는 10진수 카운터

- 4020: 14 스테이지 바이너리 리플 카운터

- 4022: 디코딩된 출력이 있는 옥탈카운터

- 4024: 7 스테이지 바이너리 리플 카운터

- 4040: 12 스테이지 바이너리 리플 카운터

- 4093: 쿼드2 입력 NAND

- 4538: 듀얼 모노스터블 멀티바이저

- 4584: 16진수 반전 슈미트 트리거

- 40106: 헥스 인버터

슈미트 입력 설정 가능한 싱글 게이트 칩: (7400 시리즈 집적회로 목록 참조)#게이트 칩 1개)

- NC7SZ57 페어차일드

- NC7SZ58 페어차일드

- SN74LVC1G57 텍사스 인스트루먼트

- SN74LVC1G58 텍사스 인스트루먼트

발진기로 사용

슈미트 트리거는 쌍안정 멀티 바이브레이터이며, 이 트리거를 사용하여 다른 유형의 멀티 바이브레이터인 완화 오실레이터를 구현할 수 있습니다.이는 반전 슈미트 트리거의 출력과 입력 사이에 단일 RC 적분 회로를 연결하여 이루어집니다.출력은 주파수가 R 및 C의 값과 슈미트 트리거의 임계값 포인트에 따라 달라지는 연속 사각파가 됩니다.단일 집적회로(예를 들어 4000 시리즈 CMOS 장치 유형 40106에는 6개가 포함)에 의해 복수의 슈미트 트리거 회로가 제공될 수 있기 때문에 IC의 스페어 섹션은 2개의 외부 컴포넌트만으로 간단하고 신뢰할 수 있는 발진기로 신속하게 사용할 수 있습니다.

여기서 비교기 기반의 슈미트 트리거는 반전 구성에 사용됩니다.또한 RC 네트워크를 통합하면 느린 네거티브 피드백이 추가됩니다.그 결과 오른쪽에 표시된 것처럼 콘덴서가 한 슈미트 트리거 임계값에서 다른 슈미트 트리거 임계값으로 충전될 때 출력이 자동으로 V에서SSDD V로 진동합니다.

「 」를 참조해 주세요.

- OP 앰프 응용 프로그램

- 쌍안정 멀티 바이브레이터 회로

- 히스테리시스가 있는 임계값 검출기

- 4000 시리즈 집적회로 목록 - Schmitt 트리거 입력이 포함된 로직 칩 포함

- 7400 시리즈 집적회로 목록 - Schmitt 트리거 입력이 포함된 로직 칩 포함

메모들

- ^ 애매성의 원인 중 하나는 하나의 단순한 트랜지스터 기반의 슈미트 트리거 실현이 자연스럽게 반전되는 것이며, 비반전 슈미트 트리거는 때로 그러한 반전 구현과 인버터로 구성되어 있다.스탠드아론의 반전 구성을 버퍼링하기 위한 추가 인버터를 추가할 수 있다.이것에 의해, 집적회로내의 반전 구성을 자연스럽게 반전시키는 한편, 비반전 구성을 1개의 인버터로 구현하고, 독립형 반전 구성을 2개의 인버터로 구현할 수 있다.그 결과 반전 기포와 이력 곡선을 조합한 심볼은 장치 전체 또는 내장된 슈미트 트리거만을 설명하기 위해 이력 곡선을 사용할 수 있습니다.

- ^ 일반적으로 음의 피드백은 op-amp 회로에서 사용됩니다.일부 연산 증폭기는 반전 입력과 비반전 입력 간에 무시할 수 정도의 차이를 적용하는 음의 피드백 구성에서만 사용하도록 설계되었습니다.입력 보호 회로가 내장되어 있어 반전 및 비반전 입력이 서로 멀리 떨어진 곳에서 작동하지 않습니다.예를 들어 병렬로 반대편향을 갖는 2개의 범용 다이오드 또는 직렬로 반대편향을 갖는 2개의 제너 다이오드(즉, 이중 양극 제너 다이오드)로 이루어진 클리퍼 회로가 연산증폭기의 2개의 입력에 걸쳐 내부적으로 사용되는 경우가 있다.이 경우 연산 증폭기는 비교기로서 제대로 작동하지 않습니다.반대로 비교기는 입력 전압이 크게 다를 수 있다는 가정 하에 설계된다.

- ^ 비반전(+) 입력이 반전(-) 입력보다 높은 전압일 경우 비교기 출력은 높은 공급S 전압인 +V로 거의 전환됩니다.비반전(+) 입력이 반전(-) 입력보다 낮은 전압일 경우 비교기 출력은 공급 전압이 낮은 -V로S 거의 전환됩니다.

- ^ 소음 진폭이 슈미트 트리거 임계값의 변화에 비해 작다고 가정하는 경우.

레퍼런스

- ^ Schmitt, Otto H. (January 1938). "A Thermionic Trigger". Journal of Scientific Instruments. 15 (15): 24–26. Bibcode:1938JScI...15...24S. doi:10.1088/0950-7671/15/1/305.

- ^ a b Pavek 방송 박물관 뉴스레터 2004년 8월호http://160.94.102.47/Otto_Images/PavekOHSbio.pdf Wayback Machine에서 2015-10-01 아카이브 완료

- ^ SR 래치가 있는 스위치의 디버깅

- ^ 7414 데이터 시트

되어

되어

지정되며 출력 M의 최대값은 전원 레일입니다.

지정되며 출력 M의 최대값은 전원 레일입니다.

되어 하이로 돌아갑니다.따라서 이 회로는 0을

되어 하이로 돌아갑니다.따라서 이 회로는 0을