I²S

I²S| 유형 | 시리얼 통신 버스 | ||

|---|---|---|---|

| 생산 이력 | |||

| 디자이너 | 오늘날 NXP Semiconductors로 알려진 Philips Semiconductor | ||

| 설계된 | 전 | ||

| 데이터. | |||

| 데이터 신호 | 푸시풀 | ||

| 폭 | 데이터라인(SD)×1 + 2 클럭 라인(SCK, WS) | ||

| 프로토콜 | 시리얼 | ||

I²S(Inter-IC Sound, "eye-squared-ess"로 발음)는 디지털 오디오 장치를 연결하는 데 사용되는 전기 직렬 버스 인터페이스 표준입니다.전자 장치의 집적 회로 간에 PCM 오디오 데이터를 통신하는 데 사용됩니다.I²S 버스는 클럭 데이터 신호와 시리얼 데이터 신호를 분리하여 데이터 스트림에서 클럭을 복구해야 하는 비동기 통신 시스템에 필요한 수신 장치보다 단순합니다.또는 I²S의 철자는 I2S(eye-two-ess로 발음) 또는 IIS(eye-eye-ess로 발음)입니다.비슷한 이름에도 불구하고 I²S는 양방향 I²C(IIC) 버스와 관련이 없습니다.

역사

이 표준은 Philips Semiconductor(현 NXP Semiconductors)에 의해 1986년에 도입되어 1996년 [1]6월 5일에 처음 개정되었습니다.이 표준은 2022년 2월 17일에 마지막으로 개정되었으며 마스터와 슬레이브라는 용어를 컨트롤러와 [2]타깃으로 업데이트하였다.

세부 사항

I²S 프로토콜은 Philips 사양에 설명된 정의된 매개 변수를 사용하여 특정 유형의 PCM 디지털 오디오 통신의 개요를 제공합니다.

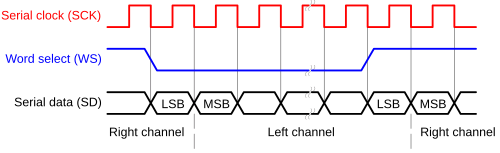

버스는 최소 3개의 노선으로 구성됩니다.

- 비트 클럭 라인

- 워드 클럭 라인

- 하나 이상의 다중 데이터 라인

다음 행도 포함할 수 있습니다.

- 마스터 클럭(일반적으로 256 x LRCLK)

- 업로드할 다중 데이터 라인

비트 클럭은 데이터 라인의 각 이산 비트마다 1회 펄스를 일으킵니다.비트 클럭 주파수는 샘플링 속도, 채널당 비트 수 및 채널 수의 곱입니다.예를 들어 샘플 주파수가 44.1kHz이고 정밀도가 16비트이고 채널(스테레오)이 2개인 CD 오디오의 비트 클럭 주파수는 다음과 같습니다.

- 44.1kHz × 16 × 2 = 1.4112MHz

I²S를 사용하면 동일한 데이터 라인에서 두 채널을 전송할 수 있으므로 선택 클럭이라는 단어를 사용하면 장치가 채널 0 또는 채널 1 중 어느 쪽을 현재 전송 중인지 알 수 있습니다.샘플 주파수와 주파수가 동일한 50% 듀티 사이클 신호입니다.스테레오 소재의 경우, I²S 사양은 워드 셀렉트 클럭의 로우 사이클에 좌측 오디오를 송신하고, 하이 사이클에 우측 채널을 송신한다고 기술하고 있다.일반적으로 데이터는 상승 [1]에지에 래치되므로 시리얼 클럭의 하강 에지와 동기화됩니다.select clock이라는 단어는 MSB가 전송되기 전에 1비트 클럭 주기를 변경합니다.이를 통해 예를 들어 수신자는 이전 단어를 저장하고 [1]다음 단어의 입력을 지울 수 있습니다.

데이터가 서명되고 MSB(최상위 비트)를 통해 2의 보완으로 인코딩됩니다.[1]이것에 의해, 송신기와 [1]수신기의 네고시에이션이 불필요하게 되어, 프레임 당의 비트수를 임의로 설정할 수 있습니다.

오디오 인터커넥트로

오디오 기기에서는 I²S가 CD 플레이어와 외부 디지털/아날로그 변환기 사이의 외부 링크로 사용되는 경우가 있는데, 이는 하나의 플레이어 박스 내에서 순수하게 내부 접속이 아닌 것입니다.이는 일반적으로 사용되는 AES/EBU, Toslink 또는 S/PDIF 표준 대신 사용될 수 있습니다.

I²S 연결은 케이블을 통해 사용하도록 설계되지 않았으며 대부분의 집적회로는 동축 케이블에 대한 임피던스가 올바르지 않습니다.다른 라인 길이에 관련된 임피던스 적응 오차는 클럭 라인과 데이터 라인 간의 전파 지연의 차이를 일으킬 수 있으므로 SCK, WS 및 데이터 신호 간의 동기 문제가 발생할 수 있으며, 주로 높은 샘플링 주파수와 비트 레이트에서 발생합니다.I²S 버스에는 오류 감지 메커니즘이 없으므로 상당한 디코딩 오류가 발생할 수 있습니다.

이 응용 프로그램에는 표준 상호 연결 케이블이 없습니다.제조원에 따라서는 3개의 BNC 커넥터, 8P8C("RJ45") 소켓 또는 DE-9 커넥터를 제공합니다.Audio Alchemy(현재는 사용되지 않음)와 같은 다른 제품들은 DIN 커넥터를 사용했습니다.PS Audio, Musica Pristina 및 Wyred4 Sound는 HDMI 커넥터를 사용합니다.네덜란드 제조업체인 Van Medevoot는 일부 장비에 Q-link를 구현하여 4개의 RCA 커넥터(데이터, MCK, LRCK, BCK)를 통해 I²S를 전송합니다.

「 」를 참조해 주세요.

레퍼런스

- ^ a b c d e f g h i "I²S Specification" (PDF). Philips Semiconductors. June 5, 1996. Archived from the original (PDF) on January 2, 2007.

- ^ "UM11732 I2S bus specification" (PDF). NXP. Retrieved 19 March 2022.

- ^ a b c Lewis, Jerad (January 2012). "Technical Article MS-2275: Common Inter-IC Digital Interfaces for Audio Data Transfer" (PDF). Analog Devices, Inc.

- ^ a b "MCLK in I2S audio protocol". electronics.stackexchange.com. Retrieved 2016-11-04.

Clock source for the delta-sigma modulators and digital filters. ... It is the clock that is used by the audio codec ... to time and/or drive its own internal operation.

- ^ "PCM1781 (or any I2S DAC) clock sources - Audio Converters Forum - Audio Converters - TI E2E Community". e2e.ti.com. Retrieved 2016-11-04.

True, the master (modulator) clock is not part of the I2S standard

- ^ Arbona, Jorge (September 2010). "Application Report SLAA469 Audio Serial Interface Configurations for Audio Codecs" (PDF).

Audio converters based on the delta-sigma (ΔΣ) architecture require an internal master clock that operates at a much faster rate than the target sample rate.

외부 링크

- I²S 사양 - Philips/NXP

- I²S 및 STM32F4 슬라이드 - Ouburn University

- 오디오 데이터 전송을 위한 공통 IC 디지털 인터페이스, PDF