AMD Am29000

AMD Am29000

일반적으로 29k로 단축되는 AMD Am29000은 Advanced Micro Devices(AMD)에서 개발 및 제작한 32비트 RISC 마이크로프로세서 및 마이크로컨트롤러 제품군입니다. 버클리 RISC의 대표적인 모델인 29k는 여러 가지 중요한 개선 사항을 추가했습니다.이 칩들은 한때 시장에서 가장 인기 있는 RISC 칩이었으며,[citation needed] 다양한 제조업체의 레이저 프린터에 널리 사용되었습니다.

1984년부터 1985년까지 개발되어 1987년 3월에 발표되었으며 1988년 5월에 출시된 [1][2][3]Am29000은 여러 버전으로 출시되었으며 1995년에 Am29040으로 끝이 났습니다.[4]29050은 사이클당 한 번의 곱셈 연산을 수행할 수 있는 부동 소수점 장치를 갖추고 있기 때문에 주목을 받았습니다.

AMD는 1995년 말까지 슈퍼스칼라 버전을 설계하고 있었는데, 이 때 AMD가 29k의 개발을 중단한 이유는 설계 팀이 사업의 PC(x86) 쪽으로 이전되었기 때문입니다.AMD의 임베디드 비즈니스에서 남은 것은 임베디드 186 계열의 80186 파생 제품으로 재조정되었습니다.그때까지 AMD의 대부분의 자원은 데스크톱 PC용 고성능 x86 프로세서에 집중되었으며, AMD K5를 생산하기 위해 29k 디자인의 많은 아이디어와 개별 부품을 사용했습니다.

설계.

29k는 Sun SPARC, Intel i960, ARM 및 RISC-V로 이어지는 동일한 버클리 RISC 디자인에서 진화했습니다.

Berkeley RISC에서 파생된 일부 디자인에 사용된 한 가지 디자인 요소는 절차 호출의 속도를 크게 높이는 데 사용되는 기술인 레지스터 윈도우의 개념입니다.이 아이디어는 많은 레지스터 세트를 스택으로 사용하여 통화 중에 로컬 데이터를 레지스터 세트에 로드하고 프로시저가 돌아오면 "죽었다"고 표시하는 것입니다.루틴에서 반환되는 값은 SPARC(예: SPARC)의 상위 8개 레지스터인 "글로벌 페이지"에 배치됩니다.Stanford 대학의 경쟁 초기 RISC 디자인인 Stanford MIPS도 이 개념을 검토했지만 개선된 컴파일러가 유선 연결 창보다 범용 레지스터를 더 효율적으로 사용할 수 있다고 판단했습니다.

원래 버클리 디자인인 SPARC와 i960에서는 창문의 크기가 고정되어 있었습니다.로컬 변수를 하나만 사용하는 루틴은 SPARC에서 8개의 레지스터를 여전히 사용하므로 이 값비싼 리소스가 낭비됩니다.여기서 29000은 가변적인 창 크기를 사용하여 이러한 초기 디자인과 차별화되었습니다.이 예제에서는 두 개의 레지스터만 사용됩니다. 하나는 로컬 변수에, 다른 하나는 반환 주소에 사용됩니다.또한 프로시저 스택에 대해 동일한 128개의 레지스터를 포함하여 더 많은 레지스터를 추가했지만 글로벌 액세스를 위해 또 다른 64개를 추가했습니다.이에 비해 SPARC는 총 128개의 레지스터를 가지고 있으며, 글로벌 세트는 8개의 표준 윈도우였습니다.이러한 변화로 인해 다양한 워크로드에서 29000의 레지스터 사용률이 훨씬 향상되었습니다.

또한 29000은 메모리 내(그리고 이론적으로는 캐시 내) 스택으로 레지스터 윈도우 스택을 확장했습니다.창이 채워지면 호출은 레지스터 스택의 끝에서 메모리로 밀려나며 루틴이 반환되면 필요에 따라 복원됩니다.일반적으로 29000의 레지스터 사용은 버클리 개념을 기반으로 한 경쟁 디자인보다 훨씬 진보했습니다.

버클리 디자인과의 또 다른 차이점은 29000은 특수 목적 조건 코드 레지스터를 포함하지 않았다는 것입니다.어떤 레지스터라도 이 목적을 위해 사용할 수 있으므로 코드를 복잡하게 만드는 대신 조건을 쉽게 저장할 수 있습니다.Branch Target Cache(29000의 경우 512바이트, 29050의 경우 1024바이트)는 Branch Target 주소에서 발견된 4개 또는 2개의 순차 명령 집합을 저장하여 Branch를 사용하는 동안 명령 페치 지연 시간을 줄였습니다. 29000에는 어떠한 Branch 예측 시스템도 포함되어 있지 않기 때문에 Branch를 사용하는 경우 지연이 발생했습니다.버퍼는 분기의 대상 주소에서 4개 또는 2개의 명령을 저장함으로써 이를 완화시켰는데, 이 명령은 페치 버퍼가 메모리에서 새 명령으로 다시 채워지는 동안 즉시 실행될 수 있었습니다.[5]

가상 주소 변환 지원은 MIPS 아키텍처와 유사한 접근 방식을 따랐다.64 엔트리 TLB(Translation Look-aside Buffer)는 가상 주소에서 물리 주소로의 매핑을 유지하며, 변환되지 않은 주소가 발견되면 결과적으로 TLB "miss"로 인해 프로세서는 물리 메모리에 대한 적절한 매핑을 제공하는 역할을 담당하는 소프트웨어 루틴에 트랩하게 됩니다.TLB 미스 이벤트 시 대체할 TLB 엔트리를 선택하기 위해 랜덤 레지스터를 사용하는 MIPS 접근 방식과는 대조적으로, 29000은 (가장 최근에 사용된) 전용 루(lru) 레지스터를 제공했습니다.[6]29000 제품군의 일부 제품은 실리콘의 일부를 주변기기에 전용할 수 있도록 16개의 TLB 엔트리만 제공했습니다.이를 보완하기 위해 매핑에 사용되는 최대 페이지 크기를 8KB에서 16MB로 늘렸습니다.[7]: 305–306

버전

최초의 Am29000은 1988년에 MMU가 내장되어 출시되었으나 부동 소수점 지원은 Am29027 FPU로 오프로드되었습니다. MMU 또는 Branch Target Cache에 장애가 발생한 유닛은 Am29005로 판매되었습니다.[5]

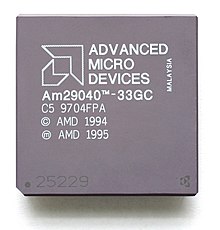

1991년에 Am29030과 Am29035로 라인이 확장되었으며, 각각 8KB 또는 4KB의 명령 캐시가 포함되었습니다.[8]이때[9] Am29050은 온칩 캐시 없이도 사용할 수 있게 되었지만, 완전히 파이프라인된 다중 누적 작업, 80%의 적중률을 자랑하는 더 큰 1KB 지점 타겟 캐시, 4-엔트리 TLB와 같은 물리적 주소 캐시를 통해 더 나은 파이프라인의 로드 작업 속도를 높일 수 있었습니다.슈퍼스칼라 프로세서는 아니지만 부동 소수점 연산과 정수 연산을 같은 주기로 완료할 수 있습니다.정수 측과 부동 소수점 측에는 각각 레지스터에 대한 고유한 쓰기 포트가 있습니다.[10]0.8 마이크론 유효 채널 길이의[10] 1 마이크론 공정에[12] 428,000개의 트랜지스터가[11] 들어 있었고 20, 25, 33, 40MHz에서 사용할 수 있었습니다. 이후 Am29040은 33, 40, 50MHz로 출시되었는데, 4KB 데이터 캐시, 곱셈 장치 및 몇 가지 다른 향상된 기능을 갖춘 것을 제외하면 Am29030과 같습니다.[13]119 mm² Am29040은 0.7 마이크론 공정에 120만 개의 트랜지스터를 포함하고 있었습니다.[14][15]

29K의 슈퍼스칼라 버전이 설계 중이었으나 x86을 선호하여 취소되었습니다.코드명은 재규어이며, 1994년 11월과 1995년 8월에 기술되었습니다.[3][16][17]이것은 진보된 디자인으로, 6개의 예약 스테이션에 4방향 파견이 가능하고, 4방향 퇴역이 가능한 추측성 명령어 실행이 가능했습니다.레지스터 파일은 4개의 읽기와 2개의 쓰기를 동시에 허용했습니다.명령과 데이터의 캐시는 각각 8KB였습니다.캐시의 로드가 저장소를 우회할 수 있습니다.비용 문제와 목표 시장 때문에 온칩 FPU가 없었습니다.그것은 0.4 마이크론 공정에서 100 MHz 주파수에 도달할 것으로 예상되었습니다.[16][18]

AMD는 출시되지 않은 29K 마이크로아키텍처를 x86 호환 프로세서의 K5 시리즈의 기본으로 사용했습니다.ALU는 이월되었고, 약간 수정된 재주문 버퍼도 이월되었습니다.FPU는 29050에서 가져왔지만 80비트 정밀도로 확장되었습니다.K5는 캐시된 명령어의 사전 디코딩 정보에 도움을 받아 디코딩 시 x86 명령어를 "RISC-OP"로 변환했습니다.AMD는 슈퍼스칼라 29K의 성능은 K5보다 약간 떨어지지만 크기 차이로 인해 비용은 훨씬 낮다고 주장했습니다.[19][16]

허니웰 29KII는 AMD 29050을 기반으로 하는 CPU로 실시간 항공전자 분야에서 널리 사용되었습니다.

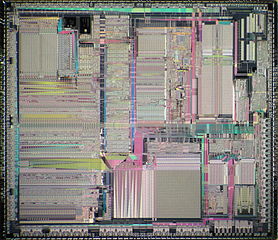

- 다이 사진

-

Am29000

-

Am29030

-

Am29040

-

Am29050

제품 및 응용프로그램

29000은 유닉스 워크스테이션에서 사용 가능성이 있는 "중고 성능 임베디드 응용 프로그램"을 위한 제품으로 자리 잡았으며, [6]X 단자, 레이저 프린터 컨트롤러 카드, 그래픽 가속기 카드, 광학 문자 인식 솔루션, 네트워크 브리지 등 다양한 제품에 사용되었습니다.[20]29000의 메모리 아키텍처는 제품 설계자들에게 특별한 매력이었습니다. 이를 통해 외부 캐시 메모리를 포기하고 동적 RAM을 직접 사용하는 동시에 수용 가능한 성능을 유지할 수 [20]: 1 있어 프로그램 명령 및 데이터를 유지하는 데 사용되는 메모리 기술을 어느 정도 유연하게 선택할 수 있었습니다.[21]

29000은 특히 Macintosh와 IBM PC 호환 플랫폼에서 컴퓨팅 가속기 또는 보조 프로세서로 사용되었습니다.예를 들어, Yarc Systems Corporation은 Macintosh II 및 PC AT 시스템용 29000 기반 "RISC 코프로세서" 카드를 생산했으며, Motorola 68020 및 68030 프로세서를 탑재한 다른 "CISC 코프로세서" 카드와 T800 트랜스퓨터 프로세서를 탑재한 "병렬 코프로세서" 카드도 생산했습니다.[22]Am29000 CPU와 Am29027 부동소수점 가속기를 채용한 NuSuper(원래 이름은 McCray[23])와 AT-Super 카드가 [22]뒤를 이어 MacRageous가 Am29050으로 CPU를 업그레이드했습니다.[24]이러한 가속기 카드는 매킨토시 II 자체의 몇 배의 성능을 제공했으며 DECstation 3100과 같은 RISC 워크스테이션과 경쟁적으로 벤치마킹했습니다.시스템에 여러 장의 카드를 장착할 수도 있습니다.그러나 매킨토시 II 시스템과 이러한 카드를 결합한 비용은 Unix를 실행하는 기존 RISC 워크스테이션의 비용에 근접했습니다.[25]

29000을 사용하는 한 가지 주목할 만한 제품은 매킨토시 IIfx용 애플의 매킨토시 디스플레이 카드 8·24 GC였으며, 30MHz Am29000 프로세서, 64KB 정적 RAM 캐시, 2MB의 비디오 RAM을 갖추고 QuickDraw 그래픽 툴킷에서 사용할 수 있는 추가 2MB의 동적 RAM 옵션을 제공했습니다.29000이 포함됨으로써 이 특정 버전의 카드는 애플이 판매하는 다른 버전과 차별화되어 픽셀당 24비트 이미지를 처리할 때 성능이 크게 향상되었습니다.[26]

참고 항목

참고문헌

- ^ Martin, James A. (23 March 1987). "Firm says 32-bit chip handles 17 MIPS". Computerworld. Vol. 21, no. 12. p. 14.

- ^ Cole, Bernard C. (28 April 1988). "RISC Slugfest: Is Marketing More Important Than Performance?" (PDF). Electronics. p. 66 (p. 68 of .pdf).

- ^ a b "Oral History of William Michael 'Mike' Johnson" (PDF). Computer History Museum (Interview). Interviewed by Kevin Krewell. 9 May 2014.

Well, it started in '85. And it took I would say about three years and maybe four revs till it was functional.

- ^ Betker, Michael R.; Fernando, John S.; Whalen, Shaun P. (Autumn 1997). "The History of the Microprocessor" (PDF). Bell Labs Technical Journal: 48.

- ^ a b Stewart, Brett (1990). "New generations of the 29 K family solutions". Digest of Papers Compcon Spring '90. Thirty-Fifth IEEE Computer Society International Conference on Intellectual Leverage. pp. 295–298. doi:10.1109/CMPCON.1990.63690.

- ^ a b Mann, Daniel (October 1991). "Unix and the Am29000 Microprocessor". IEEE Micro. pp. 23–31. ISSN 0272-1732. Retrieved 19 May 2023.

- ^ Mann, Daniel (1995). Evaluating and Programming the 29K™ RISC Family. Advanced Micro Devices. Retrieved 19 May 2023.

- ^ Fickel, Louise (13 May 1991). "Advanced Micro Devices Bolsters 29000 Family With Two RISC CPUs". InfoWorld. Vol. 13, no. 19. p. 28.

- ^ "FLASH MEMORY ANNOUNCEMENTS". Computer Business Review archive at Tech Monitor. 9 October 1990.

- ^ a b "Am29050™ Microprocessor User's Manual". archive.org. 1991.

- ^ Ganapathy, Gopi; Abraham, Jacob A. Hardware Acceleration Alone Will Not Make Fault Grading ULSI A Reality. International Test Conference 1991.

- ^ Lynch, Thomas Walker; Swartzlander (Jr), Earl E. (July 1991). "The redundant cell adder". Proceedings, 10th IEEE Symposium on Computer Arithmetic. doi:10.1109/ARITH.1991.145553.

- ^ "Am29040 High-Performance RISC Microprocessor with Instruction and Data Caches" (PDF). chipdb.org. Retrieved 18 September 2022.

- ^ Gwennap, Linley. "Digital, MIPS Add Multimedia Extensions" (PDF). Microprocessor Report. 10 (15): 24–28.

- ^ Microprocessor Forum folder. 1994.

{{cite book}}:website=무시됨(도움말) - ^ a b c McMinn, Brian (14 August 1995). "The First Superscalar 29K Family Member" (PDF). Hot Chips.

- ^ "FIRST SUPERSCALAR Am29000 REVEALED". Computer Business Review archive at Tech Monitor. 28 November 1994.

- ^ Detar, Jim (31 October 1994). "AMD brews up Superscalar 29K". Electronic News.

- ^ Slater, Michael (24 October 1994). "AMD's K5 Designed to Outrun Pentium" (PDF). Microprocessor Report. 8 (14): 1–7.

- ^ a b FUSIONews 29K. Advanced Micro Devices. Summer 1990. Retrieved 20 May 2023.

- ^ Marshall, Trevor (May 1988). "Real-World RISCs". Byte. pp. 263–268. Retrieved 20 May 2023.

- ^ a b YARC, the solutions company. Yarc Systems Corporation.

- ^ "YARC Claims 50-MHz Operation for Mac II Booster Board". Byte. August 1988. p. 16. Retrieved 20 May 2023.

- ^ MacRageous Macintosh-II RISC Coprocessor System. Yarc Systems Corporation.

- ^ Varhol, Peter D. (October 1989). "YARC's NuSuper Soups Up the Mac". MIPS. pp. 81–83. Retrieved 20 May 2023.

- ^ Smith, Bud E. (May 1990). "A Big, Fast, Macintosh with RISC Graphics". Personal Workstation. pp. 46–50. Retrieved 20 May 2023.

외부 링크

- AMD 29k (streamed instruction processor) ID 가이드

- Mann, Daniel (1995), Evaluating and Programming the 29K RISC Family (PDF), Advanced Micro Devices, archived from the original (PDF) on September 27, 2007 pdf book 29k 가족에 대해서

- chipdb.org 다양한 Am29000 프로세서 이미지