Zilog Z80

Zilog Z80 날짜 스탬프에 따라 1976년 6월에 제조된 Z80 | |

| 일반 정보 | |

|---|---|

| 개시. | 1976년 3월 |

| 설계자 | 페데리코 파긴, 시마 마사토시 |

| 공통 제조원 | |

| 성능 | |

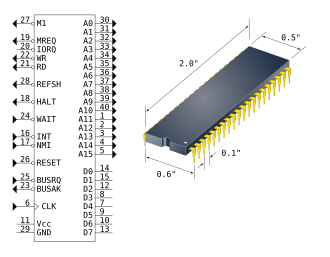

| 최대 CPU 클럭 속도 | 2.5, 4, 6, 8 MHz~10 MHz, CMOS 배리언트 최대 20 MHz 및 바이너리 호환 파생 모델(Zilog에서 최대 33 MHz 및 50 MHz). |

| 데이터 폭 | 8비트[1] |

| 주소 폭 | 16비트[1] |

| 물리 사양 | |

| 트랜지스터 |

|

| 패키지 | |

| 소켓 |

|

Z80은 Zilog가 스타트업 회사의 첫 제품으로 선보인 8비트 마이크로프로세서입니다.Z80은 1974년 말 Federico Faggin에 의해 고안되어 1975년 초에 그와 그의 11명의 직원이 개발했다.최초의 작업 샘플은 1976년 3월에 납품되어 1976년 7월에 정식으로 시장에 도입되었습니다.Z80의 수익으로, 동사는 독자적인 칩 팩토리를 건설해, 그 후 [2]2년간 1,000명 이상의 종업원으로 성장했습니다.

Zilog Z80은 인텔 8080의 소프트웨어 호환 확장 기능 및 확장 기능으로 주로 임베디드 시스템을 대상으로 하고 있습니다.Z80은 이 역할에 사용되었지만 1970년대부터 1980년대 [3][4]중반까지 데스크톱 컴퓨터와 가정용 컴퓨터에서 가장 널리 사용되는 CPU 중 하나가 되었습니다.또한 군사 애플리케이션, 신시사이저와 같은 음악 장비(롤랜드 주피터-8), 팩맨을 포함한 1970년대 후반과 1980년대 초반의 동전 작동식 아케이드 게임에서도 흔했다.

Zilog는 Z80을 미국에 본사를 둔 Synertek와 Mostek에 라이선스하여 초기 생산을 도왔으며 유럽의 두 번째 소스 제조업체인 SGS에도 라이선스했습니다.이 디자인은 또한 몇몇 일본, 동유럽,[ii] 소련 제조사들에 의해 모방되었다.NEC, 도시바, 샤프, 히타치와 같은 대기업이 디바이스(또는 독자적인 Z80 호환 클론이나 디자인)를 제조하기 시작한 이래, 세계 시장에서 Z80의 인정을 받았습니다.

최근 수십 년 동안 Zilog는 지속적으로 성장하고 있는 임베디드 시스템 시장에 다시 초점을 맞추고 있으며, 가장 최근의 Z80 호환 마이크로 컨트롤러 제품군인 선형 16MB 주소 범위를 갖춘 24비트 eZ80은 보다 단순한 Z80 및 Z180 제품과 함께 성공적으로 출시되었습니다.

역사

Z80은 물리학자이자 엔지니어인 Federico Faggin이 1974년 말 인텔을 떠나 Ralph Ungermann과 함께를 설립하면서 탄생했습니다Fairchild Semiconductor에서, 그리고 후에 Intel에서, Faggin은 기초적인 트랜지스터와 반도체 제조 기술에 종사해 왔습니다.그는 또한 인텔에서 메모리와 마이크로프로세서에 사용되는 기본 설계 방법을 개발했으며 인텔 4004, 8080 및 기타 여러 IC에 대한 연구를 주도했습니다.4004와 8080의 주요 로직이자 트랜지스터 레벨 설계자인 시마 마사토시씨가 Zilog 팀에 합류했다.

설계자에 따르면 Z80 CPU(옵션 지원 및 주변기기 IC[iii])의 주요 타깃은 인텔리전트 터미널, 하이엔드 프린터 및 고급 현금 레지스터와 같은 제품과 통신 기기, 산업용 로봇 및 기타 자동화 기기였습니다.

1976년 3월까지 Zilog는 고객을 위한 조립기 기반 개발 시스템과 함께 Z80을 개발하였고, 1976년 7월에 정식으로 시장에 [5]출시되었습니다.Z80 지원 및 주변기기의 일부는 이 시점에서 개발 중이며, 그 중 상당수는 다음 해에 출시되었다.

초기 Z80은 Synertek과 Mostek에서 제조되었으며, Zilog는 1976년 말에 자체 제조 공장을 준비했습니다.이 회사들은 Z80이 단일 5V 전원 [iv]공급에 대응하기 위해 부하 트랜지스터로 사용하는 고갈 모드 MOSFET를 만드는 데 필요한 이온 주입을 수행할 수 있기 때문에 선택되었습니다.

Faggin 명령은 8080(뿐만 아니라 그것의 소스 코드로)을 위한 대부분의 8080코드, 특히 CP/M 운영 체제와 인텔의 PL/M 컴파일러, 수정되지 않은 새로운 Z80 CPU. 마사토시 시마에 달아날 것이라고 인텔 8080[6][7]과 2진 호환할으로 설정된 마이크로 아키텍처뿐 아니라 대문과 트랜지스터 수준 대부분의 디자인을 디자인했다. 의Z80 CPU, 소수의 엔지니어 및 레이아웃 [8][9]담당자의 지원을 받습니다.CEO Federico Faggin은 실제로 2명의 전담 레이아웃 담당자와 함께 칩 레이아웃 작업에 크게 관여했습니다.Faggin에 따르면, 그는 재무적 [2]투자자들의 빡빡한 일정을 맞추기 위해 일주일에 80시간을 일했다.

Z80은 [7]8080에 비해 많은 개선점을 제공했습니다.

- 다음을 포함한 확장 명령 세트:

- 어셈블러 명령 니모닉의 보다 논리적이고 이해하기 쉽고 읽기 쉬운 시스템

- 보다 유연한 16비트 데이터 이동(로드 또는 LD) 명령(스택 포인터 SP 포함)

- 외부 주변기기 포트에 대한 입출력용 보다 유연한 어드레싱 모드

- 비트 테스트를 포함한 모든 레지스터 및 메모리의 싱글 비트어드레싱

- 메모리 및 어큐뮬레이터 이외의 레지스터에서 시프트/스위치 전환

- (이전 8080보다) 개량된 정확성 BCD 연산

- 메모리의 BCD 번호 문자열에 대한 명령 회전

- 16비트 감산 및 8비트 부정

- 프로그램 루프

- 프로그램 카운터 상대 점프

- 블록 복사, 블록 입출력(I/O) 및 바이트 검색 [10]명령입니다.

- 서명된 8비트 및 16비트 [v]산술이 더 잘 지원되는 오버플로 플래그입니다.

- 새로운 IX 및 IY 인덱스는 직접 베이스+오프셋 주소 지정에 대한 명령으로 등록됩니다.

- 보다 나은 인터럽트 시스템:

- 보다 자동적이고 일반적인 벡터화된 인터럽트 시스템인 모드 2는 주로 Zilog의 카운터/타이머 라인, DMA 및 통신 컨트롤러 및 최소한의 하드웨어(모드 0은 8080 호환 모드)[11]를 갖춘 단순한 시스템을 위한 고정 벡터 인터럽트 시스템인 모드 1을 대상으로 합니다.

- Non Maskable Interrupt(NMI; 마스크 불가능 인터럽트)는 전원 차단 상황 또는 기타 높은 우선순위의 이벤트에 응답하기 위해 사용할 수 있습니다(및 최소화된 Z80 시스템이 모드1에서 2레벨 인터럽트 방식을 쉽게 구현할 수 있도록 합니다).

- 고속 비동기 이벤트 핸들러나 멀티태스킹디스패처 등의 인터럽트에 대한 응답 속도를 높이기 위해 빠르게 전환할 수 있는 완전한 중복 레지스터 [12]파일입니다.일반 코드의 추가 레지스터로 의도된 것은 아니지만,[vi] 일부 애플리케이션에서는 이러한 방식으로 사용되었습니다.

- 전원 공급, 클럭 생성 및 메모리 및 I/O 인터페이스에 필요한 하드웨어 감소

- 5V 전원장치(8080에는 -5V/+5V/+12V 필요).

- 단상 5볼트 클럭(8080에는 겹치지 않는 2상 클럭이 필요).

- 내장 DRAM 리프레시.SRAM을 사용하지 않으면 외부 회로가 필요하게 됩니다.단, SRAM은 [vii]더 비싸고 밀도가 낮습니다(단, 더 빠릅니다).

- 비멀티플렉스 버스(8080은 데이터 버스에 다중화된 상태 신호가 있습니다).

- 단일 Z80 CPU를 인서킷 [13]에뮬레이터 등의 개발 시스템에서 사용할 수 있도록 프로그램 카운터만 클리어하는 특수 리셋 기능.

Z80은 프로세서 시장에서 [14]8080과 그 후속 제품인 8085를 이어받아 가장 인기 있고 널리 사용되는 8비트 CPU [3][4]중 하나가 되었습니다.British Telecom과 같은 일부 조직은 임베디드 애플리케이션에 익숙하고 온칩 시리얼 인터페이스와 인터럽트 아키텍처에 익숙하기 때문에 8085에 대한 충성도를 유지했습니다.마찬가지로 Zenice Data Systems는 8085와 16비트 Intel 8088을 조합하여 최초의 MS-DOS 컴퓨터인 Zenice Z-100을 개발했습니다.이는 Z80 기반의 Heathkit H89 및 Zenice Z-89 제품에 대한 경험이 있기 때문입니다.그러나 Z80을 다른 CPU와 통합한 다른 컴퓨터도 있습니다: Motorola 68000을 탑재한 Radio Shack TRS-80 Model 16, 8088을 탑재한 DEC Rainbow, MOS 8502를 탑재한 Commodore 128.

Zilog는 1980년대 초반 성장하던 노트북 컴퓨터 시장에 적합한 저전력 Z80을 늦게 생산했다.인텔은 1983년 4월부터 탠디(TRS-80 모델100), 올리베티, NEC에서 판매된 Kyocera 디자인의 노트북과 같은 배터리 구동식 노트북에 사용되는 CMOS 8085(80C85)를 생산했습니다.그러나 몇 년 후에는 Z80의 CMOS 버전(Zilog와 일본 제조사 모두)이 Amstrad NC100, Cambridge Z88 및 Tandy 자체 WP-2와 같은 제품에서도 이 시장을 지배하게 될 것입니다.

Z80의 초기 성공의 열쇠는 적어도 CP/M이나 기타 사무실 및 가정용 컴퓨터 등의 시장에서는 내장 DRAM 교체였을 것입니다(대부분의 Z80 임베디드 시스템은 교체가 필요 없는 정적 RAM을 사용합니다).또한 최소 2레벨 인터럽트 시스템, 또는 반대로 멀티레벨 데이지 체인 인터럽트 시스템이 여러 Z80 IO 칩을 수리하는 데 유용했을 수도 있습니다.적은 하드웨어와 심플한 회로 기판 레이아웃으로 시스템을 구축할 수 있었던 모든 기능.그러나 다른 사람들은 그 인기가 더 적은 레지스터를 가진 8비트 CPU에 비해 콘텍스트 전환이 빠르거나 부동소수점 연산과 같은 것들을 더 효율적으로 처리할 수 있는 중복 레지스터 때문이라고 주장한다. (Z80은 HL'HL, DE'DE, BC'를 사용하여 내부적으로 그러한 숫자들을 여러 개 유지할 수 있다.)BC는 32비트가 등록되므로 계산 중에 느린 RAM에서 액세스할 필요가 없습니다.)[15]

원래의 NMOS 설계에서는, 기존의 4 MHz(Z80A), 최대 6 MHz(Z80B) 및 8 MHz(Z80H)[16][17]를 개입시켜, 초기 2.5 MHz로부터 지정 상한 클럭 주파수가 연속적으로 증가했습니다.NMOS 버전은 1980년대 후반부터 10MHz 부품으로 생산되었습니다.CMOS 버전은 현재 판매되고 있는 버전의 경우 4MHz에서 최대 20MHz까지의 특정 상한 주파수로 개발되었습니다.CMOS 버전에서는 저전력 스탠바이로 내부 상태를 유지할 수 있었습니다.주파수 [viii]제한은 없습니다.완전히 호환되는 파생 모델 HD64180[18][19]/Z180 및 eZ80은 현재 각각 최대 33MHz와 50MHz로 지정되었습니다.

설계.

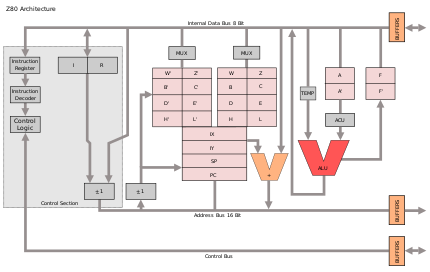

프로그래밍 모델 및 레지스터 세트

Z80의 프로그래밍 모델과 레지스터 세트는 매우 전통적인 것으로, 궁극적으로 Datapoint 2200의 레지스터 구조에 기초하고 있습니다.Z80은 같은 엔지니어가 개발한 인텔8080의 확장판으로서 설계되었으며, 이는 8008의 확장판입니다.8008은 기본적으로 Datapoint 2200의 [ix]TTL 기반 CPU의 PMOS 구현이었습니다.

2200 설계에서는 8비트 레지스터 H와 L(High and Low)을 16비트 주소 레지스터 HL로 [x]페어링할 수 있었습니다.8080에서는 이 페어링이 BC와 DE 쌍에도 추가되었지만 HL은 주소 레지스터뿐만 아니라 16비트 어큐뮬레이터로도 사용할 수 있도록 일반화되었습니다.또한 8080은 어큐뮬레이터 동작에 중요한8비트 즉시 데이터 모드와 HL, BC 및 DE 부하에 대한 즉시 16비트 데이터를 도입했습니다.또한 HL과 메모리 간에 다이렉트 주소를 사용하여 16비트를 직접 복사할 수 있게 되었습니다.

Z80은 IX 및 IY를 포함한 모든 16비트 레지스터 쌍을 보다 범용적으로 만들고 이러한 모든 쌍에 대해 메모리 간에 직접 16비트를 복사할 수 있도록 함으로써 이를 더욱 직교시켰습니다.Z80의 16비트 IX 및 IY 레지스터는 주로 기본 주소 레지스터를 목적으로 하며, 여기서 특정 명령은 이전 값에 추가되는 일정한 오프셋을 제공하지만 16비트 어큐뮬레이터로도 사용할 수 있습니다.IX 또는 IY를 포함하는 모든 오퍼랜드 참조에는 추가 명령 프리픽스바이트가 필요하며 대신 HL을 사용하는 명령 타이밍에 적어도4개의 클럭사이클이 추가됩니다.이로 인해 IX 또는 IY를 사용하는 것이 8080 모델레지스터만을 사용하는 방법보다 효율이 떨어지는 경우가 있습니다.또한 Z80은 새로운 서명 오버플로 플래그를 도입하여 서명된 16비트 산술 전용 명령어로 8080의 매우 단순한 16비트 산술을 보완했습니다.

8080 호환 레지스터 AF, BC, DE, HL은 Z80에서 [21]별도의 레지스터 파일로 복제됩니다.여기서 프로세서는 한 뱅크에서 다른 [22]뱅크로 신속하게 전환할 수 있습니다(4개의 t-상태, Z80 명령의 최소 실행 시간). 이 기능은 단일 레벨의 높은 우선순위의 인터럽트에 대한 응답을 고속화하는 데 유용합니다.2200 에는 같은 기능이 있었지만, 인텔에서는 실장되지 않았습니다.듀얼 레지스터 세트는 인터럽트 처리 성능을 향상시키므로 임베디드 역할에서 매우 유용하지만, 부동 소수점 연산이나 가정용 컴퓨터 게임과 같은 복잡한 코드의 추가 일반 레지스터 세트로 퍼스널 컴퓨터 역할에서 널리 사용되고 있습니다.

중복 레지스터 파일은 종종 "대체 레지스터 세트"라고 불립니다(어셈블러 소스 코드 및 Zilog 문서에서 아포스트로피 문자를 사용하여 "primed" 레지스터 파일입니다).이는 한 번에 하나의 세트만 주소 지정할 수 있음을 강조합니다.단, 플래그 레지스터 F를 가진 8비트 어큐뮬레이터 A는 "범용" 레지스터 쌍 HL, DE 및 BC에서 분기된다.이것은, 액세스의 스왑에 사용하는 다음의 2개의 개별의 순서에 의해서 실현됩니다.EX AF,AF'교환은 AF'와 페어 AF만 등록합니다.EXX명령은 3개의 범용 레지스터 쌍 HL, DE, BC를 대체 HL', DE' 및 BC'와 교환한다.따라서 어큐뮬레이터 A는 대체(또는 프라이밍) 레지스터 파일 내의 범용 8비트 레지스터 중 하나와 독립적으로 상호 작용할 수 있으며, HL'이 메모리에 대한 포인터를 포함하고 있는 경우에는 메모리 및 어큐뮬레이터 A 간에 8비트 데이터를 전송할 수도 있다.

이것은 프로그래머에게 혼란스러울 수 있습니다.실행 후EX AF,AF'또는EXX이전에는 대체(프라이밍) 레지스터였던 것이 이제는 메인 레지스터가 되고 그 반대의 경우도 마찬가지입니다.프로그래머가 어떤 세트가 컨텍스트에 있는지(어셈블러 소스 텍스트를 면밀히 조사하면서 "컴퓨터를 재생하는" 동안 또는 더 나쁜 것은 디버거로 코드를 검토하는 동안) 알 수 있는 유일한 방법은 프로그램의 각 지점에서 각 레지스터 스왑이 이루어지는 위치를 추적하는 것입니다.이러한 코드 세그먼트내에서 많은 점프나 콜이 행해지고 있는 경우는, 주의 깊게 코멘트를 하지 않는 한, 어느 레지스터 파일이 콘텍스트에 포함되어 있는지를 금방 판별하기 어려워질 가능성이 있습니다.따라서 교환 명령어는 직접 또는 짧은 이산 코드 세그먼트로 사용하는 것이 좋습니다.Zilog Z280 명령어 세트에는 다음이 포함됩니다.JAF그리고.JAR대체 레지스터가 컨텍스트에 있는 경우(이 프로그래밍 복잡성을 공식적으로 인식하는 경우) 수신처 주소로 점프하는 명령입니다.

레지스터

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

8080에서는 일반적으로 8비트 레지스터가 페어링되어 16비트 버전이 제공됩니다.8080 호환[23] 레지스터는 다음과 같습니다.

AF: 8비트 어큐뮬레이터(A) 및 플래그 비트(F)의 반송, 제로, 마이너스, 패리티/오버플로우, 하프캐리(BCD에 사용) 및 BCD에 대해서도 Add/Subtract 플래그(일반적으로 N)를 사용합니다.BC: 16비트 데이터/주소 레지스터 또는2개의 8비트 레지스터DE: 16비트 데이터/주소 레지스터 또는2개의 8비트 레지스터HL: 16비트 어큐뮬레이터/주소 레지스터 또는2개의 8비트 레지스터SP: 스택 포인터, 16비트PC: 프로그램 카운터, 16비트

Z80에 도입된 새로운 레지스터는 다음과 같습니다.

IX: 8비트 즉시 오프셋을 위한 16비트 인덱스 또는 베이스 레지스터IY: 8비트 즉시 오프셋을 위한 16비트 인덱스 또는 베이스 레지스터I: 인터럽트 벡터 베이스 레지스터, 8비트R: DRAM 리프레시 카운터, 8비트(msb는 카운트되지 않음)AF': 대체(또는 섀도) 축전지 및 플래그(EX AF, AF'로 태그 입력 및 출력)BC',DE'그리고.HL': 대체(또는 섀도) 레지스터(EXX를 사용하여 입력 및 출력)- 4비트 인터럽트 상태 및 인터럽트 모드 상태

리프레시 레지스터,RCPU가 opcode(1바이트 명령처럼 내부적으로 실행되는opcode prefix)를 취득할 때마다 증가하며 프로그램 실행과는 단순한 관계가 없습니다.이는 게임 및 소프트웨어 보호 방식에서 [citation needed]의사 난수를 생성하기 위해 사용되는 경우가 있습니다.일부 설계에서는 "하드웨어" 카운터로도 사용되고 있습니다.예를 들어 ZX81을 사용하면 랩 어라운드(INT를 A6에 접속함으로써)에서 인터럽트를 트리거하여 TV 화면의 문자 위치를 추적할 수 있습니다.

인터럽트 벡터 레지스터,I는 Z80 고유의 모드2 인터럽트에 사용됩니다(에 의해 선택됨).IM 2명령)을 참조해 주세요.인터럽트 확인 응답 사이클 중에 CPU로 전송되는 인덱스를 통해 선택되는 128 엔트리 서비스 루틴주소의 기본 주소의 높은 바이트를 제공합니다.이 인덱스는 단순히 서비스 [11]루틴을 가리키는 테이블 형식의 간접 주소에 대한 포인터의 낮은 바이트 부분입니다.포인터는 특정 주변기기의 칩, 주변기기의 기능 또는 이벤트를 나타냅니다.이 경우, 통상, 우선도 해결을 위해서 데이지 체인이라고 불리는 체인으로 칩이 접속되어 있습니다.리프레시 레지스터와 마찬가지로 이 레지스터도 때때로 창조적으로 사용되어 인터럽트 모드 0 및 1(또는 인터럽트를 사용하지 않는 시스템에서는 단순히 다른 8비트 데이터 레지스터로 사용될 수 있습니다.

순서LD A,R그리고.LD A,I다른 모든 것과 달리 Z80 플래그 레지스터에 영향을 줍니다.LD(부하) 지시.Sign(비트 7) 및 Zero(비트 6) 플래그는 Refresh 또는 Interrupt 소스 레지스터에서 로드된 데이터에 따라 설정됩니다.두 명령 모두 IFF2 플립 [24]플랍의 현재 상태에 따라 패리티/오버플로 플래그(비트 2)가 설정됩니다.

마이크로아키텍처

Z80은 일반적으로 8비트의 CPU로 간주되지만 4비트의 ALU를 탑재하고 있기 때문에 계산은 2주기로 [25]실시되었습니다.

Z80 어셈블리 언어

Datapoint 2200 및 Intel 8008

최초의 인텔8008 어셈블리 언어는 Datapoint 2200 설계에서 계승된 매우 단순한 (그러나 체계적인) 구문에 기초하고 있습니다.이 원래의 구문은 나중에 이 원래의 8008 칩을 위한 다소 전통적인 새로운 어셈블리 언어 형태로 변환되었습니다.이와 동시에 새로운 어셈블리 언어도 확장되어 보다 고도의 인텔 8080 칩의 추가 어드레싱 모드에 대응하고 있습니다(8008과 8080은 바이너리 호환성이 없는 언어 서브셋을 공유합니다만, 8008은 바이너리 호환성이 있습니다.

이 프로세스에서 니모닉은LLOAD의 경우 LOAD, STORE 및 MOVE라는 단어의 다양한 약자로 대체되었으며 다른 기호 문자와 혼합되어 있습니다.니모닉 레터M메모리(HL에 의해 참조됨)는 명령 니모닉 내에서 해제되어 구문적으로 자유로운 피연산자가 되었지만 레지스터와 레지스터의 조합은 명령 니모닉 자체(LDA, LXI H 등) 내에서 매우 일관되지 않게 나타납니다.ame 시간(LDAX B, STAX D 등).

| 인텔 8008 데이터 포인트 2200 | 인텔 8080 인텔 8085 | Zilog Z80 | 인텔 8086/ 인텔 8088 |

|---|---|---|---|

| 1973년 이전 | 1974년 | 1976 | 1978 |

LBC | MOV B,C | LD B,C | MOV BL,CL |

-- | LDAX B | LD A,(BC) | -- |

LAM | MOV A,M | LD A,(HL) | MOV AL,[BX] |

LBM | MOV B,M | LD B,(HL) | MOV BL,[BX] |

-- | STAX D | LD (DE),A | -- |

LMA | MOV M,A | LD (HL),A | MOV [BX],AL |

LMC | MOV M,C | LD (HL),C | MOV [BX],CL |

LDI 56 | MVI D,56 | LD D,56 | MOV DL,56 |

LMI 56 | MVI M,56 | LD (HL),56 | MOV byte ptr [BX],56 |

-- | LDA 1234 | LD A,(1234) | MOV AL,[1234] |

-- | STA 1234 | LD (1234),A | MOV [1234],AL |

-- | -- | LD B,(IX+56) | MOV BL,[SI+56] |

-- | -- | LD (IX+56),C | MOV [SI+56],CL |

-- | -- | LD (IY+56),78 | MOV byte ptr [DI+56],78 |

-- | LXI B,1234 | LD BC,1234 | MOV CX,1234 |

-- | LXI H,1234 | LD HL,1234 | MOV BX,1234 |

-- | SHLD 1234 | LD (1234),HL | MOV [1234],BX |

-- | LHLD 1234 | LD HL,(1234) | MOV BX,[1234] |

-- | -- | LD BC,(1234) | MOV CX,[1234] |

-- | -- | LD IX,(1234) | MOV SI,[1234] |

(8086의 경우) 동등한 샘플, 로드 및 저장 명령을 사용하여 [26]4개의 구문을 그림으로 나타냅니다.Z80 구문에서는 식 주위에 괄호를 사용하여 값을 메모리주소로 사용하는 것을 나타냅니다(아래 참조).8086 구문에서는 이 목적을 위해 일반 괄호 대신 괄호를 사용합니다.Z80과 8086 모두 + 기호를 사용하여 베이스 레지스터에 상수가 추가되어 주소가 형성됨을 나타냅니다.8086은 Z80의 완전한 슈퍼셋은 아닙니다.BX는 포인터로 사용할 수 있는 유일한 8086 레지스터 쌍입니다.

새로운 구문

인텔이 어셈블리 니모닉에 [27]대한 저작권을 주장했기 때문에 Z80용으로 새로운 어셈블리 구문을 개발해야 했습니다.이번에는 좀 더 체계적인 접근방식이 사용되었습니다.

- 모든 레지스터와 레지스터 쌍은 풀네임으로 명시되어 있습니다.

- 괄호는 하나의 점프 명령 JP(HL)를 제외하고 "메모리 내용 at"(정수 주소 또는 가변 포인터 참조)을 나타내기 위해 지속적으로 사용됩니다. JP(XY)는 새로운 PC 주소를 로드하는 JP(HL)의 변형일 뿐입니다.[xi]

- 모든 로드 및 스토어 명령은 LOAD에 대해 동일한 니모닉 이름 LD를 사용합니다(단순한 Datapoint 2200 어휘로 되돌립니다). ADD 및 INC 등의 기타 일반적인 명령에서는 주소 지정 모드 또는 오퍼랜드크기에 관계없이 동일한 니모닉을 사용합니다.이는 오퍼랜드 자체가 충분한 정보를 전달하기 때문에 가능합니다.

이러한 원리로 인해 모든 새로운 Z80 명령어의 이름과 형식을 쉽게 찾을 수 있을 뿐만 아니라 다음과 같은 이전 명령어의 직교화도 쉽게 찾을 수 있었습니다.LD BC,(1234).

명명상의 차이와 기본 레지스터 구조의 차이에도 불구하고 Z80과 8086 구문은 명령어의 많은 부분에서 사실상 동형입니다.8080 어셈블리 언어와 8086 어셈블리 언어 사이에는 상당히 피상적인 유사점(확장 레지스터의 경우 MOV 또는 문자 X 등)만 존재합니다.단, 8080 프로그램은 번역 프로그램을 [29][30]통해 8086 어셈블리 언어로 번역할 수 있습니다.

명령어 세트 및 부호화

Z80은 사용 가능한 256개의 코드 중 252개를 싱글 바이트의 opcode("루트 명령")로 사용합니다.나머지 4개의 코드는 opcode [31]프리픽스로 광범위하게 사용됩니다.CB 및 ED는 추가 명령을 활성화하며 DD 또는 FD는 각각 IX+d 또는 IY+d를 HL 대신 선택합니다.이 스킴에 의해 Z80은 다수의 명령어와 레지스터를 조합할 수 있습니다.Zilog는 이들을 158개의 다른 "명령어 타입"으로 분류합니다.이 중 78개는 인텔 8080[31] (Z80 상에서 모든 8080 프로그램을 동작시킬 수 있습니다)과 동일합니다.Zilog 문서에서는[32] 다음 범주(대부분 8080에서 나온 명령, 블록 및 비트 명령과 같은 완전히 새로운 명령 및 16비트 로드, I/O, 회전/시프트 및 상대 점프와 같은 보다 다용도 어드레싱 모드를 사용하는 다른 8080 명령)로 지침을 분류합니다.

- 로드 및 교환

- 블록 전송 및 검색

- 산술과 논리

- 회전 및 이동

- 비트 조작(설정, 리셋, 테스트)

- 점프, 콜 및 리턴

- 입력/출력

- 기본적인 CPU 제어

레지스터 A와 [33]HL은 ADD A, A 및 ADD HL, HL 명령으로 2의 거듭제곱할 수 있지만 원래의 Z80에서는 명시적인 곱셈 명령을 사용할 수 없습니다(IX와 IY도 마찬가지).시프트 명령은 2의 거듭제곱으로 곱하거나 나눌 수도 있습니다.

8080의 플래그 변경 속성 대부분이 복사되었기 때문에 추가, 이동 및 회전의 크기와 변형에 따라 플래그에 미치는 영향이 다소 다릅니다.다만, 8080(비트 2)의 패리티 플래그 비트 P는, 8080에는 없는 기능인 2개의 보완 오버플로 인디케이터의 추가 목적에 대응하고 있기 때문에, Z80에서는 P/V(패리티/오버플로우)라고 불립니다.Z80의 산술 명령에서는 패리티가 아닌 오버플로우를 나타내도록 설정되어 있지만 비트 명령에서는 여전히 패리티 플래그로 사용되고 있습니다.(이는 Z80이 8080을 위해 작성된 코드와의 미묘한 비호환성을 나타냅니다.Z80은 때때로 8080이 패리티를 나타내는 서명된 오버플로우를 나타내므로 일부 pra의 논리가 발생할 수 있습니다.Cic 8080 소프트웨어에서 장애가 발생할 수 있습니다.[xii]이 새로운 오버플로 플래그는 모든 새로운 Z80 고유의 16비트 작업에 사용됩니다(ADC,SBC또한 8비트 연산에서는 16비트 연산에서는 8080에서 상속됩니다(ADD,INC,DEC)는 영향을 주지 않습니다.또, 플래그 레지스터의 비트 1(8080의 스페어 비트)은, 마지막으로 실행된 연산 명령이 감산인지 덧셈인지를 나타내는 플래그 N으로서 사용된다.의 Z80 버전DAA명령(BCD 산술용 10진수 조정 어큐뮬레이터)은 N 플래그를 체크하고 그에 따라 동작하기 때문에 (가상의) 차감 후 나중에 이어집니다.DAA구형 8080에서는 Z80과는 다른 결과를 얻을 수 있습니다.단, 이것은 8080에서는 에러 코드일 가능성이 있습니다.DAA는, 그 프로세서에 추가용으로만 정의되어 있습니다.

Z80에는 6개의 새로운 기능이 탑재되어 있습니다.LD8080과는 [34]달리 DE, BC 및 SP 레지스터 쌍을 메모리에서 로드하고 이들 3개의 레지스터 쌍에서 메모리를 로드할 수 있는 명령입니다.8080과 마찬가지로 로드 명령은 플래그에 영향을 주지 않습니다(특수 목적 I 및 R 레지스터 로드 제외).정규 부호화(8080과 공통)의 결과, 각 8비트 레지스터를 자신으로부터 로드할 수 있습니다(예를 들면).LD A,A) 이것은 사실상NOP.

새로운 블록 전송 명령에서는 메모리에서 메모리로 또는 메모리와 I/O 주변 포트 간에 최대 64킬로바이트를 이동할 수 있습니다.차단 명령LDIR그리고.LDDR(LoaD, Increment/Decrement, Repeat) 는, HL 를 사용해 송신원주소를 가리키고, DE 를 행선지 주소를 가리키고, BC 를 바이트카운터로 사용합니다.바이트는 송신원으로부터 수신처에 카피되어 포인터는 증가 또는 감소해, 바이트 카운터는 BC가 제로가 될 때까지 감소합니다.비반복 버전LDI그리고.LDD1바이트를 이동하고 포인터와 바이트 카운터를 범프합니다.이 카운터가 0이 되면 P/V 플래그가 리셋됩니다.대응하는 메모리-투-I/OINIR,INDR,OTIR,OTDR,INI,IND,OUTI그리고.OUTD동일하게 동작합니다.Z80은 레지스터 C를 사용하여 I/O 포트에 모든 레지스터를 입력 및 출력하여 포트를 지정할 수 있습니다(8080은 명령에서 지정된 직접 포트 주소를 사용하여 어큐뮬레이터 A를 통해서만 I/O를 수행합니다.변수 8080 포트 주소를 사용하려면 자체 수정 코드 기술이 필요합니다).

블록 명령의 마지막 그룹은CP(HL)에서 바이트와 축전지 A 사이의 연산을 비교합니다.레지스터 쌍 DE는 사용되지 않습니다.반복 버전CPIR그리고.CPDRBC가 0이 되거나 일치하는 것이 발견된 경우에만 종료됩니다.HL은 (다음)의 바이트를 가리키고 있습니다.CPIR또는 그 이전(CPDR일치하는 바이트).일치하는 항목이 없으면 Z 플래그가 재설정됩니다.반복되지 않는 버전이 있습니다.CPI그리고.CPD.

8080과는 달리 Z80은 상대 주소로 점프할 수 있습니다.JR대신JP)를 사용합니다.이 새로운 2바이트에서는 제로 플래그와 캐리 플래그만 테스트할 수 있습니다.JR(조건에 관계없이 8080 점프 및 콜은 모두 3바이트 명령입니다.)프로그램 루프에 특화된 2바이트 명령도 Z80에 새로 추가되었습니다.DJNZ(제로가 아닌 경우 감쇠 점프)는 즉시 오퍼랜드로서 부호 있는8비트 치환을 취합니다.B 레지스터는 감소하며, 결과가 0이 아닌 경우 PC에 대해 프로그램 실행이 점프합니다. 플래그는 변경되지 않은 상태로 유지됩니다.8080에서 동등한 루프를 실행하려면 별도의 루프가 필요합니다.DEC수정 및 조건부 점프(2바이트 절대 주소로) 명령(합계 4바이트) 및DEC플래그 레지스터를 변경합니다.

인덱스 레지스터(IX/IY, 종종 생략된 XY) 명령은 고정 이기종 구조(레코드 등) 또는 가변 베이스 주소(재귀적 테스트 프레임 등)에 상대적인 고정 오프셋으로 구성된 데이터에 액세스하는 데 유용할 수 있으며, 인덱스되지 않은 레지스터를 사용하여 여러 짧은 명령을 사용할 필요가 없으므로 코드 크기를 줄일 수 있습니다.단, 심플한 동작의 장/복잡한 동등한 시퀀스에 비해 컨텍스트에 따라서는 속도가 저하될 수 있지만, HL을 사용하여 동일한 메모리에 액세스하기 위해서는 1개의 인덱스 메모리 위치에 액세스하기 위해 19T 상태보다 많은 CPU 시간이 소요됩니다(예를 들어 HL과 HL을 사용하여 동일한 메모리에 액세스하기 위해 11T 상태).INC다음 항목을 가리킵니다).따라서 데이터에 대한 단순 또는 선형 액세스의 경우 IX 및 IY의 사용이 느리고 메모리를 더 많이 사용하는 경향이 있습니다.그러나 레지스터를 저장/복원할 필요가 없으므로 '메인' 레지스터가 모두 점유된 경우에도 유용할 수 있습니다.공식 문서화되어 있지 않은8비트 하프(아래 참조)는 특히 도움이 됩니다.이는 16비트 부모보다 속도가 느려지지 않기 때문입니다.마찬가지로 16비트 추가 명령어는 원래 Z80에서는 특별히 고속(11클럭)이 아닙니다(8080/8085보다 1클럭 느림).다만, 8비트 연산을 사용해 같은 계산을 실행하는 것보다 약 2배 고속이며, 마찬가지로 중요한 것은 레지스터의 사용율을 낮춥니다.프로그래머가 (일반적으로 동적으로 계산되는) 다른 오프셋 변위 바이트를 인덱스된 명령어에 "포킹"하는 것은 드문 일이 아닙니다.이것은 파이프라인되지 않은 실행 유닛을 가진 거의 모든 초기 8비트 프로세서에서 정기적으로 행해지던 자기 수정 코드의 예입니다.

인덱스 레지스터에는 다음과 같은 병렬 명령이 있습니다.JP (HL),어느 것이JP (XY)이것은 포스와 같은 스택 지향 언어에서 자주 볼 수 있습니다. 포스 워드(그 언어를 구성하는 아토믹서브루틴)의 말미에 반드시 스레드 인터프리터 루틴으로 돌아가야 합니다.일반적으로 이 점프 명령은 응용 프로그램에 수백 번 표시되며,JP (XY)보다는JP THREAD는 각 오카렌스마다 1바이트 및2개의 T스테이트를 저장합니다.이로 인해 인덱스 레지스터를 다른 용도로 사용할 수 없게 됩니다.그렇지 않으면 인덱스 레지스터를 지속적으로 새로고침해야 하므로 효율성이 저하됩니다.

10년 동안 마이크로코딩된 Z180 설계로 처음에는 더 많은 "칩 영역"을 확보할 수 있게 되어 (특히 더 넓은 ALU를 사용하여) 약간 더 효율적으로 구현할 수 있게 되었습니다. Z800, Z280 및 Z380도 이와 유사하다고 할 수 있습니다.그러나 2001년에 완전히 파이프라인화된 eZ80이 출시되고 나서야 이러한 명령어는 기술적으로 만들 수 있는 만큼 사이클 효율적이 되었습니다. 즉, Z80 인코딩을 조합하여 클럭 [citation needed]사이클마다 8비트 읽기 또는 쓰기를 수행할 수 있습니다.

문서화되어 있지 않은 순서

인덱스 레지스터인 IX와 IY는 메모리, 스택 프레임 및 데이터 구조를 조작할 수 있는 기능을 강화한 유연한 16비트 포인터로 설계되었습니다.공식적으로는 16비트만 취급되었습니다.실제로는 HL 레지스터와 같은 방식으로 8비트 레지스터 [35]쌍으로 구현되었으며, HL 레지스터는 16비트 또는 High 및 Low 레지스터와 별도로 액세스할 수 있습니다.바이너리 opcode(기계어)는 동일하지만 앞에 새로운 opcode prefix가 [36]붙습니다.Zilog는 의도된 함수에 대한 opcode 및 관련 니모닉을 공개했지만 H 및 L 레지스터를 조작할 수 있는 모든 opcode가 IX 및 IY 레지스터의 8비트 부분에 대해 동등하게 유효하다는 사실은 문서화하지 않았습니다.예를 들어 opcode 26h 뒤에 즉시 바이트 값이 표시됩니다.(LD H,n)이 값은 H 레지스터에 로드됩니다.IX 레지스터의 opcode prefix인 DD를 사용하여 이 2바이트 명령을 실행하면 대신 IX 레지스터의 최상위 8비트가 동일한 값으로 로드됩니다.여기서 주목할 만한 예외는 다음과 같은 절차입니다.LD H,(IX+d)는 같은 명령어로 [36]HL과 IX 또는 IY 레지스터를 모두 사용합니다.이 경우 DD 프리픽스는 명령어의 (IX+d) 부분에만 적용됩니다.XY 레지스터의 절반에는 8비트 산술, 논리 및 비교 명령을 위한 피연산자(operand)가 저장되며, 일반 8비트 레지스터는 다른 용도로 사용할 수 없습니다.색인 레지스터의 상부를 증감하는 문서화되지 않은 기능은 문서화된 명령어에 의존하지 않고도 일반적인 색인화된 명령의 범위를 쉽게 확장할 수 있게 했다.ADD/SBC XY,DE또는ADD/SBC XY,BC.

문서화되어 있지 않은 다른 지침도 [37]몇 가지 있습니다.문서화되어 있지 않거나 부정한 opcode는 Z80에 의해 검출되지 않고 다양한 효과가 있으며, 그 중 몇 가지는 도움이 됩니다.그러나 명령어 세트의 정식 정의의 일부가 아니기 때문에 Z80의 다른 구현은 문서화되지 않은 모든 opcode에 대해 동일한 방식으로 동작하는 것을 보증하지 않습니다(특히 가능성이 높습니다).

버그

그OTDR지침이 Z80 설명서에 부합하지 않습니다.둘 다OTDR그리고.OTIR명령어는 carry(C) 플래그를 변경하지 않은 상태로 둡니다.그OTIR명령어는 올바르게 동작합니다.다만, 실행중에,OTDR명령, carry 플래그는 축적기(A)와 마지막 출력 사이의 스플리어스 비교 결과를 취합니다.OTDR사용설명서.[38]

코드 예시

예 1: 다음 Z80 어셈블러의 소스 코드는 HELLO_WORLD라는 서브루틴용입니다.이것은 비디오 디스플레이에 메시지를 인쇄하고 종료하는 입문 프로그램입니다.단순하지만 어셈블러 소스 코드가 포맷되어 컴퓨터 운영 체제를 통해 디스플레이 하드웨어와 상호 작용하는 방법을 보여줍니다.이는 특정 컴퓨터 하드웨어, 운영 체제 및 어셈블러 소프트웨어에 고유해야 합니다.사용되는 예는 다음과 같습니다.

TRS-80 모델4는 Tandy/Radio Shack 및 Logical Systems에서 생산되며 대부분의 어셈블러는 Radio Shack 또는 Misosys Inc.(시리즈 I/EDASM, ALDS, EDAS 또는 MRAS -C 스위치 포함)에서 판매됩니다.이 구성의 주요 기능은 CP/M 하에서도 Z80 어셈블러에 보편적입니다.

3000 3E 69 3002 EF 3003 21 14 30 3006 3E 0A 3008 EF 3009 0E 02 300B 3E 02 300D EF 300E 21 00 3011 3E 16 3013 EF 3014 48 65 6C 3018 6F 77 301C 72 020 C 620 C | ; hello_world_TRS-80 모델4 ; "Hello, world!" 라고 인쇄한 후 TRSDOS Ready로 종료합니다. ; ; 엔트리 레지스터: 없음 ; 반환 레지스터: 없음 ; ; 아래 값은 H로 접미사가 붙지 않는 한 10진수입니다. "seudo-op"이라는 용어는 "assembler direction"과 동일하며 Z80 코드가 아닙니다. ; @CLS EQU 105 ; EQU 유사 op sets @CLS 텍스트라벨 = TRSDOS 슈퍼바이저 코드 @DSP EQU 2 ; set @DSP text label = TRSDOS SVC가 char를 표시로 전송하도록 설정합니다. @DSPLY EQU 10 ; 텍스트 문자열 표시를 위해 @DSPLY 텍스트라벨 = SVC를 설정합니다. @종료 EQU 22 ; @EX 설정IT 텍스트 라벨 = TRSDOS Ready로 돌아가기 위한 SVC ; 조직 3000H ; ORG 유사 운영은 TRSDOS 6.x에서 표준 시작 주소를 설정합니다. 기동 LD A,@CLS ; CLS = 화면 지우기, 디스플레이 지우기 및 커서 홈 RST 40 ; Z80 시스템 SVC 프로세서의 재부팅 명령, @CLS 실행 LD HL,MSG ; HL이 있는 메시지 문자열을 가리킵니다(@DSPLY SVC에서 필요). LD A,@DSPLY 텍스트 문자열을 *DO Display Output 디바이스(비디오 화면)로 전송합니다. RST 40 ; @DSPLY SVC를 실행합니다(문자열을 종료하려면 13d바이트 필요). LD C,13 ; 이제 Reg C에서 필요한 다른 캐리지 리턴을 보냅니다. LD A,@DSP ; TRSDOS Ready 프롬프트에서 Hello 메시지를 소거합니다. RST 40 시스템 종료 후 LD HL,0 ; 명령어 인터프리터에 에러 상태가 없음을 나타냅니다. LD A,@종료 ; TRSDOS Ready로 돌아갑니다. RST 40 ;(스택의 무결성이 유지되고 있습니다.RET를 사용하는 것이 좋을지도 모릅니다. MSGDB 안녕, 세상아!,13 ; DB = Define Byte 유사 연산으로 ASCII 문자열을 Z80 메모리에 어셈블합니다. CRDB 13 ; 13d 바이트는 ASCII 캐리지 리턴 문자이며 커서를 아래로 이동합니다. 끝. 기동 ; 조립자가 필요로 하는 END 의사 조작 ; 프로그램 진입점으로 전송 레코드를 생성한다. |

예 2: 다음 Z80 어셈블리소스 코드는 서브루틴용입니다memcpy특정 크기의 데이터 바이트 블록을 한 위치에서 다른 위치로 복사합니다.중요: 이 예에서는, 행선지 블록이 송신원과 겹치는 경우는 취급하지 않습니다.심각한 제한이지만, 일부 애플리케이션(특히, 송신원이 ROM 에 있는 경우나 행선지가 RAM 에 있는 경우 등)에는 관계없는 코드입니다.이러한 코드는, 중복하는 일이 없습니다.샘플 코드는, 속도의 베스트 프랙티스가 아니고, 다양한 명령의 타입을 나타내기 위해서, 지극히 비효율적입니다.데이터 블록은 한 번에 1바이트씩 복사되며 데이터 이동 및 루프 로직은 16비트 연산을 사용합니다.또한 Z80에는 루프 전체를 실행하는 단일 명령이 있습니다.LDIR조립된 코드는 인텔 8080 및 8085 CPU와 바이너리 호환성이 있습니다.

천 1000 1000 78 1001 B1 1002 C8 1003 1A 1004 77 1005 13 1006 23 1007 08 C3 00 10 100B | ; memcpy -- ; 메모리 블록을 한 위치에서 다른 위치로 복사합니다. ; ; 엔트리 레지스터 ; BC - 복사할 바이트 수 ; DE - 소스 데이터 블록의 주소 ; HL - 대상 데이터 블록의 주소 ; ; 레지스터 반환 ; BC - 제로 조직 1000시간 원점: 1000h 메모리 일반의 고리 ld a,b 테스트 BC, 또는 c BC = 0이면 리트 z 반환 ld a,(데) (DE)에서 A를 로드합니다. ld (hl),a A를 (HL)에 저장 주식회사 데 증가 DE 주식회사 hl 인크리먼트 데크 bc 기원전 10월 JP 고리 루프를 반복합니다. 끝. |

명령 실행

각 명령은 보통 기계 주기(M-cycle)라고 불리는 단계로 실행되며, 각 단계는 3~6 클럭 주기(T-상태)[39]가 걸릴 수 있습니다.각 M 사이클은 대략 1개의 메모리액세스 또는 내부 조작에 대응합니다.실제로 많은 명령어가 다음 명령어의 M1 중에 종료됩니다.이 명령어는 fetch/execute 오버랩으로 알려져 있습니다.

| 총 M사이클 | T-상태 | 설명 | M1 | M2 | M3 | M4 | M5 | M6 |

|---|---|---|---|---|---|---|---|---|

| 1개[40] | 4개[1] | INC B | 동작 코드 | |||||

| 2개[41] | 7 | ADD A,n | 동작 코드 | n | ||||

| 3개[42] | 11 | ADD HL,DE | 동작 코드 | 내부의 | 내부의 | |||

| 4개[43] | 15 | SET b,(HL) | 접두사 | 동작 코드 | R(HL), 설정 | W(HL) | ||

| 5개[44] | 19 | LD (IX+d),n | 접두사 | 동작 코드 | d | n, 추가 | W(IX+d) | |

| 6개[45] | 23 | INC (IY+d) | 접두사 | 동작 코드 | d | 더하다 | R(IY+d), inc | W(IY+d) |

Z80 기계 사이클은 컨텍스트에 따라 3, 4, 5 또는 6개의 T-상태 중 각 M-사이클을 구축하는 내부 상태 기계에 의해 시퀀싱됩니다.이것에 의해, 번거로운 비동기 로직이 회피되어 제어 신호가 폭넓은 클럭 주파수로 일관되게 동작합니다.이는 또한 기계 사이클의 세분화가 없는 경우(약 2~3배 더 높음)보다 더 높은 주파수 결정을 사용해야 한다는 것을 의미합니다.고해상도 클럭을 사용하면 메모리 타이밍을 보다 정확하게 제어할 수 있기 때문에 사용 가능한 메모리 [citation needed]대역폭을 보다 효율적으로 사용할 수 있기 때문에 메모리 액세스 시간이 엄격해지는 것은 아닙니다.

예를 들어, opcode fetch의 경우 Z80은 2개의 풀클럭 사이클을 메모리액세스 기간(M1 신호)에 결합합니다.Z80에서는 이 신호가 6800, 6502 등의 설계보다 일반적인 명령 실행 시간의 비교적 큰 부분 동안 지속됩니다.이 설계에서는 일반적으로 클럭 [citation needed]사이클의 30~40%가 지속됩니다.일반적으로 메모리 칩의 가격(1980년대에는[citation needed] 450~250ns의 액세스 시간)이 가장 빠른 액세스 시간을 결정하므로 이러한 설계는 Z80보다 훨씬 긴 클럭 사이클(즉, 내부 클럭 속도)로 고정되었습니다.

메모리는 일반적으로 현재의 마이크로프로세서에 사용되는 상태 머신의 서브사이클(클럭 사이클)에 비해 느렸습니다.따라서 임베디드 설계에서 안전하게 사용할 수 있는 가장 짧은 기계 사이클은 최대 CPU 주파수가 아닌 메모리 액세스 시간에 의해 제한되는 경우가 많습니다(가정 컴퓨터 시대에는 특히 그렇습니다).그러나 이러한 관계는 특히 SRAM과 관련하여 지난 수십 년 동안 서서히 변화해 왔습니다. 따라서 eZ80과 같은 캐시리스 단일 사이클 설계는 최근 훨씬 더 의미가 있습니다.

리프레시 레지스터 R의 내용은 CPU가 취득한 명령을 디코딩하여 실행하는 동안 리프레시 제어 신호와 함께 주소 버스의 하부에 송신된다.인터럽트 레지스터의 내용을 새로 고치는 동안 주소 [46]버스의 윗부분을 통해 전송됩니다.

호환성이 있는 주변기기

Zilog는 Z80의 인터럽트 처리 시스템과 I/O 주소 공간을 모두 지원하는 Z80을 위한 많은 주변기기를 도입했습니다.여기에는 CTC(Counter/[47]Timer Channel), SIO(Serial Input Output), DMA(Direct Memory Access), PIO(Parallel Input-Output) 및 DART(Dual Asynchronous Receiver Transmitter)가 포함됩니다.제품 라인이 발전함에 따라 이들 칩의 저전력, 고속 및 CMOS 버전이 도입되었습니다.

8080, 8085 및 8086 프로세서와 마찬가지로 Motorola 6800 및 MOS Technology 6502와 같은 프로세서와 달리 Z80 및 8080에는 I/O 명령을 위한 별도의 제어 라인과 주소 공간이 있습니다.Osborne 1과 같은 일부 Z80 기반 컴퓨터는 "모토롤라 스타일" 메모리 매핑 입출력 장치를 사용했지만, 대개 입출력 공간은 Z80과 호환되는 많은 Zilog 주변 칩 중 하나를 처리하기 위해 사용되었습니다.Zilog I/O 칩은 Z80의 새로운 모드 2 인터럽트를 지원하여 다수의 주변기기를 위한 인터럽트 처리를 단순화하였습니다.

Z80은 공식적으로 16비트(64KB) 메모리 어드레싱과 8비트(256포트) I/O 어드레싱을 지원하는 것으로 설명되었습니다.모든 I/O 명령은 실제로 16비트 주소 버스 전체를 아사트합니다.OUT (C), reg 및 IN reg, (C)는 16비트 BC 레지스터 전체의 내용을 어드레스 [38]버스에 배치하고, OUT (n), A 및 IN A, (n)는 어드레스 버스의 b8~b15에, n은 어드레스 버스의 b0~b7에 배치한다.설계자는 이 기능을 이용하기 위해 16비트 주소 버스 전체를 I/O 동작으로 디코딩하거나 주소 버스의 상위 절반을 사용하여 I/O 디바이스의 하위 기능을 선택할 수 있습니다.이 기능은 Amstrad CPC/PCW 및 ZX81과 같은 디코딩 하드웨어 요건을 최소화하기 위해서도 사용되고 있습니다.

두 번째 소스 및 파생상품

두 번째 소스

Zilog용 Z80을 최초로 생산한 Mostek은 MK3880으로 세컨드 소스로 제공했습니다.SGS-Thomson(현재의 STMicroelectronics)도 Z8400과 함께 세컨드 소스로 제공되었습니다.샤프와 NEC는 각각 NMOS Z80, LH0080, μPD780C의 두 번째 소스를 개발했다.LH0080은 샤프와 소니 MSX 컴퓨터, 그리고 샤프 MZ [48]시리즈의 많은 일본 제조업체에 의해 만들어진 다양한 가정용 컴퓨터와 개인용 컴퓨터에 사용되었다.

도시바는 CMOS 버전인 TMPZ84C00을 만들었는데, 이는 Zilog가 자체 CMOS Z84C00에도 사용한 것과 동일한 디자인으로 생각됩니다[by whom?](그러나 검증되지는 않았습니다).골드스타(현 LG)가 만든 Z80칩과 NMOS, ROHM전자가 만든 CMOS의 Z80클론(DMA, PIO, CTC, DART, SIO 포함) BU18400 시리즈도 있었다.

동독에서는 U880으로 알려진 무면허 복제 Z80이 제조되었다.Robotron's 및 VEB Mikroelktronik Muhlhausen의 컴퓨터 시스템(KC85 시리즈 등) 및 많은 자체 제작 컴퓨터 시스템에도 광범위하게 사용되었습니다.루마니아에서는 MMN80CPU라는 이름의 또 다른 무면허 복제품이 발견될 수 있으며 TIM-S, HC, COBRA와 같은 가정용 컴퓨터에 사용되는 마이크로 일렉트로니카에서 생산된다.

또한 소련에서는 Z80의 여러 클론이 생성되었으며, 그 중 대표적인 것이 T34BM1(소련의 8080-클론 KR580VM80A와 병행)이다.첫 번째 마킹은 사전 제작 시리즈에서 사용되었고, 두 번째 마킹은 더 큰 제작에 사용되었습니다.그러나 1980년대 후반 소련의 마이크로일렉트로닉스 붕괴로 T34BM1은 s1858 [citation needed]s1보다 더 많다.

파생상품

- 오리지널 Z80과의 호환성

- Hitachi는 칩 주변기기와 1MB의 간단한 MMU를 갖춘 CMOS의 마이크로코딩된 부분 동적 Z80인 HD64180을 개발했습니다.나중에 Zilog가 Z64180으로 두 번째 소싱한 후 Z80 주변 칩에 더 잘 적응된 버스 프로토콜과 타이밍을 가진 약간 수정된[49] Z180의 형태로 제공되었습니다.Z180은 Zilog라는 이름으로 유지되고 있으며, 최신 버전은 전력 소비량이 매우 낮은 완전 정적 S180/L180 코어와 EMI(노이즈)를 기반으로 합니다.

- 도시바는 84핀 Z84013/Z84C13과 100핀 Z84015/Z84C15 시리즈의 "인텔리전트 페리페럴 컨트롤러"를 개발했습니다.이는 기본적으로 Z80 주변기기를 갖춘 일반 NMOS 및 CMOS Z80 코어, 워치독 타이머, 전원 켜기 리셋 및 대기 상태 제너레이터입니다.도시바뿐만 아니라 샤프도 제조.이 제품들은 현재 Zilog가 [50]두 번째로 공급하고 있습니다.

- 1994년에 출시된 32비트 Z80 호환 Zilog Z380은 주로 통신 [citation needed]기기에 사용됩니다.

- 8/16/24비트 워드 길이와 16MB의 선형 주소 공간을 갖춘 Zilog의 완전 파이프라인형 Z80 호환 eZ80은[51] 2001년에 도입되었습니다.온칩 SRAM 또는 플래시 메모리를 탑재한 버전 및 내장 주변기기를 탑재한 버전으로 존재합니다.1개의 변종에는 온칩 MAC(미디어 액세스컨트롤러)가 있으며, 이용 가능한 소프트웨어에는 TCP/IP 스택이 포함되어 있습니다.Z800 및 Z280과는 달리 추가된 명령어는 몇 개(주로 LEA, PEA 및 가변 주소 16/24비트 로드)뿐이지만 명령어는 원래 Z80의 2배에서 11배(평균값 약 3~5배)의 클럭 사이클 효율로 실행됩니다.현재 최대 50MHz의 클럭 주파수로 지정되어 있습니다.

- 가와사키는 오리지널 Z80의 약 1.2~1.3배의 클럭 사이클 효율과 최대 33MHz 클럭이 가능한 바이너리 호환 KL5C8400을 개발했습니다.또한 가와사키는 주변기기와 소형 RAM on 칩을 탑재한 KL5C80A1x 패밀리를 생산하고 있습니다.클럭 효율은 대략적으로 e80Z와 같습니다.o 10MHz(2006년).[52]

- NEC μPD9002는 Z80 및 x86 패밀리와 호환되는 하이브리드 CPU였습니다.

- Chinese Actions Semiconductor의 오디오 프로세서 패밀리 칩(ATJ2085 및 기타)에는 Z80 호환 MCU와 24비트 전용 DSP [53]프로세서가 포함되어 있습니다.이 칩들은 많은 MP3와 미디어 플레이어 제품에 사용된다.

- T80(VHDL)과 TV80(Verilog)의 합성 가능한 소프트 코어는, [54]OpenCores.org 에서 입수할 수 있습니다.

- 1980년에 발표된[55] National Semiconductor NSC800은 많은 TeleSecurity Timmann(TST) 전자 암호[56] 머신 및 Canon X-07에 사용되고 있습니다.NSC800은 Z-80 지침 [57]집합과 완전히 호환됩니다.NSC800은 8085와 같은 멀티플렉스 버스를 사용하지만 Z80과는 [58]핀 배치가 다릅니다.

- 비호환성

- Toshiba TLCS 900 시리즈의 대용량(대부분 OTP) 마이크로 컨트롤러는 Z80을 기반으로 하며, 기본적인 BC, DE, HL, IX, IY 레지스터 구조와 거의 동일한 명령을 공유하지만 이전 TLCS 90은 Z80과 [59]호환성이 없습니다.

- NEC 78K 시리즈 마이크로컨트롤러는 Z80을 기반으로 하며 동일한 기본 BC, DE, HL 레지스터 구조를 공유하며 바이너리 호환성이 없는 유사한 명령(다른 이름)을 가지고 있습니다.

- 부분 호환

- Rabbit Semiconductor의 Rabbit 2000/3000/4000 마이크로프로세서/마이크로컨트롤러는[60] HD64180/[61]Z180 아키텍처를 기반으로 하지만 완전히 이진 호환되지는 않습니다.

- 더 이상 생산되지 않음

- ASCII Corporation R800은 MSX TurboR 컴퓨터에 사용되는 고속 16비트 프로세서입니다.소프트웨어였지만 Z80과의 하드웨어 호환성은 없었습니다(신호 타이밍, 핀 배치 및 핀 기능은 Z80과 다릅니다).

- Zilog의 NMOS Z800과 CMOS Z280은 16MB의 페이지 MMU 주소 공간을 가진 (HD64180/Z180 이전) 16비트 Z80 구현이었습니다. Z80 명령 세트에 많은 직교화 및 주소 지정 모드를 추가했습니다.Minicomputer 기능 사용자 및 시스템 모드, 다중 처리기 지원 등, 칩 MMU에, 칩 명령과 데이터 캐시도 그렇고 —에 기능성과 그(보통 electronics-oriented)포함된 시스템 디자이너에 대한 지원 때보다 더 복잡성보다는 보였다 —, 그것은 또한 그것은 매우 힘든 명령어 실행 시간을 예측하기로 했다.[표창 필요한]

- Pang/Buster Brothers와 같은 일부 아케이드 게임에서는 VLSI 테크놀로지에 의해 제조된 암호화된 "Kabuki" Z80 CPU를 사용하여 복호화 키를 내장 배터리 백업 메모리에 저장하여 불법 부트레그 [62]게임을 방지합니다.

주목할 만한 용도

데스크톱 컴퓨터

1970년대 후반과 1980년대 초반 Z80은 CP/M 운영체제를 탑재한 익명의 비즈니스 지향 머신에 많이 사용되었습니다.이러한 [63][64]조합은 당시 시장을 지배하고 있었습니다.CP/M을 실행하는 Z80 비즈니스 컴퓨터의 4가지 유명한 예로는 Heathkit H89, 휴대용 Osborne 1, Kaypro 시리즈 및 Epson QX-10이 있습니다.덜 알려진 것은 비싼 고급 오트로나 [65]어태치였다.일부 시스템에서는 멀티태스킹 운영체제 소프트웨어(MP/M이나 Morrow의 Micronix 등)를 사용하여 하나의 프로세서를 여러 사용자 간에 공유했습니다.

Z80을 메인 프로세서 또는 플러그인 옵션으로 사용하여 Z80용으로 작성된 소프트웨어에 액세스할 수 있는 여러 가정용 컴퓨터가 도입되었습니다.TRS-80 시리즈에는, 원래의 모델(나중에 「모델 I」로 개칭), 모델 II, 모델 III, 및 모델 4가 있습니다.이러한 모델에는 Z80이 메인 프로세서 또는 세컨더리 프로세서로 탑재되어 있습니다.그 밖에 주목되는 머신으로는 인텔 8088과 Z80 CPU를 탑재한 DEC Rainbow 100과 Seequa Cameleon이 있으며, Z80 상에서 동작하는8비트 CP/M-80 어플리케이션 또는 8088 상에서 동작하는 PC DOS 어플리케이션과 완전히 호환되지 않는 커스텀 MS-DOS가 있습니다.

1981년 Multitech(나중에 Acer가 됨)는 Z80 마이크로프로세서를 위한 간단하고 저렴한 훈련 시스템인 Microfessor I을 발표했습니다.현재, 그것은 여전히 영국 사우샘프턴에 있는 Flite Electronics International Limited에 의해 제조되고 판매되고 있다.

1984년 도시바는 일본과 호주에서 도시바 MSX HX-10을 선보였다.

1985년 샤프는 Hotbit를, Gradiente는 1980년대 후반까지 브라질에서 지배적인 8비트 가정용 컴퓨터가 된 Expert를 발표했습니다.

휴대용 및 핸드헬드 컴퓨터

Z80은 CMOS 버전의 프로세서를 이용할 수 있게 되면서 배터리 구동 장치의 경량화에 대한 사용이 더욱 확산되었습니다.또한 샤프의 LH5801과[66] 같은 다른 CMOS 기반 프로세서의 개발에도 영감을 주었습니다.베이직 프로그램 가능한 포켓 컴퓨터인 샤프 PC-1500은 1981년에 출시되었고, 1986년에 개선된 샤프 PC-1600과 1991년에 샤프 PC-E220이 출시되었습니다.샤프 마법사 시리즈의 최신 모델도 Z80에 기반을 두고 있습니다.데스크톱 머신과 마찬가지로 CP/M 운영체제를 실행할 수 있는 노트북은 1984년 Epson PX-8 Geneva, 1985년 Epson PX-4 및 Bondwell-2에 이어 출시되었습니다.이후 노트북 시장은 더욱 강력한 인텔 8086 프로세서와 MS-DOS 운영체제로 옮겨갔지만 1988년 캠브리지 Z88과 1992년 Amstrad NC100과 같이 배터리 수명이 긴 경량 Z80 기반 시스템이 여전히 도입되고 있었습니다.Z80에서 파생된 Z8S180은 또한 1993년에 펜으로 작동하는 개인 디지털 보조기, Amstrad PenPad PDA600에 보급되었다.홍콩에 본사를 둔 VTech는 Z80을 [67][68]기반으로 한 '레이저'라고 불리는 소형 노트북 컴퓨터를 생산했다.마지막 2대는 레이저 PC5와[69] PC6입니다.[70]1999년에 처음 출시된 Cidco MailStation Mivo 100은 Z80 기반의 마이크로컨트롤러를 [71]갖춘 독립형 휴대용 이메일 장치입니다.Texas Instruments는 Z80 코어를 중심으로 구축된 도시바 프로세서를 사용하여 포켓 오가나이저 라인(2000년에 종료)을 생산했습니다.첫 번째 제품은 TI PS-6200으로[72], 수십 개의 모델을 장기간 생산한 후 Pocket Mate [73]시리즈로 완성되었습니다.

임베디드 시스템 및 가전제품

Zilog Z80은 임베디드 시스템과 마이크로컨트롤러 [23]코어에서 오랫동안 인기 있는 마이크로프로세서였으며,[3][74] 오늘날에도 널리 사용되고 있습니다.Z80에는 가전제품, 공업제품 및 전자악기 사용이 포함됩니다.예를 들어 Z80은 획기적인 음악 신시사이저 Project-5와 [75]MIDI 신시사이저 Project [76]600에 사용되었습니다.Casio는 Z80A를 PV-1000 비디오 게임기에 사용했습니다.

아케이드 게임 팩맨을 포함한 1980년대 초반의 아케이드 비디오 게임에는 Z80 CPU가 다수 포함되어 있습니다.

Z80은 세가 마스터 시스템과 세가 게임 기어 콘솔에 사용되었습니다.Sega Genesis에는 Z80이 탑재되어 있으며, 8KB의 RAM이 탑재되어 MC68000 메인 CPU와 병렬로 동작하며, 시스템의 사운드 칩과 I/O(컨트롤러) 포트에 직접 액세스 할 수 있습니다.또, 68000 메인 메모리 버스(64KB 메인 RAM, 소프트웨어 카트리지, 및 비디오 카트리지 전체에 있는 소프트웨어)에 액세스 할 수 있습니다.마스터 시스템 게임과의 하위 호환성을 제공하는 것과 관련하여 Z80은 Genesis 소프트웨어의 [xiii]오디오 제어 및 재생에 자주 사용됩니다.

Z80 CPU는 TI-81부터 1990년부터 Texas Instruments의 트레일블레이징 및 인기 있는 그래프 계산기 TI-8x 시리즈에도 사용되었습니다.TI-81은 2MHz로 클럭이 설정되어 있습니다.TI-82 및 TI-85를 시작으로 하는 시리즈의 대부분의 상위 라인 계산기는 Z80 CPU를 6MHz 이상으로 클럭합니다(TI-8x 이름을 가진 일부 모델은 M68000 등 다른 CPU를 사용하지만 대부분은 Z80 기반입니다).이 경우 조립 또는 컴파일된 사용자 프로그램을 Z80 기계어 코드 형태로 실행할 수 있습니다.)2004년에 도입된 TI-84 Plus 시리즈는 2020년 현재도 생산되고 있다.2015년에 출시된 TI-84 Plus CE 시리즈는 Z80에서 파생된 Zilog eZ80 프로세서를 사용하며 2020년 현재도 생산 중입니다.

1980년대 후반, 「AON」이라고 불리는 일련의 소련의 유선 전화는, Z80을 탑재했습니다.이러한 전화들은 발신자 ID, 발신자에 근거한 다른 벨소리,[77] 단축 다이얼등을 가지는 유선 전화의 기능 세트를 확장했습니다.90년대 후반, 이러한 전화기의 제조원은 전력 소비량을 줄이고 콤팩트 벽면의 과열을 방지하기 위해 8051 호환 MCU로 전환했습니다.

「 」를 참조해 주세요.

- Zilog eZ80

- S-100 버스

- SymbOS

- Z88DK

- Micro-Professor MPF-I, Z80 트레이닝 시스템

각주

- ^ Federico Faggin과의 Oral History에 따르면 National은 CMOS에서만 NMOS 버전을 만들지 않았습니다.

- ^ Zilog는 이 복사를 지연시키기 위해 칩 레이아웃에 몇 가지 "트랩"을 포함시켰습니다.Faggin에 따르면, NEC 엔지니어는 나중에 μPD780을 작동시키기 전에 몇 달 동안 작업했다고 말했습니다.

- ^ 이것들은 Z80 CTC(카운터/타이머), Z80 DMA(다이렉트 메모리 액세스), Z80 DART(듀얼 비동기 리시버-송신기), Z80 SIO(동기 통신 컨트롤러), Z80 PIO(병렬 입력/출력)라고 불립니다.

- ^ Zilog는 Z80과 다른 대부분의 제품을 수년간 제조하다가 제조 공장을 매각하여 오늘날과 같은 "무난한" 회사가 되었습니다.

- ^ 8080에는 16비트 추가 및 16비트 증감 명령이 있었지만 명시적인 16비트 감산 및 오버플로 플래그는 없었습니다.Z80은 이를 ADC HL,rr 및 SBC HL로 보완하고 이에 따라 새로운 오버플로 플래그를 설정합니다(8080 호환 ADD HL에서는 그렇지 않습니다).

- ^ 특히 Sinclair 홈컴퓨터에서 사용되는 40비트 부동소수점 형식의 2개의 오퍼랜드의 32비트 맨티사를 동시에 처리할 수 있습니다.스웨덴 ABC 80이나 ABC 800과 같은 Z80 기반 컴퓨터에서도 비슷한 방식으로 사용되었습니다.

- ^ 이 새로 고침은 데이터를 전송할 필요가 없으며 연속된 행 주소만 출력하므로 1.5T 미만의 상태를 차지합니다.Z80의 전용 M1 신호(기계 사이클 1)를 사용하면 메모리 칩이 명령 페치에 대해 데이터 액세스와 동일한 액세스 시간, 즉 4T 페치 사이클 중 거의 2개의 T-상태(3T 데이터 읽기 사이클)를 사용할 수 있습니다.Z80은 8080(또는 8086)과 같은 클럭 주파수로 액세스 시간의 범위를 가지는 메모리를 사용할 수 있습니다.이 긴 M1 신호(클럭에 상대적인)는 Z80이 동일한 유형의 메모리를 사용하여 6800, 6502 또는 유사한 내부 주파수의 약 4-5배를 사용할 수 있음을 의미하기도 합니다.

- ^ 다이내믹 래치를 사용하여 수천 클럭사이클 이상 정지할 수 없었던 원래 nMOS 버전과는 다릅니다.

- ^ 관련된 8086 패밀리는 이 레지스터 설계도 계승했습니다.

- ^ 이 가변 HL 포인터는 실제로 Datapoint 2200 및 Intel 8008의 메모리(데이터용)에 액세스하는 유일한 방법이었습니다.데이터에 액세스하는 데 직접 주소를 사용할 수 없습니다.

- ^ 점프(

JP프로그램 카운터에 새로운 명령 주소를 로드하는 명령 자체는 메모리에 액세스하지 않습니다.절대 점프와 상대 점프 형식은 오퍼랜드에서 둥근 괄호를 생략하여 이를 반영한다."와 같은 점프 지침을 등록합니다.JP (HL)"는 이 [28]표기법에서 명백히 벗어난 부분에 둥근 괄호를 포함합니다. - ^ 예를 들어, 8080에서 프로그래머는 바이트의 패리티를 다음과 같이 테스트할 수 있습니다.

ADD영점 없음, bySUB그것으로부터, 또는 그것으로부터 제로를 추적하는OR또는XOR8080과 Z80 모두에서 동일한 속도와 크기의 단일 명령 작업입니다.프로그래머가 우연히 패리티를 테스트하는 방법을 선택한 경우OR또는XORZ80은 프로그램을 올바르게 실행하지만 프로그래머가 패리티를 테스트하는 것을 선택한 경우ADD또는SUB(8080 또는 8085와 같이) 바이트의 패리티를 올바르게 나타내도록 P를 할당하는 대신 Z80은 항상 P/V 플래그를 0으로 리셋합니다.인텔의 8080용 프로그래밍 매뉴얼이나 기타 문서에는 패리티 테스트에 산술 명령어를 사용하는 것을 권장하거나 논리 명령어를 사용하는 것이 권장되지 않습니다.따라서 8080 프로그래머가 권장되는 양호한 프로그래밍 프랙티스를 실행하는 것이 Z8080에서 동작하는 방법 중 하나를 선택했다고 기대할 이유가 없습니다.효과가 없는 방법들 중 하나 때문에. - ^ 이러한 일반적인 사용방법은 Genesis에서 Z80을 "사운드 프로세서"라고 부르는 경우가 빈번하지만 부정확한 경우가 많습니다.

레퍼런스

- ^ a b c Zilog (2005). Z80 Family CPU User Manual (PDF). Zilog. p. 5.

- ^ a b 페데리코 파긴, 구술사.

- ^ a b c Balch, Mark (2003-06-18). "Digital Fundamentals". Complete Digital Design: A Comprehensive Guide to Digital Electronics and Computer System Architecture. Professional Engineering. New York, New York: McGraw-Hill Professional. p. 122. ISBN 0-07-140927-0.

- ^ a b The Seybold report on professional computing. Seybold Publications. 1983.

In the 8-bit world, the two most popular microcomputers are the Z80 and 6502 computer chips.

- ^ Anderson(1994), 페이지 51. 오류::

- ^ Anderson(1994), 페이지 57. 오류::

- ^ a b Brock, Gerald W. (2003). The second information revolution. Harvard University Press. ISBN 978-0-674-01178-6.

- ^ "History of the 8-bit: travelling far in a short time". InfoWorld. Vol. 4, no. 47. Palo Alto, CA: Popular Computing Inc. 1982-11-29. pp. 58–60. ISSN 0199-6649.

- ^ Shima, Masatoshi; Federico Faggin; Ralph Ungermann (1976-08-19). "Z-80 chip set heralds third microprocessor generation". Electronics. New York. 49 (17): 32–33 McGraw–Hill.

- ^ Ciarcia(1981), 페이지 31, 32.

- ^ a b Wai-Kai Chen (2002). The circuits and filters handbook. CRC Press. p. 1943. ISBN 978-0-8493-0912-0.

interrupt processing commences according to the interrupt method stipulated by the IM i, i=0, 1, or 2, instruction. If i=1, for direct method, the PC is loaded with 0038H. If i=0, for vectored method, the interrupting device has the opportunity to place the op-code for one byte . If i=2, for indirect vector method, the interrupting device must then place a byte. The Z80 then uses this byte where one of 128 interrupt vectors can be selected by the byte.

- ^ Mathur (1989). Introduction to Microprocessors. p. 111. ISBN 978-0-07-460222-5.

The register architecture of the Z80 is more innovative than that of the 8085

- ^ "Z80 Special Reset".

- ^ Adrian, Andre. "Z80, the 8-bit Number Cruncher".

- ^ "Z80, the 8-bit Number Cruncher".

- ^ Popular Computing. McGraw-Hill. 1983. p. 15.

- ^ Markoff, John (1982-10-18). "Zilog's speedy Z80 soups up 8-bit to 16-bit performance". InfoWorld. InfoWorld Media Group. p. 1. ISSN 0199-6649.

- ^ Electronic design. Hayden. 1988. p. 142.

In addition to supporting the entire Z80 instruction set, the Z180

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

The designers picked an architecture compatible with the Z80, giving Z80 users a completely software compatible upgrade path. The 64180 processor runs every Z80 instruction exactly as a Z80 does

- ^ "Down to the silicon: how the Z80's registers are implemented".

- ^ Kilobaud. 1001001. 1977. p. 22.

- ^ Zaks, Rodnay (1982). Programming the Z80 (3rd ed.). SYBEX. p. 62. ISBN 978-0-89588-069-7.

- ^ a b Steve Heath. (2003). Embedded systems design. Oxford: Newnes. p. 21. ISBN 978-0-7506-5546-0.

- ^ "Z80 Flag Affection". z80.info. Thomas Scherrer. Retrieved 2016-06-14.

- ^ Shirriff, Ken. "The Z-80 has a 4-bit ALU. Here's how it works". Archived from the original on 2013-09-09. Retrieved 2021-11-16.

- ^ Frank Durda IV. "8080/Z80 Instruction Set". Archived from the original on 2016-02-11. Retrieved 2009-07-22.

- ^ "8080A/ 8-Bit N-Channel Microprocessor". Intel Component Data Catalog 1978. Santa Clara, CA: Intel Corporation. 1978. pp. 11–17.

All mnemonics copyright Intel Corporation 1977

- ^ "Z80 Relocating Macro Assembler User's Guide" (PDF). p. B–2. Archived from the original (PDF) on 2011-07-20. Retrieved 2009-06-04.

- ^ Scanlon, Leo J. (1988). 8086/8088/80286 assembly language. Brady Books. p. 12. ISBN 978-0-13-246919-7.

[...] The 8086 is software-compatible with the 8080 at the assembly-language level. [...]

- ^ Nelson, Ross P. (January 1989) [1988]. The 80386 Book: Assembly Language Programmer's Guide for the 80386. Microsoft Programming Series (1 ed.). Microsoft Press. p. 2. ISBN 978-1-55615-138-5.

[...] An Intel translator program could convert 8080 assembler programs into 8086 assembler programs [...]

- ^ a b "Z80 CPU Introduction". Zilog. 1995.

It has a language of 252 root instructions and with the reserved 4 bytes as prefixes, accesses an additional 308 instructions.

- ^ "Z80-CPU Technical Manual, Section 5.0, page 19". Zilog, Inc. Retrieved 2021-07-20.

- ^ Sanchez, Julio; Canton, Maria P. (2008). Software Solutions for Engineers And Scientists. Taylor & Francis. p. 65. ISBN 978-1-4200-4302-0.

The 8-bit microprocessors that preceded the 80x86 family (such as the Intel 8080, the Zilog Z80, and the Motorola) did not include multiplication.

- ^ "8080/Z80 Instruction Sets". Quick and Dirty 8080 Assembler. Frank Durda. Archived from the original on 2016-02-11. Retrieved 2016-07-25.

- ^ Froehlich, Robert A. (1984). The free software catalog and directory. Crown Publishers. p. 133. ISBN 978-0-517-55448-7.

Undocumented Z80 codes allow 8 bit operations with IX and IY registers.

- ^ a b Bot, Jacco J. T. "Z80 Undocumented Instructions". Home of the Z80 CPU.

If an opcode works with the registers HL, H or L then if that opcode is preceded by #DD (or #FD) it works on IX, IXH or IXL (or IY, IYH, IYL), with some exceptions. The exceptions are instructions like LD H,IXH and LD L,IYH.

- ^ Robin Nixon 암스트래드 메모장 고급 사용자 가이드, Robin Nixon, 1993년 ISBN 1-85058-515-6, 219-223페이지

- ^ a b Young, Sean (1998). "Z80 Undocumented Features (in software behaviour)".

The I/O instructions use the whole of the address bus, not just the lower 8 bits. So in fact, you can have 65536 I/O ports in a Z80 system (the Spectrum uses this). IN r,(C), OUT (C),r and all the I/O block instructions put the whole of BC on the address bus. IN A,(n) and OUT (n),A put A*256+n on the address bus.

- ^ Zilog (2005). Z80 Family CPU User Manual (PDF). Zilog. p. 11.

- ^ Ciarcia(1981), 페이지 65.

- ^ Zaks, Rodnay (1989). Programming the Z80. Sybex. p. 200. ISBN 978-0-89588-069-7.

ADD A, n Add accumulator with immediate data n. MEMORY Timing: 2 M cycles; 7 T states.

- ^ Ciarcia(1981), 페이지 63.

- ^ Ciarcia(1981), 페이지 77.

- ^ Ciarcia(1981), 페이지 36.

- ^ Ciarcia(1981), 페이지 58.

- ^ "Z80 User Manual, Special Registers pg. 3". zilog.com. Zilog. Retrieved 2016-06-14.

- ^ "Z80 Family CPU Peripherals User Manual" (PDF). EEWORLD Datasheet. ZiLOG. 2001. Archived from the original (PDF) on 2014-05-02. Retrieved 2014-04-30.

- ^ "Overview of the SHARP MZ-series". SharpMZ.org. Archived from the original on 2008-03-27. Retrieved 2011-07-28.

Most MZ's use the 8bit CPU LH0080 / Z80 [...]

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

The 64180 is a Hitachi-supplied Z80 core with numerous on-chip "extras". Zilog's version is the Z180, which is essentially the same part.

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

Both Toshiba and Zilog sell the 84013 and 84015, which are Z80 cores with conventional Z80 peripherals integrated on-board.

- ^ "EZ80 ACCLAIM Product Family". Zilog.

- ^ Electronic Business Asia. Cahners Asia Limited. 1997. p. 5.

Kawasaki's KL5C80A12, KL5C80A16 and KL5C8400 are high speed 8-bit MCUs and CPU. Their CPU code, KC80 is compatible with Zilog's Z80 at binary level. KC80 executes instructions about four times faster than Z80 at the same clock rate

- ^ "Hardware specs". S1mp3.org. 2005.

- ^ "Projects :: OpenCores".

- ^ "NSC800 - 저전력 고성능 마이크로프로세서 패밀리"

- ^ "TST-4043: HF-모뎀과 FEC를 갖춘 데이터 암호화기"

- ^ "NSC800 고성능 저전력 CMOS 마이크로프로세서"

- ^ "MCS-85, Zilog Z80 및 전국 NSC800 확장 보드"

- ^ "Section 6 MOS MPU, MCU, and Peripherals Market Trends" (PDF). p. 16.

- ^ Axelson, Jan (2003). Embedded ethernet and internet complete. Lakeview research. p. 93. ISBN 978-1-931448-00-0.

Rabbit Semiconductor's Rabbit 3000 microprocessor, which is a much improved and enhanced derivative of ZiLOG, Inc.'s venerable Z80 microprocessor.

- ^ Hyder, Kamal; Perrin, Bob (2004). Embedded systems design using the Rabbit 3000 microprocessor. Newnes. p. 32. ISBN 978-0-7506-7872-8.

The Rabbit parts are based closely on the Zilog Z180 architecture, although they are not binary compatible with the Zilog parts.

- ^ Cruz, Eduardo (2014-11-23). "Arcade Hacker: Capcom Kabuki CPU - Intro".

- ^ Holtz, Herman (1985). Computer work stations. Chapman and Hall. p. 223. ISBN 978-0-412-00491-9.

and CP/M continued to dominate the 8-bit world of microcomputers.

- ^ Dvorak, John C. (1982-05-10). "After CP/M, object oriented operating systems may lead the field". InfoWorld. Vol. 4, no. 18. InfoWorld Media Group. p. 20. ISSN 0199-6649.

The idea of a generic operating system is still in its infancy. In many ways it begins with CP/M and the mishmash of early 8080 and Z80 computers.

- ^ "Otrona Attache". Steve's Old Computer Museum. Steven Stengel. Retrieved 2019-03-05.

- ^ "Sharp PC-1500 Technical Reference Manual" (PDF).

- ^ "Poor Man's Laptop". Google Books. Popular Mechanics, April 1991, page 120. April 1991. Retrieved 2018-04-11.

- ^ "Laser PC4". Old Computer Museum. Retrieved 2018-04-11.

- ^ "Laser PC5 from VTech". Larwe dot com. Retrieved 2018-04-11.

- ^ "Laser PC6". Perfect Solutions dot com. Perfect Solutions. Archived from the original on 2018-05-21. Retrieved 2018-04-11.

- ^ "Fybertech.net - Mailstation". Retrieved 2021-04-18.

- ^ "Texas Instruments PS-6200". Datamath Calculator Museum. Joerg Woerner. Retrieved 2019-06-18.

- ^ "Texas Instruments PocketMate 100". Datamath Calculator Museum. Joerg Woerner. Retrieved 2019-06-18.

- ^ Ian R. Sinclair (2000). Practical electronics handbook. Oxford, Angleterre: Newnes. p. 204. ISBN 978-0-7506-4585-0.

- ^ "Gordon Reid's Vintage Synths - the Sequential Circuits Prophet 5 and Prophet 10". gordonreid.co.uk.

- ^ "Prophet 600: A Classic Synthesizer Gets Processor Upgrade". 2014-03-19.

- ^ "Making a demo for an old phone — AONDEMO". habr.com.

원천

- Ciarcia, Steve (1981). Build Your Own Z80 Computer - Design Guidelines and Application Notes (1st ed.). Byte Books. ISBN 978-0070109629.

추가 정보

- 데이터시트 및 매뉴얼

- Z80 데이터 시트(NMOS), Zilog, 10페이지, 1978.

- Z80 데이터북(NMOS), Zilog, 131페이지, 1978.

- Z80 데이터 시트(NMOS 및 CMOS), Zilog, 36페이지, 2002.에라타

- Z80 사용자 매뉴얼(NMOS 및 CMOS), Zilog, 332페이지, 2016.

- Z80 주변기기 사용자 매뉴얼(NMOS 및 CMOS), Zilog, 330페이지, 2001.

- 하드웨어 서적

- 독자적인 Z80 컴퓨터 구축 - 설계 가이드라인과 어플리케이션 노트, 제1판, Steve Ciarcia, 바이트북, 332페이지, 1981년, ISBN 978-0070109629.(표준)

- Z80 마이크로프로세서 - 아키텍처, 인터페이스, 프로그래밍 및 설계, 제1판, Ramesh Gaonkar, Macmillan, 674페이지, 1988년, ISBN 978-0675205405 (아카이브)

- Z80 사용자 매뉴얼 - 핀 정의, 제어 신호, 주변기기 등, 제1판, Joseph Carr, Reston, 338 페이지, 1980년, ISBN 978-0835995177 (아카이브)

- 마이크로프로세서 인터페이스 기술; 제3판, Rodnay Zaks 및 Austin Lesa; Sybex; 466페이지; 1979; ISBN 978-0-89588-029-1. (아카이브)

- 소프트웨어 북

- Z80 프로그래밍, 3rd Ed, Rodnay Zaks, Sybex, 630페이지, 1980, ISBN 978-0895880949(표준)

- Z80 어셈블리 언어 프로그래밍, 제1판, Lance Leventhal, Osborne/McGraw-Hill, 642페이지, 1979년, ISBN 978-0931988219. (아카이브)

- 8080/Z80 어셈블리 언어 - 개선된 프로그래밍 기술, 제1판, Alan Miller, John Wiley & Sons, 332페이지, 1981년, ISBN 978-0471081241. (아카이브)

- Z80 및 8080 어셈블리 언어 프로그래밍, 제1판, Kathe Spracklen, Hayden, 180페이지, 1979, ISBN 978-0810451674. (아카이브)

- 실용적인 마이크로컴퓨터 프로그래밍 - Z80 - 상주 어셈블러 및 디버깅 모니터, 제1판 Ed, Walter Weller, Northern Technology, 501페이지, 1978년, ISBN 978-0930594053을 포함합니다.(표준)

- Z80 어셈블리 언어 서브루틴, 제1판, Lance Leventhal 및 Winthrop Saville, Osborne/McGraw-Hill, 512페이지, 1983년, ISBN 978-0931988912. (아카이브)

- 문서화되어 있지 않다Z80 문서, Sean Young, v0.91, 52페이지, 2005년 (아카이브)

- 레퍼런스 카드

- Z80 마이크로프로세서용 레퍼런스 카드, Shirley & Nanos; Nanos Systems; 16페이지; 1981년 (아카이브)

- Z80 마이크로프로세서 인스턴트 레퍼런스 카드, James Lewis, Micro Logic, 2페이지, 1981년 (아카이브)