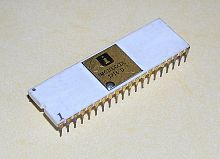

인터실 6100

Intersil 6100Intersil 6100은 12비트 PDP-8 명령어 세트의 싱글칩 마이크로프로세서 구현으로 1970년대 중반 Intersil에 의해 개발된 다양한 주변기기 지원 및 메모리 IC와 함께 구현됩니다.CMOS-PDP8이라고 불리기도 합니다.또한 Harris Corporation에서 생산되었기 때문에 Harris HM-6100으로도 알려져 있습니다.Intersil 6100은 1975년 [1][2]2분기에, Harris 버전은 1976년에 [2]출시되었습니다.

6100 패밀리는 대부분의 동시대 제품(Z80, 8080, 6502, 6800, 9900 등)에서 사용되는 바이폴라 및 NMOS 기술이 아닌 CMOS를 사용하여 생산되었습니다.CMOS 테크놀로지와 낮은 클럭 속도(Harris HM-6100A의 경우 8MHz)로 전력 소비량이 비교적 낮고 10V/2MHz에서 100mW 미만이었으며 4~11V의 광범위한 범위에서 단일 전원으로 작동할 수 있었기 때문에 임베디드 시스템의 높은 신뢰성 없이도 사용할 수 있었습니다.t(시스템의 나머지 부분도 CMOS인 경우).

6100은 군사 사양에 따라 제공되었으며, Intersil과 Harris가 이중으로 공급했기 때문에 일부 군사 제품에서 8080, 6800 등의 저전력 대안으로 사용되었습니다.매우 단순한 명령어 세트와 아키텍처를 가지고 있었지만, 이전에는 이산 논리 회로와 심지어 Ledex 전동식 로터리 스위치나 릴레이 기반 로직 컨트롤러를 사용한 임베디드 시스템에 매우 적합했습니다.

6100 패밀리는 DECmate 제품 라인 등 다수의 상업용 제품에 사용되었으며, DEC는 PC를 최초로 생산하기 위해 시도했다.인터실은 1982년까지 IM6100 패밀리로 상업적으로 집적회로를 판매했습니다.경쟁력 있는 가격이 아니었기 때문에 제공은 실패했습니다.1981년 IBM PC는 "CMOS-8s"의 운명을 굳건히 했습니다.

묘사

6100은 PDP-8을 밀접하게 에뮬레이트하는12비트 CPU입니다(자세한 내용은 PDP-8을 참조).여기에는 PC(프로그램 카운터), 12비트 AC(어큐뮬레이터), MQ(승수 지수)의 3가지 주요 레지스터가 있습니다.2연산 명령어는 모두 AC와 MQ를 읽고 AC에 씁니다.

스택 포인터는 없습니다.서브루틴은 보통 서브루틴 자체의 첫 번째 워드에 리턴 주소를 저장함으로써 메인코드로 돌아가 발신자에게 돌아갑니다.이것에 의해, ROM 에 서브 루틴을 보유하는 것이 어려워지기 때문에, 이러한 서브 루틴은 주소를 격납하는 다른 장소를 찾을 필요가 있습니다.이것은 모든 메인 메모리가 읽기/쓰기 코어였던 원래의 PDP-8에서는 문제가 되지 않았습니다.

6100 조건에서는 다음 명령만 건너뛸 수 있습니다.분기는 조건부 점프와 후속 점프로 구성된다.마스크 가능한 인터럽트는 1개뿐입니다.인터럽트가 트립되면 CPU는 현재 PC를 0000에 저장한 후 0001부터 실행을 시작합니다.인터럽트는 IOF 및 ION(또는 SKON) 명령을 사용하여 비활성화 또는 활성화할 수 있습니다.

6100에는 12비트 데이터/주소 버스가 탑재되어 있어 RAM은 4K워드(6KB)로 제한됩니다.메모리 참조는 7비트로 주소 0 또는 PC 페이지 베이스 주소에서 오프셋됩니다(PC의 최하위7비트를 0으로 설정함으로써 취득).옵션의 6102 지원 칩을 사용하면 메모리를 확장할 수 있습니다.이 칩은 PDP-8/E가 PDP-8을 확장한 것과 마찬가지로 3개의 주소 라인을 추가하여 메모리를 32K 워드(48KB)까지 확장합니다.6102에는 IFR(명령 필드 레지스터)와 DFR(데이터 필드 레지스터)의 2개의 내부 레지스터가 있어 CPU가 메모리에 액세스 할 때 4K 페이지를 오프셋합니다.

버전 및 지원 하드웨어

인터실은 6100 시스템을 지원하기 위해 다양한 관련[3] 칩을 제공했습니다.IM6100 CPU는 스트레이트8(메모리 매핑하드웨어가 없는 기본 PDP-8)을 실장하고 있습니다.IM6101 PIE(Programmable Interface Element)는 기본적인 PDP-8 I/O 포트입니다.IM6102 MEDIC(Memory Extension, DMA Controller, Interval Timer)는 IM6100을 PDP-8/E의 CPU와 유사한 것으로 변환합니다.IM6103 PIO(Parallel Input-Output Port) 및 IM6402 또는 IM6403 UART는 IC 상의 기본적인 PDP-8 I/O 디바이스입니다.

인터실은 또한 호환되는 크기의 RAM과 ROM을 제공했습니다: IM6551과 IM6561 (1 Kbit, 256×4) SRAM, IM6512 (768 비트, 64x12) SRAM, IM6312 (12 Kbit, 1024×12) 마스크 프로그램 가능한 PROM.

이러한 컴포넌트 중 일부는 IM6100 CPU, IM6101 PIE, IM6312 ODT(Octal Debugging Technic) 모니터 ROM, 256×4 RAMOS를 포함한 싱글보드 시스템인 6960 – 썬플라 PC 보드를 탑재한 Intersil 6801 CMOS 패밀리 썬플라 키트로 제공되었습니다.

기본 6100은 나중에 6102 메모리 컨트롤러가 내장된 6120으로 업그레이드되었습니다.

레퍼런스

- ^ "The Explosion 1975-1976 » AntiqueTech". AntiqueTech.com. 2009-04-21. Archived from the original on 2017-07-03. Retrieved 2017-06-19.

- ^ a b Bell, Gordon (1980), Family Tree of Digital's Computers, (Poster), Digital Equipment Corporation, retrieved 2017-06-19

- ^ 인터실, 데이터북 1981, 8-77페이지부터 8-211페이지까지.

외부 링크

- "Intersil 6100 마이크로프로세서 아키텍처", CPU World

- Intersil, "IM6100 CMOS 패밀리 샘플러"