인텔 8051

Intel 8051 인텔 P8051 마이크로컨트롤러 |

인텔 MCS-51 (일반적으로 8051, 보통 8-o-5-1로 발음)는 임베디드 시스템용으로 인텔이 1980년에 개발한 싱글 칩 마이크로 컨트롤러 (MCU) 시리즈입니다.인텔 MCS-51 명령어세트의 설계자는 John H였습니다. 와튼.[1][2]인텔의 오리지널 버전은 1980년대와 1990년대 초에 인기를 끌었으며, 강화된 바이너리 호환 파생 모델이 오늘날에도 여전히 인기를 끌고 있습니다.이것은 복잡한 명령어 세트 컴퓨터의 한 예이며(대형 레지스터 세트 및 레지스터 창과 같은 RISC 아키텍처의 일부 기능을 포함) 프로그램 명령어와 데이터를 위한 별도의 메모리 공간이 있습니다.

인텔의 오리지널 MCS-51 패밀리는 전작 인텔 MCS-48과 마찬가지로 NMOS(Metal-Oxide-Semiconductor) 테크놀로지를 사용하여 개발되었지만 이후 버전(예를 들어 80C51)은 상호보완적인 금속산화물반도체(CMOS) 테크놀로지를 사용하여 전작보다 적은 전력을 소비합니다.따라서 배터리 구동 장치에 더 적합하게 되었습니다.

이 패밀리는 확장 8비트 MCS-151 및 8/16비트/32비트 MCS-251 패밀리 바이너리 호환 마이크로 컨트롤러로 [3]1996년에 계속되었습니다.인텔은 MCS-51, MCS-151 및 MCS-251 패밀리를 제조하고 있지 않지만, 많은 벤더가 제조한 확장 바이너리 호환 파생상품은 여전히 인기가 있습니다.일부 파생 모델에는 Digital Signal Processor(DSP; 디지털 신호 프로세서)가 통합되어 있습니다.이러한 물리 디바이스 외에, 복수의 기업에서는, Field-Programmable Gate Array(FPGA) 또는 Application-Specific Integrated Circuit(ASIC; 애플리케이션 고유의 집적 회로) 설계에 사용하는 IP 코어로 MCS-51 파생 모델을 제공하고 있습니다.

중요한 기능과 응용 프로그램

8051 아키텍처는 많은 기능(중앙처리장치(CPU), 랜덤 액세스 메모리(RAM), 읽기 전용 메모리(ROM), 입출력(I/O) 포트, 시리얼 포트, 인터럽트 제어, 타이머)을 하나의 패키지로 제공합니다.

- 8비트 연산 로직 유닛(ALU) 및 어큐뮬레이터, 8비트 레지스터(특별 이동 명령이 있는 16비트 레지스터 1개), 8비트 데이터 버스 및 2×16비트 주소 버스, 프로그램 카운터, 데이터 포인터 및 관련 8/11/16비트 연산입니다.따라서 주로 8비트 마이크로 컨트롤러입니다.

- 17개의 명령, 1비트 어큐뮬레이터, 32개의 레지스터(4x8비트, 비트 주소 지정 가능) 및 최대 144개의 특수 1비트 주소 지정 가능 RAM 변수(18x8비트)[4]를 갖춘 부울 프로세서

- 명령의 곱셈, 분할 및 비교

- 각각 8개의 레지스터가 있는 4개의 고속 전환 가능 레지스터 뱅크(메모리 맵)

- 옵션 레지스터 뱅크 스위칭을 통한 고속 인터럽트

- 우선순위가[5] 선택 가능한 인터럽트 및 스레드

- 128바이트 또는 256바이트의 온칩 RAM(IRAM)

- 듀얼 16비트 어드레스 버스.Harvard 아키텍처의 2개의 메모리 버스를 사용하여 ROM(PMEM)과 외부 RAM(XRAM) 각각 64KB16(65,536개소)의 메모리 위치에 액세스 할 수 있습니다.

- 온칩 ROM(803x 모델에는 포함되지 않음)

- 8비트 양방향 입출력 포트x 4 (풀 3), 비트 주소 지정 가능

- UART(시리얼 포트)

- 16비트 카운터/타이머×2

- 절전 모드(일부 파생 모델)

8051 코어의 특징 중 하나는 부울 처리 엔진을 포함하는 것으로, 이를 통해 일부 내부 레지스터, 포트 및 일부 RAM 위치에서 비트 레벨 부울 논리 연산을 직접적이고 효율적으로 수행할 수 있습니다.또 다른 기능은 4개의 뱅크 선택 가능한 작업 레지스터 세트를 포함하는 것으로, 인터럽트 서비스 루틴을 시작 및 종료하기 위해 컨텍스트 스위치를 실행하는 데 필요한 시간을 크게 단축합니다.8051은 하나의 명령으로 레지스터 뱅크를 전환할 수 있기 때문에 중요한 레지스터를 RAM으로 전송하는 데 시간이 걸리는 작업을 피할 수 있습니다.

UART 및 필요한 경우 타이머를 구성한 후에는 UART에 의해 마지막 비트가 전환될 때마다 전송 시프트 레지스터를 다시 채우거나 전체 수신 시프트 레지스터를 비우는 간단한 인터럽트 루틴만 작성하면 됩니다(데이터를 다른 곳에 복사).메인 프로그램은 8비트 데이터를 읽고 스택에 쓰는 것만으로 시리얼 읽기 및 쓰기를 수행합니다.

파생 기능

2013년 현재도[update] 많은 주요 칩 메이커에 의해 새로운 파생 모델이 개발되고 있으며 IAR Systems, Keil 및 Altium[6] Tasking과 같은 주요 컴파일러 공급업체가 지속적으로 업데이트를 릴리스하고 있습니다.

MCS-51 기반의 마이크로 컨트롤러에는 일반적으로 1개 또는 2개의 UART, 2개 또는 3개의 타이머, 128 또는 256 바이트의 내부 데이터 RAM(16 바이트는 비트주소 지정 가능), 최대 128 바이트의 I/O, 512 바이트에서 64 KB의 내부 프로그램메모리, 경우에 따라서는 외부 데이터 공간에 있는 확장 데이터 RAM(ERAM)의 양이 포함됩니다.외부 RAM과 ROM은 데이터 및 주소 버스를 공유합니다.원래 8051 코어는 머신 사이클당 12클럭 사이클로 실행되었으며 대부분의 명령어는 1~2개의 머신 사이클로 실행되었습니다.따라서 12MHz 클럭 주파수로 8051은 초당 100만 개의 1사이클 명령 또는 초당 500,000개의 2사이클 명령을 실행할 수 있습니다.확장 8051 코어는 현재 일반적으로 기계 사이클당 6, 4, 2, 또는 1 클럭으로 동작하며 클럭 주파수는 최대 100MHz이므로 초당 더 많은 명령을 실행할 수 있습니다.Silicon Labs, 일부 Dallas(현재는 Maxim Integrated의 일부) 및 일부 Atmel(현재는 Microchip의 일부) 장치는 단일 사이클 [7][8][9]코어를 가지고 있습니다.

8051 변형들 절전 시기 탐지, 온칩 oscillators,self-programmable 플래시 롬 프로그램 메모리 내장된 외부 RAM, 여분의 내부 프로그램 저장, ROM, 사용한 비휘발성 데이터 저장, I2C, 은, 그리고 USB호스트 인터페이스, CAN나 LIN 버스, ZigBee또는 Bluetooth라디오 모듈, PWMgenerato에 부트 스트랩 로더 코드가 내장 리셋 타이머 포함될 수 있다.rs, 아날로그 비교기, 아날로그/디지털 및 디지털/아날로그 변환기, RTC, 추가 카운터 및 타이머, 회로 내 디버깅 설비, 더 많은 인터럽트 소스, 추가 절전 모드, 더 적은 병렬 포트 등인텔은 RAM에 로드된 사용자 프로그램을 실행할 수 있는 BASIC 인터프리터를 ROM에 탑재한 마스크 프로그램 버전 8052AH-BASIC을 제조했습니다.

MCS-51 베이스의 마이크로 컨트롤러는, 극한의 환경에 대응하고 있습니다.고온 변종의 예로는 -40°C~+250°C의[10] Tkmos TK8H51 제품군 또는 -55°C~+225°C의 Honeywell HT83C51(+300°[11]C에서 최대 1년간 작동 가능)이 있습니다.예를 들어 UT69RH051로[12] Cobham(이전의 Aeroflex) 또는 1830VE32로 NIET(러시아어: 1830е3232)[13]에서 사용할 수 있는 방사선 경화형 MCS-51 마이크로컨트롤러를 사용할 수 있습니다.

일부 엔지니어링 스쿨에서는 마이크로 컨트롤러 입문 과정에 [14][15][16][17]8051 마이크로 컨트롤러가 사용됩니다.

패밀리 명명 규칙

8051은 4KB ROM과 128바이트 RAM을 탑재한 인텔의 원래 이름입니다.87로 시작하는 모델에는 사용자가 프로그래밍할 수 있는 EPROM이 있으며 UV 소거가 가능한 경우도 있습니다.세 번째 문자로 C를 사용하는 배리언트는 CMOS의 일종입니다.8031 및 8032는 ROM이 없는 버전으로 128바이트 및 256바이트 RAM을 갖추고 있습니다.마지막 숫자는 메모리 크기를 나타낼 수 있습니다. 예를 들어 8KB ROM의 8052, 16KB EPROM의 87C54 및 32KB EPROM의 87C58 등 모두 256바이트 RAM의 메모리 크기를 나타냅니다.

메모리 아키텍처

MCS-51 에는, 내장 RAM, 특수 기능 레지스터, 프로그램 메모리, 및 외장 데이터 메모리의 4 종류의 메모리가 있습니다.이러한 기능에 효율적으로 액세스하기 위해 일부 컴파일러는[18] 최대 7가지 유형의 메모리 정의를 사용합니다.내부 RAM, 내부 RAM에 대한 싱글비트 액세스, 특수 기능 레지스터, 선택된 (8로 분할 가능) 특수 기능 레지스터에 대한 싱글비트 액세스, 프로그램 RAM, 레지스터 간접 액세스를 사용하여 액세스되는 외부 RAM, 표준 8비트 레지스터 중 하나를 사용하여 액세스되는 레지스터 및 16비트 간접 액세스 레지스터를 이용한 간접 외부 RAM 액세스음.정말.

8051의 명령 세트는 분리된 메모리(데이터와 명령)를 갖춘 하버드 아키텍처로 설계되어 프로그램 메모리에서 가져온 코드만 실행할 수 있으며 프로그램 메모리에 쓰는 명령은 없습니다.그러나 IC를 떠나는 버스는 단일 주소 및 데이터 경로를 가지며, Von Neumann 아키텍처 버스와 매우 유사합니다.

대부분의 8051 시스템은 명령 세트를 준수하며 플래시 메모리와 같은 새로운 실행 가능 프로그램을 다운로드하기 위해 맞춤형 기능이 필요합니다.

내장 RAM

Internal RAM(IRAM; 내부 RAM)에는 주소 0 ~0xFF 를 사용하는8비트 주소 공간이 있습니다.0x00 ~ 0x7F의 IRAM에는 128개의 직접 수신처 지정 1바이트 레지스터가 포함되어 있으며 명령의 일부인 8비트 절대 주소를 사용하여 액세스할 수 있습니다.또는 간접적으로 IRAM에 액세스 할 수 있습니다.주소는 R0 또는 R1에 로드되어 @R0 또는 @R1 구문을 사용하여 메모리에 액세스 하거나 스택포인터 SP를 통해 스택메모리로서 PUSH 및 POP 조작과 *CALL 및 RET 조작을 사용합니다.

원래의 8051에는 128바이트의 IRAM밖에 없습니다.8052에서는 IRAM이 0x80 ~0xFF로 추가되어 간접적으로만 액세스 할 수 있습니다(스택스페이스로서 사용하는 등).대부분의 8051 클론에는 256바이트의 IRAM도 탑재되어 있습니다.

대신 IRAM 주소 80~FF에 대한 직접 액세스는 어큐뮬레이터 A, B, 반송 비트 C 및 제어, 상태 등을 위한 다른 특수 레지스터가 위치한 특수 함수 레지스터(SFR)에 매핑된다.

특수 기능 레지스터

특수기능 레지스터(SFR)는 IRAM과 동일한 주소 공간(주소 0x80 ~ 0xFF)에 있으며 IRAM의 하반부와 동일한 명령을 사용하여 직접 액세스합니다.이러한 주소에는 @R0 또는 @R1 또는 스택포인터 SP를 통해 간접적으로 액세스할 수 없습니다.대신 IRAM의 후반부에 액세스 할 수 있습니다.

특수 기능 레지스터(SFR)에는 축전지 A(또는 ACC, E0에서) 및 B(F0에서) 및 프로그램 상태 워드(또는 D0에서 PSW) 자체와 16비트 데이터 포인터 DPTR(82, DPL 및 83, DPH)가 포함됩니다.이들 외에 A8에서의 인터럽트 인터넷 IE 및 B8에서의 인터럽트 우선 IP, I/O포트 P0(80), P1(90), P2(A0), P3(B0), 시리얼 I/O컨트롤 SCON(98) 및 CPUSBU(99)를 포함한 기타 특수기능 레지스터의 작은 코어.) 및 동작 모드(89의 TMOD), 16비트타이머 0(8A에서의 TL0, 8C에서의 TH0) 및 타이머 1(8B에서의 TL1, 8D에서의 TH1)은 8051의 모든 버전에 있습니다.다른 주소는 버전에 의존하며, 특히 8052의 타이머 2 레지스터는 8051에 포함되어 있지 않다.컨트롤 레지스터 T2CON(C8), 16비트 캡처/래치(CA의 RCAP2L, CB의 RCAP2H) 및 타이머 2(CC의 TL2, CD의 TH2)는 포함되어 있지 않다.

창 등록

0x00~0x1F 의 IRAM 의 32 바이트에는, 8 바이트의 레지스터 윈도우를 4 개 격납하기 위한 스페이스가 포함되어 있습니다.여기에는 8 개의 레지스터 R0 ~ R7 이 매핑됩니다.현재 활성 창은 프로그램 상태 워드에 포함된 2비트 주소에 의해 결정됩니다.

비트 레지스터

IRAM 로케이션 0x20~0x2F 에서의 16바이트(128비트)에는 128개의 1비트레지스터를 위한 공간이 포함되어 있습니다.이들은 비트레지스터 00-7F 로서 개별적으로 주소 지정이 가능합니다.

80-FF로 주소 지정된 나머지 비트 레지스터는 16개의 특수 함수 레지스터 80, 88, 90, 98, ..., F0 및 F8(주소가 8의 배수인 비트)에 매핑되므로 어큐뮬레이터 A, B 및 프로그램 상태 워드 PSW로 구성된 비트가 포함됩니다.PSW의 비트3 및 4인 레지스터 윈도 주소는 각각 비트레지스터 D3 및 D4로 주소 지정이 가능하며 PSW의 비트7의 캐리비트 C(또는 CY)는 비트레지스터 D7로 주소 지정이 가능합니다.

프로그램 메모리

프로그램 메모리(PMEM, IRAM 및 XRAM에 비해 사용 빈도는 낮지만)는 최대 64KB의 읽기 전용 메모리이며, 주소 0부터 다른 주소 공간에 있습니다.사용하는 칩의 특정 모델에 따라 온칩 또는 오프칩이 될 수 있습니다.프로그램 메모리는 읽기 전용이지만 8051의 일부 변종에서는 온칩플래시 메모리를 사용하여 시스템 내 또는 애플리케이션 내 메모리를 재프로그래밍하는 방법을 제공합니다.

코드와 더불어 룩업 테이블과 같은 읽기 전용 데이터를 프로그램 메모리에 저장할 수 있습니다.MOVC A,@A+DPTR또는MOVC A,@A+PC지침들.주소는 8비트 어큐뮬레이터와 16비트 레지스터(PC 또는 DPTR)의 합계로서 계산됩니다.

특수 점프 및 호출 지침(AJMP그리고.ACALL)는 로컬(같은 2KB 이내)[19] 프로그램 메모리에 액세스하는 코드 크기를 약간 줄입니다.

64K보다 큰 코드가 필요한 경우 공통 시스템은 코드를 뱅크 스위칭하여 범용 I/O가 상위 주소 비트를 선택합니다.일부 8051[18] 컴파일러는 페이지 코드에 자동으로 액세스하도록 준비합니다.이러한 시스템에서는 인터럽트 벡터와 페이징 테이블이 코드의 첫 32K에 배치되어 항상 상주합니다.

외부 데이터 메모리

External Data Memory(XRAM; 외부 데이터 메모리)는 주소 0에서 시작하여 16비트의 주소 공간을 사용할 수 있는 세 번째 주소 공간입니다.온칩 또는 오프칩을 사용할 수도 있습니다.외부적인 이유는MOVX(외부 이동) 명령.8051의 많은 변종에는 표준 256바이트의 IRAM과 칩 상의 몇 킬로바이트의 XRAM이 포함되어 있습니다.

XRAM의 첫 번째 256바이트는MOVX A,@R0,MOVX A,@R1,MOVX @R0,A,그리고.MOVX @R1,A지침들.전체 64KB에 액세스하려면MOVX A,@DPTR그리고.MOVX @DPTR,A. 16비트 주소를 사용하려면 프로그래머가 16비트 인덱스 레지스터를 로드해야 합니다.따라서 16비트 주소를 사용하는 RAM 접근은 상당히 느립니다.

CPU에[20] 따라서는 8비트의 간접 주소에서 임의의 8비트의 범용 레지스터를 사용할 수 있습니다.

이 기능을 사용할 수 있도록 내부 RAM이 256바이트보다 크거나 외부[20] RAM에 액세스할 수 없는 일부 8051 호환 마이크로 컨트롤러는 외부 RAM에 액세스할 수 없으며 256바이트 페이지의 상위 주소를 설정할 수 있는 특수 기능 레지스터(PDATA 등)를 가지고 있습니다.이것에 의해, 범용 I/O 핀을 설정해 RAM 주소의 상한 바이트를 호출할 수 있는 MCS8051 모드가 에뮬레이트 됩니다.

64K보다 큰 RAM이 필요한 경우 일반 시스템에서는 RAM을 뱅크 스위칭하여 범용 I/O에서 상위 주소 비트를 선택합니다.일부 8051[18] 컴파일러는 페이지 데이터에 자동으로 액세스하도록 준비합니다.

레지스터

8051에서 메모리 매핑되지 않은 유일한 레지스터는 16비트 프로그램카운터(PC)입니다.실행할 다음 명령의 주소를 지정합니다.Relative Branch Instructions는 PC에 추가되는 8비트 서명 오프셋을 제공합니다.

8개의 범용 레지스터 R0~R7은 다른 레지스터보다 1바이트 짧은 명령으로 액세스할 수 있습니다.0x00 ~ 0x1F 사이의 IRAM에 매핑됩니다.PSW의 2개의 뱅크 셀렉트비트에 의해 판별되는 그 범위의 8바이트만이 항상 사용됩니다.

다음은 특수 기능 레지스터 공간에 메모리 매핑된 8051 레지스터의 일부 목록입니다.

- 스택 포인터, SP(0x81)

- 서브루틴 호출 및 반환 명령에 사용되는8비트 레지스터입니다스택은 위로 올라갑니다.SP는 푸시 전에 증가하며 값을 팝한 후에 감소합니다.

- 데이터 포인터, DP(0x82–83)

- 이는 PMEM 및 XRAM에 액세스하기 위해 사용되는 16비트 레지스터입니다.

- 프로그램 상태 단어, PSW(0xD0)

- 여기에는 비트 번호별로 중요한 상태 플래그가 포함됩니다.

- 패리티, P. 어큐뮬레이터 A의 패리티(비트의 XOR)를 제공합니다.

- 사용자 정의 UD소프트웨어에 의해 읽혀지고 쓸 수 있습니다.하드웨어의 영향을 받지 않습니다.

- 오버플로 플래그, OV추가 시 서명된 오버플로가 발생할 때 설정됩니다.

- 등록 선택 0, RS0.레지스터 뱅크의 하위 비트입니다.0x08 또는 0x18의 뱅크가 사용 중일 때 설정됩니다.

- 등록 1, RS1을 선택합니다.레지스터 뱅크의 상위 비트입니다.0x10 또는 0x18의 뱅크가 사용 중일 때 설정됩니다.

- 플래그 0, F0.소프트웨어에 의해 읽혀지고 쓸 수 있습니다.하드웨어의 영향을 받지 않습니다.

- 보조 캐리어, AC추가 시 비트 3에서 비트 4로의 반송파가 발생할 때 설정됩니다.

- 캐리어 비트 C.종종 비트 계산의 일반 레지스터 또는 "부울 어큐뮬레이터"로 사용됩니다.

- 어큐뮬레이터, A(0xE0)

- 이 레지스터는 대부분의 명령에서 사용됩니다.

- B 레지스터(0xF0)

- 이것은 곱셈 및 분할 명령의 축전지 확장으로 사용됩니다.

256 싱글비트는 직접 주소를 지정할 수 있습니다.이것들은 0x20~0x2F 의 16 개의 IRAM 로케이션이며, 16 개의 특수 함수 레지스터 0x80, 0x88, 0x90, ..., 0xF8 입니다.이러한 바이트 중 임의의 비트는 다양한 논리 연산 및 조건부 분기에서 직접 액세스할 수 있습니다.

PSW에는 공통 네거티브(N) 플래그 또는 제로(Z) 플래그가 포함되어 있지 않습니다.전자의 경우, 어큐뮬레이터의 최상위 비트는 비트 주소 지정 가능 SFR이기 때문에 직접 주소 지정이 가능합니다.후자의 경우 축적이 0인지 아닌지에 대한 명확한 지침이 있습니다.2연산자 비교와 점프 조작도 있다.

패리티(P) 비트는 패리티를 포함한 시리얼모드를 실장하기 위해서 자주 사용됩니다.이를 지원하기 위해 표준 MCS51 UART는 9비트를 전송할 수 있습니다.

마이크로아키텍처

인텔 MCS8051의 마이크로아키텍처는 독자 사양이지만, 공개된[21] 기능에 의해서 동작 방법이 제시되고 있습니다.멀티 사이클 프로세서입니다.MCS8051에서는 대부분의 명령에서 12개의[21] 클럭사이클이 사용되었습니다.많은 명령에서 [21]축전지를 사용합니다.이와는 대조적으로 대부분의 호환 컴퓨터는 곱셈 및 나누기 명령을 제외하고 1~3주기로 명령을 실행합니다.대부분의 어플리케이션에서 MCS8051을 대체하는 주된 이유는 속도가 매우 빠르기 때문입니다.

각 인터럽트에는 [21]4개의 우선순위가 있습니다.각 priority 내에서 디바이스 인터럽트는 고정 [21]priority가 됩니다.

명령 집합

명령어는 모두 1 ~3 바이트 길이로 첫 번째 opcode 바이트와 최대 2 바이트의 오퍼랜드로 구성됩니다.

opcode 바이트의 1µ4(x0 ~x3)는 불규칙한 opcode에 사용됩니다.

opcode 바이트의 3µ4 x4 ~xF는 12개의 오퍼랜드가 있는 16개의 기본 ALU 명령에 할당됩니다.Opcode의 최하위 니블은 다음과 같이 기본 피연산자를 선택합니다.

- x8–xF: 직접 등록, R0–R7.

- x6–x7: 간접, @R0 또는 @R1을 등록합니다.

- x5: 메모리 다이렉트, 다음 바이트는 IRAM 또는 SFR 위치를 지정합니다.

- x4: 즉시 다음 바이트는 8비트 상수를 지정합니다.오퍼랜드가 수신처인 경우(

INC operand,DEC operand또는, 조작에 이미 직접 소스가 포함되어 있는 경우).MOV operand,#data,CJNE operand,#data,offset대신 축전지 사용을 지정합니다.

최상위 니블은 다음과 같이 동작을 지정합니다.모든 것이 모든 주소 지정 모드를 지원하는 것은 아닙니다.특히 프라이머리 오퍼랜드가 기입되었을 때는 즉시 모드를 사용할 수 없습니다.명령 니모닉은 대상, 소스 오퍼랜드 순서를 사용합니다.

- 0y:

INC operand - 지정된 오퍼랜드를 증분합니다.즉시 모드(opcode 0x04)는 어큐뮬레이터를 지정합니다.

INC A. - 1y:

DEC operand - 지정된 오퍼랜드를 감분합니다.즉시 모드(opcode 0x14)는 어큐뮬레이터를 지정합니다.

DEC A. - 2년:

ADD A,operand - 오퍼랜드를 어큐뮬레이터 A에 추가합니다.Opcode 0x23 (

RL A, "좌회전"하지만 실제로는 좌회전)은 다음과 같이 생각할 수 있습니다.ADD A,A. - 3y:

ADDC A,operand - 피연산자와 C 비트를 누적기에 추가합니다.Opcode 0x33 (

RLC A, 캐리 왼쪽 회전)은 다음과 같이 생각할 수 있습니다.ADDC A,A. - 4y:

ORL A,operand - 논리 OR 피연산자를 어큐뮬레이터에 넣습니다.이 동작의 2개의 메모리 수신처 형식,

ORL address,#data그리고.ORL address,A는 opcode 0x43 및 0x42로 지정됩니다. - 5년:

ANL A,operand - 논리 AND 피연산자를 누적기에 넣습니다.이 동작의 2개의 메모리 수신처 형식,

ANL address,#data그리고.ANL address,A는 opcode 0x53 및 0x52로 지정됩니다. - 6년간:

XRL A,operand - Logical exclusive(논리 배타적) 또는 피연산자를 누적기에 넣습니다.이 동작의 2개의 메모리 수신처 형식,

XRL address,#data그리고.XRL address,A는 opcode 0x63 및 0x62로 지정됩니다. - 7y:

MOV operand,#data - 오퍼랜드로 즉시 이동합니다.즉시 모드(opcode 0x74)는 어큐뮬레이터를 지정합니다.

MOV A,#data. - 8년:

MOV address,operand - 값을 IRAM 또는 SFR 레지스터로 이동합니다.즉시 모드(opcode 0x84)는 opcode 0x75와 중복되므로 이 작업에는 사용되지 않습니다.

- 9년:

SUBB A,operand - 누적기에서 피연산자를 뺍니다.이 연산은 차용되며 차용 없이 차감되지 않습니다.

- 예:

MOV operand,address - IRAM 또는 SFR 레지스터에서 값을 이동합니다.immediate 모드(opcode 0xA4)는 사용되지 않습니다.immediate는 소스로만 기능하기 때문입니다.메모리 다이렉트모드(opcode 0xA5)는 0x85와 중복되기 때문에 사용되지 않습니다.

- 기준:

CJNE operand,#data,offset - 피연산자와 즉시 비교

#data동일하지 않은 경우 PC + 오프셋으로 점프합니다.immediate 모드 및 memory direct 모드(opcode 0xB4 및 0xB5)는 오퍼랜드를 어큐뮬레이터와 비교합니다.CJNE A,operand,offset같은 명령일 경우 비교와 점프는 없습니다.CJE. - Cy:

XCH A,operand - 축압기와 피연산자를 교환합니다.즉시 모드(opcode 0xC4)는 이 작업에 사용되지 않습니다.

- Dy:

DJNZ operand,offset - 피연산자를 줄이고 결과가 0이 아닌 경우 PC + 오프셋으로 점프합니다.즉시 모드(opcode 0xD4) 및 레지스터 간접 모드(0xD6, 0xD7)는 사용되지 않습니다.

- 눈:

MOV A,operand - 피연산자를 축전지로 이동합니다.이 조작(opcode 0xE4)에는 opcode 0x74가 중복되기 때문에 즉시 모드는 사용되지 않습니다.

- 회계연도:

MOV operand,A - 누산기를 피연산자로 이동합니다.즉시 모드(opcode 0xF4)는 효과가 없기 때문에 사용되지 않습니다.

그뿐ADD,ADDC,그리고.SUBB명령에서는 PSW 플래그를 설정합니다.그INC,DEC논리적인 지시에는 해당되지 않습니다.그CJNEinstruction은 오퍼랜드1 - 오퍼랜드2에서 얻은 차용에 대해서만 C비트를 변경합니다.

불규칙한 명령어는 64개의 opcode로 구성되어 있으며, 주소 지정 모드가 더 제한적이며, 일반 명령에서는 적용할 수 없는 모드에서 제거되는 여러 opcode가 있습니다.

| 오퍼코드 | x0 | x1 | x2 | x3 | x4 |

|---|---|---|---|---|---|

| 0y | NOP |

| LJMP addr16 | RR A(오른쪽 끝) | INC A |

| 1y | JBC bit,offset(비트가 클리어와 함께 설정되어 있는 경우) | LCALL addr16 | RRC A(캐리 바로 통과) | DEC A | |

| 2년 | JB bit,offset(비트가 설정되어 있는 경우) | RET | RL A(왼쪽 끝) | ADD A,#data | |

| 3년 | JNB bit,offset(비트가 클리어된 경우 표시됨) | RETI | RLC A(좌회전 반송) | ADDC A,#data | |

| 4y | JC offset(캐리 세트인 경우 제외) | ORL address,A | ORL address,#data | ORL A,#data | |

| 5년 | JNC offset(안전하게 운반하는 경우) | ANL address,A | ANL address,#data | ANL A,#data | |

| 6년 | JZ offset(제로인 경우 제외) | XRL address,A | XRL address,#data | XRL A,#data | |

| 7년 | JNZ offset(제로가 아닌 경우 제외) | ORL C,bit | JMP @A+DPTR | MOV A,#data | |

| 8년 | SJMP offset(짧은 점프) | ANL C,bit | MOVC A,@A+PC | DIV AB | |

| 9년 | MOV DPTR,#data16 | MOV bit,C | MOVC A,@A+DPTR | SUBB A,#data | |

| 아아 | ORL C,/bit | MOV C,bit | INC DPTR | MUL AB | |

| 기준 | ANL C,/bit | CPL bit | CPL C | CJNE A,#data,offset | |

| 싸이 | PUSH address | CLR bit | CLR C | SWAP A | |

| Dy | POP address | SETB bit | SETB C | DA A(수직 조정) | |

| 아이 | MOVX A,@DPTR | MOVX A,@R0 | MOVX A,@R1 | CLR A | |

| Fy | MOVX @DPTR,A | MOVX @R0,A | MOVX @R1,A | CPL A |

- 답 5

- 미사용

- B5

CJNE A,address,offset- D6~7

XCHD A,@R0–1오퍼랜드의 하위 니블을 교환합니다.

그SJMP(숏 점프) opcode는 부호 있는 상대 오프셋 바이트 피연산자를 가져와서 다음 명령의 주소에 상대적인 제어를 전송합니다.그AJMP/ACALLopcodes는 opcode 바이트의 최상위 3비트를 다음 바이트와 결합하여 PC 레지스터의 하위 11비트를 교체하는 데 사용되는 11비트 수신처를 지정합니다(PC 레지스터의 상위 5비트는 그대로 유지됩니다).큰 주소의 경우는,LJMP그리고.LCALL명령에서는, 16 비트의 수신처를 사용할 수 있습니다.

8051이 인기를 끄는 이유 중 하나는 싱글비트에서의 동작 범위이다.비트는 항상 절대 주소로 지정됩니다.레지스터 간접 주소나 인덱스 주소 지정은 없습니다.싱글 비트로 동작하는 순서는 다음과 같습니다.

SETB bit,CLR bit,CPL bit: 지정된 비트를 설정, 클리어 또는 보완합니다.JB bit,offset: 비트가 설정되어 있는 경우 점프JNB bit,offset: 조금 클리어되면 점프JBC bit,offset: 비트가 설정되어 있으면 점프하고 비트를 클리어합니다.MOV C,bit,MOV bit,C: 지정된 비트를 반송 비트로 이동하거나 그 반대로 이동합니다.ORL C,bit,ORL C,/bit: 또는 반송 비트에 대한 비트(또는 그 보완)ANL C,bit,ANL C,/bit: 캐리어 비트에 대한 비트(또는 그 보완)

비트 오퍼랜드는 다음 형식으로 작성됩니다.address.number반송 플래그가 비트 주소 지정 가능한 프로그램 상태 워드의 비트7이기 때문에SETB C,CLR C그리고.CPL C명령어는 보다 짧은 등가입니다.SETB PSW.7,CLR PSW.7그리고.CPL PSW.7.

대부분의 명령에서는 하나의 오퍼랜드가 어큐뮬레이터 또는 즉시 상수여야 하지만 opcode 0x85는MOV두 개의 내부 RAM 위치 간에 직접 연결합니다.

프로그래밍

8051에는 다양한 고급 프로그래밍 언어 컴파일러가 있습니다.8051에서는 여러 개의 C 컴파일러를 사용할 수 있습니다.이 컴파일러의 대부분은 프로그래머가 각 변수를 6종류의 메모리에 저장할 위치를 지정하고 멀티 레지스터 뱅크나 비트 조작 명령 등 8051 고유의 하드웨어 기능에 액세스할 수 있도록 합니다.상용 C [22]컴파일러가 많이 있습니다.Small Device C 컴파일러(SDCC)는 널리 사용되는 오픈 소스 C [23]컴파일러입니다.8051에서는 C++, [24][25][26][27]Fourth, BASIC, Object Pascal, PL/M, Modula-2 등의 고급 언어를 사용할 수 있지만 C나 어셈블리에 비해 널리 사용되지[citation needed] 않습니다.

IRAM, XRAM 및 PMEM(읽기 전용)은 모두 주소 0을 가지고 있기 때문에 8051 아키텍처용 C 컴파일러는 컴파일러 고유의 플러그마 또는 기타 확장 기능을 사용하여 특정 데이터의 저장 위치를 나타냅니다(즉, PMEM 내의 상수 또는 IRAM 내의 고속 액세스가 필요한 변수는 3개의 메모리 중 하나의 메커니즘입니다).일반적으로 포인터가 참조하는 메모리를 결정하기 위해 제공되며, 메모리 공간을 포함하도록 포인터 유형을 제한하거나 포인터와 함께 메타데이터를 저장함으로써 제공됩니다.

관련 프로세서

인텔은 2007년 [28][29]3월에 MCS-51 제품군을 단종했습니다.다만, 다른 벤더의 확장판 8051 제품이나 실리콘 지적 재산을 정기적으로 추가하고 있습니다.

8051의 전신인 8048은 최초의 IBM PC의 키보드에 사용되었으며, 여기서 키 입력을 컴퓨터의 본체로 전송되는 시리얼 데이터 스트림으로 변환하였다.인텔 8049는 Sinclair QL에서도 같은 역할을 했습니다.8048 및 파생 모델은 오늘날에도 기본 모델 키보드에 사용되고[update] 있습니다.

8031은 내장 프로그램 메모리(읽기 전용 메모리, ROM)가 없는 오리지널 8051의 축소판입니다.이 칩을 사용하려면 8031이 가져와 실행할 프로그램을 포함하는 외부 ROM을 추가해야 했습니다.8051 칩은 ROM이 없는 8031로 판매될 수 있습니다.8051의 내부 ROM은 8031 기반 설계에서는 EA 핀의 정상적인 상태에 의해 비활성화되기 때문입니다.벤더에서는 8051의 ROM 코드 불량, 8051의 과잉 공급, 8031의 과소 공급 등 다양한 이유로 8031을 판매할 수 있습니다.

8052는 128바이트가 아닌 256바이트의 내부 RAM, 4KB가 아닌 8KB의 ROM 및 세 번째 16비트 타이머를 탑재한 원래 8051의 확장 버전입니다.대부분의 최신 8051 호환 마이크로 컨트롤러에는 이러한 기능이 포함되어 있습니다.

8032는 내장 ROM 프로그램 메모리가 부족하다는 점을 제외하고는 8052와 동일한 기능을 가지고 있었습니다.

8751은 4KB ROM이 아닌 4KB EPROM을 탑재한8051입니다비휘발성 메모리 타입을 제외하고는 동일했습니다.이 부품은 다이 상단에 투명한 석영 창이 있는 세라믹 패키지로 제공되어 EPROM을 지우는 데 UV를 사용할 수 있습니다.관련 부품은 8752는 8KB EPROM, 8754는 16KB EPROM, 8758은 32KB EPROM입니다.

80C537(ROM 없음) 및 80C517(8KB ROM)은 자동차 업계용으로 설계된 CMOS 버전입니다.확장 기능에는 주로 새로운 주변기기 및 확장 주변기기가 포함됩니다.80C5x7에는 페일 세이프 메커니즘, 아날로그 신호 처리 기능, 확장 타이머 기능 및 32비트 산술 페리페럴이 탑재되어 있습니다.기타 기능은 다음과 같습니다.

- 256 바이트 온칩 RAM

- 256비트(직접 주소 지정 가능)

- 최대 64KB까지 확장 가능한 외장 프로그램 및 데이터 메모리

- 멀티플렉스 입력이 12개인 8비트 A/D 컨버터

- 산술 주변기기는 16×16→32비트 곱셈, 32/16→16비트 분할, 32비트 시프트 및 32비트 정규화 연산을 수행할 수 있습니다.

- 프로그램 및 외부 데이터 메모리의 간접 주소 지정을 위한 데이터 포인터 1개가 아닌 8개

- 확장된 감시 설비

- 9개의 I/O 포트

- 2개의 전이중 시리얼 인터페이스(개개의 보레이트 제너레이터 포함)

- 4개의 우선순위 인터럽트 시스템, 14개의 인터럽트 벡터

- 3가지 절전 모드

- Intel MCS-51 세컨드소스

AMD D87C51

OKI M80C31

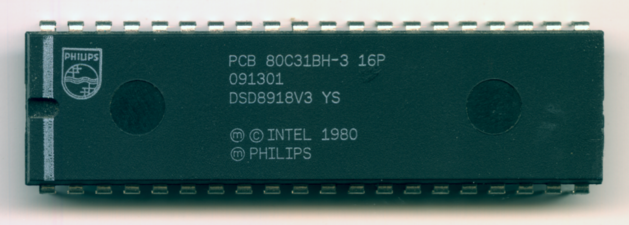

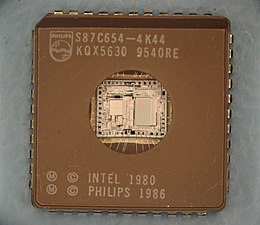

Philips PCB80C31

신호학 SCN8031

파생 벤더

20개 이상의 독립 제조사가 MCS-51 호환 프로세서를 [citation needed]생산하고 있습니다.

MCS-51과 호환되는 다른 IC 또는 IP는 아날로그 장치,[30] Integrential [31]Minsk, Kristall [32]Kiev 및 NIET Voronezh에 [13]의해 개발되었습니다. 키이우

지적 재산으로 사용

오늘날 8051은 여전히 개별 부품으로 사용 가능하지만, 대부분 실리콘 지적 재산권 [33]코어로 사용됩니다.하드웨어 기술 언어 소스 코드(VHDL 또는 Verilog 등) 또는 FPGA 넷리스트 형식으로 제공되는 이러한 코어는 일반적으로 USB 플래시 드라이브, 세탁기, 칩 상의 복잡한 무선 통신 시스템에 이르기까지 임베디드 시스템에 통합되어 있습니다.설계자는 ARM Cortex-M 시리즈, MIPS, BA22 [citation needed]등의 32비트 프로세서에 비해 크기가 작고 소비전력이 낮기 때문에 8051개의 실리콘 IP 코어를 사용합니다.

최신 8051 코어는 이전 패키지 버전보다 빠릅니다.설계 개선으로 8051 퍼포먼스가 향상되어 원래의 MCS 51 명령 세트와의 호환성이 유지됩니다.원래의 인텔 8051은 머신 사이클당 12클럭 사이클로 동작하며 대부분의 명령어는 1회 또는2회 머신 사이클로 실행됩니다.통상 최대 클럭 주파수는 12MHz이므로 이 구형 8051은 초당 100만 개의 단일 사이클 명령 또는 500,000개의 2사이클 명령을 실행할 수 있습니다.반면 확장 8051 실리콘 IP 코어는 머신 사이클당 1회 클럭 사이클로 동작하며 클럭 주파수는 최대 450MHz입니다.즉, 8051 호환 프로세서는 초당 4억 5천만 개의 명령을 실행할 수 있습니다.

8051을 기반으로 한 MCU

이 섹션은 확장해야 합니다.추가해서 도와주시면 됩니다. (2021년 6월) |

- ABOV: MC94F, MC95F, MC96F 시리즈

- Infineon: XC800

- Maxim Integrated(구 댈러스):DS80 시리즈 [34]등

- 멘토 그래픽스: M8051SYNTIL8의[35] 멘토용으로 설계된 EW 등

- 메가윈: 74, 82, 84, 86, 87 및 89 시리즈

- 마이크로칩(구 Atmel):AT89C51, AT89S51, AT83C5134 [9]등

- NXP: NXP700 및 NXP900 시리즈

- Siemens SAB 80532-N

- Siemens SDA 30C164-2 (ROM리스 프로세서)[36]

- 실러지 전기 계측 SoC: 71M6511, 71M6513, 71M6531, 71M6534, 71M6542, 71M6543[37] 에너지 계측 SoC: 78M6631, 78M6618, 78M6613, 78M6612[38]

- 실리콘 랩: C8051 시리즈 및 EFM8 시리즈[7]

- 실리콘 스토리지 테크놀로지:FlashFlex51 MCU(SST89E52RD2, SST89E54)RD2, SST89E58RD2, SST89E516RD2SST89V52RD2, SST89V54RD2, SST89V58RD2, SST89V516RD2)[39]

- STC Micro: STC89C51RC, STC90C51RC, STC90C58AD, STC10F08XE, STC11F60XE, STC12C5410AD, STC12C5202AD, STC12C12C12F5202AD, STC12C

- Texas Instruments CC111x, CC24xx 및 CC25xx 시리즈 RF SoC

- WCH(Nanjing Qinheng Microelectronics):CH551, CH552, CH554, CH546, CH547, CH548, CH558, CH559[41]

Digital Signal Processor(DSP; 디지털 신호 프로세서) 바리안트

최대 6억 7,500만 명령/초(MIPS)[42]의 16비트 DSP(MP3 또는 Vorbis 코딩/디코딩[44])와 통합 USB 2.0 인터페이스를[43] 탑재한 여러 변종 또는 지적 재산권이 있습니다.

확장 8비트 바이너리 대응 마이크로 컨트롤러: MCS-151 패밀리

이 섹션은 확장해야 합니다.추가가 가능합니다. (2013년 5월) |

1996년 인텔은 8051과 호환되는 완전 바이너리 및 명령어 세트를 갖춘 [3]MCS-151 패밀리를 발표했습니다.8051과는 달리 MCS-151은 파이프라인 CPU로 16비트 내부 코드버스가 있으며 속도는 6배입니다.MCS-151 패밀리는 Intel에 의해 단종되었지만 바이너리 호환성과 부분적으로 강화된 변형으로 널리 이용 가능합니다.

8/16/32비트 바이너리 대응 마이크로 컨트롤러: MCS-251 패밀리

이 섹션은 확장해야 합니다.추가가 가능합니다. (2013년 5월) |

16 MB(24 비트)의 주소 공간과 6배의 명령 사이클을 갖춘 80251 8/16/32 비트 마이크로 컨트롤러는 1996년에 [3][45]인텔에 의해 도입되었습니다.8비트 8051, 24비트 리니어 어드레싱, 8비트 ALU, 8비트 명령, 16비트 명령어, 32비트 한정 세트, 16비트 레지스터, 16비트 레지스터(8비트 레지스터와 공간을 공유하지 않는 8비트 레지스터 및 8비트 레지스터, 2비트 레지스터를 포함)로 동작합니다.0 32비트 레지스터(전용 32비트 레지스터 2개 및 32비트 [46]레지스터당 16비트 레지스터 2개를 포함하는 32비트 레지스터 8개)

확장 명령어[47](프로그래머 가이드도[48] 참조)와 고성능의 [49]최신 버전(지적재산권(IP)[50]으로도 이용 가능)을 갖추고 있습니다.3단계 파이프라인 방식입니다.MCS-251 패밀리는 인텔에 의해서도 단종되었습니다만, 많은 메이커의 바이너리 호환성과 부분적으로 강화된 변형으로 폭넓게 구입할 수 있습니다.

「 」를 참조해 주세요.

- DS80C390

- Hitachi HD44780 - XRAM 호환 인터페이스 탑재 LCD 컨트롤러

- 인텔 PL/M-51

- SDK-51 시스템 설계 키트

레퍼런스

- ^ 존 와튼:인텔 MCS-51 싱글칩 마이크로컴퓨터 패밀리 개요, 애플리케이션 노트 AP-69, 1980년 5월, Intel Corporation.

- ^ Intel 8051 Microprocessor Oral History Panel (PDF), Computer History Museum, September 16, 2008, archived from the original (PDF) on February 25, 2012, retrieved November 17, 2018

- ^ a b c "Intel MCS 151 and MCS 251 Microcontrollers". datasheets.chipdb.org.

- ^ 존 와튼: Wayback Machine Application Note AP-70, 1980년 5월 Intel Corporation에서 아카이브된 인텔 MCS-51 Boolean Processing Capabilities 사용 2016-03-03.

- ^ "8051 Tutorial: Interrupts". Archived from the original on 2012-12-28. Retrieved 2012-12-21.

- ^ "TASKING". www.tasking.com.

- ^ a b "8-bit Microcontrollers - 8-bit MCUs - EFM8 - Silicon Labs". www.silabs.com. Retrieved 2021-06-21.

- ^ "Site Search Maxim Integrated". www.maximintegrated.com. Retrieved 2021-06-21.

- ^ a b "8051 MCUs Microchip Technology". www.microchip.com. Retrieved 2021-06-21.

- ^ "TK80H51 250ºC Microcontroller". Tekmos Inc. Archived from the original on 20 August 2017. Retrieved 23 August 2017.

- ^ "HIGH TEMPERATURE 83C51 MICROCONTROLLER" (PDF). Honeywell. Retrieved 23 August 2017.

- ^ "Microcontrollers and Microprocessors". Cobham Semiconductor Solutions. Archived from the original on 23 August 2017. Retrieved 23 August 2017.

- ^ a b "Микроконтроллеры" [Microcontrollers] (in Russian). Voronezh: OAO "NIIET". Archived from the original on 22 August 2017. Retrieved 22 August 2017.

- ^ "Archived copy". Archived from the original on 2017-08-22. Retrieved 2017-08-22.

{{cite web}}: CS1 maint: 제목으로 아카이브된 복사(링크) - ^ Ghostarchive 및 Wayback Machine에서 아카이브:

- ^ "ELEC2700 - Computer Engineering 2 - University of Newcastle - Textbooks Zookal.com". www.zookal.com.

- ^ http://s3.amazonaws.com/f01.justanswer.com/88willy/2012-06-29_065532_assignment_03.pdf[베어 URL PDF]

- ^ a b c Keil C51 Users' Manual. Keil, a division of ARM Inc. 2021. Retrieved 17 May 2021.

- ^ ACALL은 2바이트의 서브루틴 호출 명령으로, 같은 2KB의 메모리 세그먼트내의 로케이션에 액세스 할 수 있습니다.절대 메모리 주소는 PC의 상위 5비트와 명령에 의해 정의된 11비트로 구성됩니다.

- ^ a b "Silergy 71M6513 Data sheet". Silergy electricity metering ICs. Silergy Corp. Retrieved 17 May 2021.

- ^ a b c d e MCS-51 Microcontroller Family User's Manual (PDF). publication number 121517: Intel. 1994. Retrieved 17 May 2021.

{{cite book}}: CS1 유지보수: 위치(링크) - ^ Han-Way Huang. "C8051에 내장된 시스템 설계." 페이지 238.

- ^ 르윈 A. R. W. 에드워즈「임베디드 엔지니어가 되고 싶다고? 컨설팅에서 기업 사다리까지 임베디드 엔지니어링 가이드」. 2006. 페이지 51.

- ^ 브래드포드 J. 로드리게스입니다"CamelForth/8051"

- ^ 브래드 로드리게스."이동 7부: 8051을 위한 카멜포스"

- ^ "8051 SwiftX Forth 개발"2015-09-24 Wayback Machine에서 보관

- ^ "MPE VFX Forth 7 크로스 컴파일러"

- ^ Ganssle, Jack (2006-05-29). "Intel bows out, discontinues MCS-51".

- ^ "MCS 51, MCS 251 and MCS 96 Microcontroller Product Lines, the Intel 186, Intel386 and Intel486 Processors Product Lines, and the i960 32 Bit RISC Processor, PCN 106013-01, Product Discontinuance, Reason for Revision: Add Key Milestone information and revise description of change" (PDF). Intel. 2006-05-02.

- ^ http://www.analog.com/static/imported-files/data_sheets/ADUC832.pdf[베어 URL PDF]

- ^ "Микроконтроллеры и супервизоры питания Серии 1880; 1881; 1842; 588; 1345; 5518АП1ТБМ" [Microcontrollers and Power Supervisors Series 1880; 1881; 1842; 588; 1345; 5518AP1TBM] (in Russian). Minsk: OAO "Integral". Retrieved 6 January 2017.

- ^ "Однокристальные микро-эвм" [Single-chip microcomputers] (in Russian). Kyiv: Kristall. Archived from the original on 30 May 2012. Retrieved 5 January 2017.

- ^ Hussaini (20 August 2019). "Why do we have to use the 8051? Isn't it too old?". Technobyte. Retrieved 20 August 2019.

- ^ "DS80C320 High-Speed/Low-Power Microcontrollers - Maxim Integrated". www.maximintegrated.com. Retrieved 2021-06-21.

- ^ "Syntill8 - Products". www.syntill8.com. Retrieved 2021-06-21.

- ^ "SDA30C164 Datasheet" (PDF). www.semiee.com. Retrieved 2022-05-15.

- ^ "Silergy Metering ICs". Silergy Corp. Retrieved 12 May 2021.

- ^ "Silergy Energy Measurement ICs". Silergy Corp. Retrieved 12 May 2021.

- ^ datasheetq.com. "89V54RD2 Datasheet PDF Download - Silicon Storage Technology". www.datasheetq.com. Retrieved 2020-01-18.

- ^ "STC Microcontroller---STCmicro Technology Co,.Ltd". www.stcmicro.com. Retrieved 2017-02-19.

- ^ "site index - Nanjing Qinheng Microelectronics Co., Ltd". wch-ic.com. Retrieved 2021-06-21.

- ^ "TI Delivers new low-cost, high-performance audio DSP for Home and Car w/ 8051". Archived from the original on 2016-11-13. Retrieved 2013-05-06.

- ^ "Atmel AT85C51SND3 Audio DSP Data Sheet with USB 2.0" (PDF).

- ^ Salim, A.J.; Othman, M.; Ali, M.A. Mohd (October 5, 2006). "Integration of 8051 With DSP in Xilinx FPGA". 2006 IEEE International Conference on Semiconductor Electronics. pp. 562–566. doi:10.1109/SMELEC.2006.380694. ISBN 0-7803-9730-4. S2CID 21616742 – via IEEE Xplore.

- ^ 8051 마이크로컨트롤러 By Kenneth J Ayala Google books

- ^ http://datasheets.chipdb.org/Intel/MCS51/DATASHTS/27262001.PDF[베어 URL PDF]

- ^ "Temic TSC80251 Architecture" (PDF).

- ^ "Atmel TSC80251 Programmers Guide" (PDF). Archived from the original (PDF) on 2016-03-04. Retrieved 2013-05-06.

- ^ DQ80251 32비트 마이크로컨트롤러 DCD

- ^ R80251XC 32비트 마이크로컨트롤러 Evatronix[dead link]

추가 정보

- 책들

- Mazidi; McKinlay; Mazidi (2012). The 8051 Microcontroller: A Systems Approach. 648 pp. ISBN 978-0-13-508044-3.

- Schultz, Thomas (2008). C and the 8051 (4th ed.). 464 pp. ISBN 978-0-9783995-0-4.

- Steiner, Craig (2005). The 8051/8052 Microcontroller: Architecture, Assembly Language, and Hardware Interfacing. 348 pp. ISBN 978-1-58112-459-0.

- Calcutt; Cowan; Parchizadeh (2000). 8051 Microcontrollers: Hardware, Software and Applications. 329 pp. ISBN 978-0-340-67707-0.

- Axelson, Jan (1994). The Microcontroller Idea Book: Circuits, Programs, and Applications featuring the 8052-BASIC Microcontroller. 277 pp. ISBN 978-0-9650819-0-0.

- Payne, William (December 19, 1990) [1990]. Embedded Controller FORTH for the 8051 Family (hardcover). Boston: Academic Press. 528 pp. ISBN 978-0-12-547570-9.

- 인텔(R)

- MCS-51 마이크로컨트롤러 패밀리 사용자 매뉴얼, 인텔, 1994, 발행번호 121517.

- MCS-51 매크로 어셈블러 유저즈 가이드, 인텔, 발행 번호9800937.

- 8 비트 임베디드 컨트롤러, 인텔, 1991년, 발행 번호 270645-003.

- 마이크로컨트롤러 핸드북, 인텔; 1984, 발행번호 210918-002.

- 8051 마이크로컨트롤러 예비 아키텍처 사양 및 기능 설명, 인텔, 44페이지, 1980.

- 기타

- Hennig-Roleff, Werner (1993-02-01) [1988]. "HEX.DOC: EASM51 - HEX Format (elektor Assembler)". SIM51. 1.04 (in German). Archived from the original on 2017-08-11. Retrieved 2021-12-08. [1] [2] (HEX).DOC 파일에서는 인텔, Motorola, Tektronix, MOS 테크놀로지 및 elektor에 의한 다양한 16진수 파일 형식에 대해 설명합니다.)

외부 링크

![]() Wikimedia Commons의 MCS-51 관련 미디어

Wikimedia Commons의 MCS-51 관련 미디어