4상 논리학

Four-phase logic4상 로직은 동적 로직을 위한 설계 방법론의 일종이다. 그것은 비전문가인 엔지니어가 PMOS 또는 NMOS 프로세스를 사용하여 상당히 복잡한 IC를 설계할 수 있도록 했다. 일종의 4상 클럭 신호를 사용한다.

역사

오토네틱스의 엔지니어인 R. K. "밥" 부어는 4상 논리를 발명하여 페어차일드 반도체의 프랭크 완글스에게 이 아이디어를 전달했고 완글스는 제너럴 Instrument Microelectronics 사업부에서 이 논리 형식을 홍보했다.[1] 부허는 1966년 2월 처음으로 4상 칩인 오토네틱스 DDA 통합업체를 만들었다. 그는 나중에 이 기술을 사용하여 오토네틱스 D200 공수 컴퓨터를 설계했다.[2]

1967년 4월 조엘 카프와 엘리자베스 드 앳리는 전자 디자인 매거진에 '4상 MOS IC 논리 사용'이라는 글을 실었다.[3] 같은 해 코헨, 루벤슈타인, 완글라스는 「MTOS 4상 시계 시스템」을 출판했다.[4] 완라스는 1964년 페어차일드 반도체를 떠난 뒤 뉴욕 제너럴 Instrument Microelectronics 사업부의 연구 엔지니어링 이사로 재직해 왔다.

완라스의[5] 제자로 페어차일드반도체 설계자, 후기 4상 시스템즈 설립자인 이보젤은 1967년 10월 국제전자소자회의에서 4상 8비트 애드더 장치에 대해 '늦은 뉴스'를 했다.[6] 제너럴 Instrument Microelectronics Division의 MOS Operation 매니저인 J. L. 실리도 1967년 말에 4상 논리에 대해 썼다.[7]

1968년에 보이셀은 "칩에 대한 Adder on a Chip: LSI Help Cossible of Small Machine"이라는 기사를 Electronics 잡지에 실었다;[8] Y의 4단계 논문. T. 옌도 그 해에 등장한다.[9][10] 다른 신문들도 곧 뒤따랐다.[11]

보이젤은 4상 동적 논리로 당시 사용하던 다른 MOS 기법(금속게이트 포화 부하 PMOS 논리)에 비해 패킹 밀도 10배, 속도 10배, 전력 1/10을 페어차일드(Fairchild)[12]에서 1세대 MOS 공정을 사용해 달성할 수 있었다고 회상한다.

구조

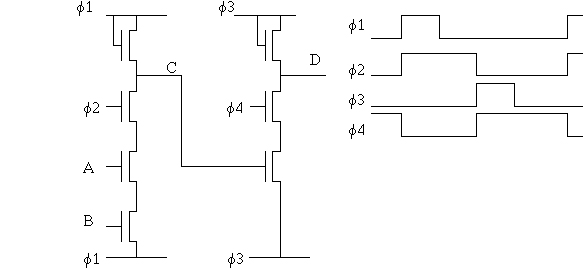

논리 게이트에는 기본적으로 '1' 관문과 '3' 관문이 있다. 이것들은 단지 그것들을 구동하는 데 사용되는 시계 단계에서만 다르다. 게이트는 어떤 논리적인 기능도 가질 수 있다. 따라서 잠재적으로 모든 게이트는 맞춤화된 레이아웃을 가지고 있다. 시계 단계(예: NMOS 트랜지스터 사용)와 함께 2입력 NAND 1 게이트와 인버터 3 게이트의 예가 아래에 나와 있다.

ϕ1과 ϕ3 시계는 ϕ2와 ϕ4 시계처럼 겹치지 않아야 한다. 1개의 게이트를 고려하여, ϕ1 클럭 하이 타임(예비충전 시간이라고도 함) 동안 출력 C는 V(ϕ1)-V까지th 사전충전되며, 여기서 V는th 사전충전 트랜지스터의 임계값을 나타낸다. 다음 1/4 클럭 사이클(샘플 시간) 동안 11이 낮고 22가 높을 때 C는 높은 상태를 유지하거나(A 또는 B가 낮은 경우) C는 낮은 상태로 배출된다(A와 B가 높은 경우).

A와 B 입력은 이 샘플 시간 동안 안정적이어야 한다. 이 시간 동안 출력 C가 유효하므로 1 게이트 출력은 다른 1 게이트 입력을 구동할 수 없다. 그러므로 1개의 문이 3개의 관문을 먹여살려야 하고 그들은 차례로 1개의 관문을 먹여살려야 한다.

한 가지 더 유용한 것은 – 2문과 4문이다. 게이트 2개는 ϕ1에 예치하고 샘플은 33에 부과한다.

gate3에는 4개의 관문이, ϕ1에는 샘플이 예치된다.

관문 상호 연결 규칙은 다음과 같다: 1개의 관문은 2개의 관문 및/또는 3개의 관문을 구동할 수 있으며, 2개의 관문은 3개의 관문만 구동할 수 있고, 3개의 관문은 4개의 관문 및/또는 1개의 관문을 구동할 수 있으며, 4개의 관문은 1개의 관문만 구동할 수 있다.

사용법

4상 로직은 잘 작동한다. 특히 모든 결합 논리 게이트에는 기록부가 포함되어 있기 때문에 인종적 위험이 없다. 이 레이아웃은 어떤 전원 공급 장치의 버스킹을 필요로 하지 않고 시계 라인만 버스 연결된다는 점에 주목할 필요가 있다. 또한, 설계 기법이 불변(cf. static logic)이기 때문에, 많은 설계는 최소 크기의 트랜지스터를 사용할 수 있다.

다음과 같은 어려움이 있다.

- 게이트 출력은 동적이다. 이것은 그것의 상태가 게이트 출력에서 캐패시턴스로 유지된다는 것을 의미한다. 그러나 출력 트랙은 클럭 라인과 다른 게이트 출력을 교차할 수 있으며, 이 모든 것이 캐패시터의 전하를 변화시킬 수 있다. 사이클 중에 게이트 출력 전압이 안전한 0 또는 1 레벨을 유지하려면 변화량을 계산하고 필요한 경우 출력 노드에 추가(디퓨전) 캐패시턴스를 추가해야 한다.

- 주어진 공급 전압, 프로세스 및 클럭 주파수에 대해 설계자는 배치 엔지니어가 각 게이트에 필요한 '전구 업' 캐패시턴스를 계산하도록 몇 가지 계산을 수행해야 한다. 캐패시턴스 부하가 많은 게이트는 최소 입력 트랜지스터보다 더 큰 용량이 필요할 수 있다(부하가 제시간에 방전될 수 있도록 하기 위해). 이는 차례로 게이트의 입력을 구동하는 게이트의 부하를 증가시킨다. 따라서 특히 고주파 설계의 경우 속도 목표가 너무 공격적이면 게이트 사이징이 계속 증가할 수 있다.

최초의 전자 계산기 고밀도 집적 회로와(LSI)은 건설된 샤프 QT-8D은 1969년부터 일본 아직 국내에서 그렇게 할 것을 LSI기술을 가지고 있지 않록웰 인터내셔널이 조작된 것이었다 4-phase 논리를 사용했다.[13]4-phase적 논리는 인텔 4004에 사용할 수 있지만, 오직 록웰기 위한 설계를 있었다.그 당시 대규모 4상 IC를 할 수 있는 올과 전문지식을 통해 인텔은 대신 2상 동적 논리에 정착했다. [14]

진화

CMOS의 출현과 함께, 프리차지 트랜지스터는 로직 트랜지스터 타입의 보완재가 될 수 있어 게이트의 출력이 클럭 라인의 높은 레벨까지 빠르게 충전할 수 있어 속도, 신호 스윙, 전력 소비량, 노이즈 마진을 개선할 수 있다. 이 기술은 도미노 논리에 쓰인다.

참조

- ^ Ross Knox Bassett (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. JHU Press. pp. 129–130. ISBN 978-0-8018-8639-3.

- ^ "CSDL IEEE Computer Society". doi:10.1109/AFIPS.1968.126. Cite 저널은 필요로 한다.

journal=(도움말) - ^ Bernard Finn; Robert Bud; Helmuth Trischler (2000). Exposing electronics. CRC Press. p. 133. ISBN 978-90-5823-057-7.

- ^ L. Cohen; R. Rubenstin; F. Wanlass (1–3 November 1967), "MTOS four phase clock systems", Northeast Electronics Research and Engineering Meeting (NEREM) Record, 9, pp. 170–171

- ^ Ross Knox Bassett (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. JHU Press. p. 122. ISBN 978-0-8018-8639-3.

- ^ L. Boysel; J. Kelley; R. Cole (October 1967), "MOS/LSI 8-Bit Parallel Accumulator", International Electron Devices Meeting (IEDM), 15 (6), pp. 2–3, Bibcode:1968ITED...15..410B, doi:10.1109/T-ED.1968.16205

- ^ J. L. Seely (March 1967). "Advances in the state-of-the-art of MOS device technology". Solid State Technology. 10: 55–62. ISBN 9780070231498.

- ^ Lee L. Boysel (18 March 1968). "Adder on a Chip: LSI Helps Reduce Cost of Small Machine". Electronics. 18: 119–123.

- ^ Y. T. Yen(1968) "논리 시뮬레이션을 위한 4상 MOS 회로 특성화 수학 모델" IEEE 컴퓨터 거래: C-17 1968년 9월

- ^ Y. T. 옌(1968) "4상 MOS 회로의 불순전한 고장 문제" IEEE 솔리드 스테이트 회로 저널: SC-4 6월 3일. 1969

- ^ 모자 R. J. 자켓 A. E. & Jarvis D. 관련 반도체 제조업체의 B. "통합 m-o-s 트랜지스터를 사용한 4상 로직 회로" Mullard 기술 통신: No 99 1969년 5월

- ^ Lee Boysel (10/12/2007). "Making Your First Million (and other tips for aspiring entrepreneurs)". U. Mich. EECS Presentation / ECE Recordings. Archived from the original on 15 November 2012. 날짜 값 확인:

date=(도움말) - ^ "Sharp QT-8D".

- ^ "The New Methodology for Random Logic Design".