이중 인라인 패키지

Dual in-line package

마이크로일렉트로닉스에서 듀얼 인라인 패키지([1]DIP 또는 DIL)는 직사각형 하우징과 두 개의 평행한 전기 연결 핀 열을 가진 전자 부품 패키지입니다. 패키지는 PCB(printed circuit board)에 장착되거나 소켓에 삽입될 수 있습니다. 이중 인라인 포맷은 1964년 페어차일드 R&D의 돈 포브스, 렉스 라이스, 브라이언트 로저스에 의해 발명되었는데,[2] 이때 원형 트랜지스터 스타일 패키지에서 사용할 수 있는 제한된 리드 수가 집적 회로 사용에 제한이 되었습니다.[3] 회로가 점점 복잡해짐에 따라 더 많은 신호 및 전원 공급 리드가 필요하게 되었습니다(렌트의 규칙에서 관찰된 바와 같이). 결국 마이크로프로세서 및 이와 유사한 복잡한 장치는 DIP 패키지에 넣을 수 있는 리드보다 더 많은 리드가 필요하게 되었고, 이로 인해 고밀도 칩 캐리어가 개발되었습니다. 또한 사각형 및 직사각형 패키지를 사용하면 패키지 아래에 인쇄 회로 흔적을 더 쉽게 경로 지정할 수 있습니다.

DIP는 일반적으로 DIPn이라고 하며, 여기서 n은 총 핀 수입니다. 예를 들어, 7개의 수직 리드로 구성된 두 줄의 미세 회로 패키지는 DIP14가 될 것입니다. 오른쪽 상단의 사진에는 3개의 DIP14 IC가 표시되어 있습니다. 일반 패키지에는 적게는 3개, 많게는 64개의 리드가 있습니다. 트랜지스터, 스위치, 발광 다이오드 및 저항 어레이와 마찬가지로 많은 아날로그 및 디지털 집적 회로 유형을 DIP 패키지로 사용할 수 있습니다. 리본 케이블용 DIP 플러그는 표준 IC 소켓과 함께 사용할 수 있습니다.

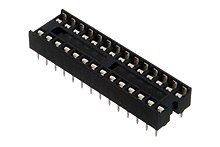

DIP 패키지는 일반적으로 장치 다이를 지지하고 연결 핀을 제공하는 주석, 은 또는 금 도금 리드 프레임 주위에 압착된 불투명 성형 에폭시 플라스틱으로 만들어집니다. 일부 유형의 IC는 고온 또는 높은 신뢰성이 필요한 세라믹 DIP 패키지 또는 장치에 패키지 내부에 광학 창이 있는 경우에 만들어집니다. 대부분의 DIP 패키지는 기판의 구멍을 통해 핀을 삽입하고 제자리에 납땜하여 PCB에 고정됩니다. 테스트 고정 장치와 같이 부품 교체가 필요하거나 변경을 위해 프로그래밍 가능한 장치를 제거해야 하는 경우 DIP 소켓을 사용합니다. 일부 소켓에는 ZIF(Zero Insertion Force) 메커니즘이 포함되어 있습니다.

DIP 패키지의 변형에는 두 번째 줄 핀 대신 히트 싱크 탭을 포함한 저항기 어레이와 패키지의 각 면에 4줄의 핀, 2줄의 핀이 엇갈린 유형이 포함됩니다. DIP 패키지는 PCB에 구멍을 뚫는 비용을 피하고 더 높은 밀도의 상호 연결을 허용하는 표면 장착 패키지 유형에 의해 대부분 대체되었습니다.

적용들

기기의 종류

DIP는 일반적으로 IC(Integrated Circuit)에 사용됩니다. DIP 패키지의 다른 장치에는 저항기 네트워크, DIP 스위치, LED 세그먼트 및 막대 그래프 디스플레이, 전기 기계식 릴레이가 포함됩니다.

리본 케이블용 DIP 커넥터 플러그는 컴퓨터 및 기타 전자 장비에서 일반적입니다.

Dallas Semiconductor는 IC 칩과 교체가 불가능한 10년 리튬 배터리를 포함하는 통합 DIP 실시간 클럭(RTC) 모듈을 제조했습니다.

개별 구성 요소를 납땜할 수 있는 DIP 헤더 블록은 구성 변경, 옵션 기능 또는 보정을 위해 구성 요소 그룹을 쉽게 제거해야 하는 곳에 사용되었습니다.

사용하다

원래의 듀얼 인 라인 패키지는 1964년 페어차일드 반도체에서 근무하던 브라이언트 "벅" 로저스가 발명했습니다. 첫 번째 장치는 14개의 핀을 가지고 있었고 오늘날과 매우 유사해 보였습니다.[4] 직사각형 모양으로 인해 이전 라운드 패키지보다 집적 회로를 더 조밀하게 패키징할 수 있었습니다.[5] 패키지는 자동화된 조립 장비에 적합했습니다. PCB는 점수 또는 수백 개의 IC로 채워질 수 있었고, 회로 기판의 모든 구성 요소는 웨이브 솔더링 기계에 한 번에 솔더링되어 자동화된 테스트 기계로 전달될 수 있었고, 사람의 노동력은 거의 필요하지 않았습니다. DIP 패키지는 여전히 그들 내부의 집적 회로와 관련하여 컸습니다. 20세기 말까지 표면 장착 패키지를 통해 시스템의 크기와 무게를 더욱 줄일 수 있었습니다. DIP 칩은 쉽게 삽입하고 사용할 수 있기 때문에 빵판의 회로 프로토타입으로 여전히 인기가 있습니다.

DIP는 1970년대와 1980년대에 마이크로전자 산업의 주류였습니다. 이들의 사용은 플라스틱 리드 칩 캐리어(PLCC) 및 소출력 집적 회로(SOIC)와 같은 새로운 표면 장착 기술(SMT) 패키지로 인해 21세기 첫 10년 동안 감소했지만 DIP는 1990년대까지 광범위하게 사용되었으며 2011년이 지나면서 여전히 상당 부분 사용되고 있습니다. 일부 최신 칩은 표면 장착 패키지 유형에서만 사용할 수 있기 때문에 많은 회사에서 이러한 표면 장착 장치(SMD)를 관통 구멍 빵판과 납땜된 프로토타이핑 보드(예: 스트립보드 및 퍼보드)가 있는 DIP 장치처럼 사용할 수 있도록 다양한 프로토타이핑 어댑터를 판매하고 있습니다. (SMT는 일반적으로 프로토타이핑에 있어 최소한 불편함을 줄 수 있습니다. 대량 생산에 있어 장점인 SMT의 대부분의 특성은 프로토타이핑의 어려움입니다.)

EPROM 및 GAL과 같은 프로그래밍 가능한 장치의 경우, DIP는 외부 프로그래밍 회로와 쉽게 다룰 수 있기 때문에 수년 동안 인기를 유지했습니다(즉, DIP 장치는 프로그래밍 장치의 소켓에 간단히 꽂을 수 있습니다). 그러나 현재 ISP(In-System Programming) 기술이 최첨단으로 발전함에 따라 DIP의 이러한 장점도 빠르게 중요성을 잃어가고 있습니다.

1990년대를 거치면서 리드가 20개 미만인 장치는 새로운 형식에 추가하여 DIP 형식으로 제조되었습니다. 약 2000년 이후로 더 새로운 장치를 DIP 형식으로 사용할 수 없는 경우가 많습니다.

장착

DIP는 관통 홀 솔더링 또는 소켓에 장착할 수 있습니다. 소켓을 사용하면 장치를 쉽게 교체할 수 있으며 납땜 중 과열로 인한 손상 위험을 제거합니다. 일반적으로 소켓은 소켓보다 훨씬 비싼 고가 또는 대형 IC에 사용되었습니다. 테스트 장비나 EPROM 프로그래머와 같이 장치를 자주 삽입하고 제거하는 경우에는 제로 삽입력 소켓이 사용됩니다.

DIP는 교육, 디자인 개발 또는 장치 테스트를 위한 임시 장착 배열인 브레드보드와 함께 사용됩니다. 일부 애호가들은 일회성 구성이나 영구 프로토타이핑을 위해 DIP와 함께 점대점 배선을 사용하며, 이 방법의 일부로 물리적으로 반전되었을 때의 모습은 이 방법에 대해 "데드 버그 스타일"이라는 비공식 용어를 불러일으킵니다.

- 16핀, 14핀 및 8핀 DIP IC용 듀얼 와이퍼 접점이 있는 0.3인치 와이드 DIP 소켓

- 0.3인치 와이드 16핀 DIP 소켓(DIP-16 IC용 가공 원형 접점 포함)

- EPROMIC 프로그래머에서 일반적으로 사용되는 0.6" 와이드 DIP-28WIC용 ZIF(Zero insertion force) 소켓

- 폭이 좁은 DIP-28 IC용 0.3" 와이드 DIP 소켓(DIP-28N이라고도 함), 오래된 아두이노 보드에서 일반적으로 사용됨

- 28핀 IC 소켓에 ATmega328P 8비트 마이크로컨트롤러 탑재 아두이노 UNOR2 보드

시공

IC 칩을 포함하는 DIP의 몸체(하우징)는 일반적으로 성형된 플라스틱 또는 세라믹으로 만들어집니다. 세라믹 하우징의 기밀성은 매우 높은 신뢰성 장치에 선호됩니다. 그러나, 대부분의 DIP는 에폭시 몰드 화합물이 압력 하에서 가열되고 이송되어 소자를 캡슐화하는 열경화성 성형 공정을 통해 제조됩니다. 수지의 일반적인 경화 주기는 2분 이내이며 한 번의 주기로 수백 개의 장치가 생성될 수 있습니다.

리드는 솔기를 따라 패키지의 긴 측면에서 나오며, 패키지의 상단 및 하단 평면에 평행하며, 아래쪽으로 약 90도(또는 약간 작게) 구부러져 있으며, 패키지 본체의 중심선에서 바깥쪽으로 약간 치우쳐 있습니다. (일반적인 DIP와 가장 유사한 SMT 패키지인 SOIC는 크기 척도에도 불구하고 본질적으로 동일하게 나타납니다. 단, 아래로 구부러진 후 리드가 패키지의 바닥면과 평행이 되도록 동일한 각도만큼 다시 위쪽으로 구부러집니다.) 세라믹(CERDIP) 패키지의 경우 에폭시 또는 그라우트를 사용하여 두 개의 절반을 밀봉하여 내부의 IC 다이를 보호하기 위해 공기와 습기를 단단히 고정합니다. 플라스틱 DIP(Pastic DIP) 패키지는 보통 리드 주변의 플라스틱 절반을 융착 또는 접착하여 밀봉하지만, 플라스틱 자체는 일반적으로 습기에 다소 다공성이고 공정이 둘레 주변의 모든 지점에서 리드와 플라스틱 사이의 우수한 미세 밀봉을 보장할 수 없기 때문에 높은 수준의 기밀성을 달성할 수 없습니다. 그러나 일반적으로 오염 물질은 여전히 충분히 잘 보관되어 있기 때문에 통제된 환경에서 수십 년 동안 장치를 합리적으로 주의하여 안정적으로 작동할 수 있습니다.

패키지 내부에는 하부 절반에 리드가 내장되어 있으며, 패키지 중앙에는 IC 다이가 시멘트로 접합되는 직사각형 공간, 챔버 또는 공극이 있습니다. 패키지의 리드는 주변부를 따라 출현 위치에서 다이를 둘러싸는 직사각형 둘레를 따라 포인트로 패키지 내부에서 대각선으로 연장되며 다이에서 미세 접촉이 될 때 테이퍼집니다. 이러한 다이 주변 접점과 다이 자체 상의 본드 패드 사이에는 초미세 본드 와이어(사람의 눈에 거의 보이지 않음)가 용접되어, 하나의 리드를 각각의 본드 패드에 연결하고, 마이크로 회로와 외부 DIP 리드 사이에 최종적으로 연결됩니다. 본드 와이어는 일반적으로 팽팽하지 않지만 재료의 열 팽창 및 수축을 위해 느슨하게 하기 위해 약간 위쪽으로 루프를 형성합니다. 본드 와이어 하나가 끊어지거나 분리되면 IC 전체가 무용지물이 될 수 있습니다. 패키지 상단은 본드 와이어를 파쇄하지 않고 이 모든 섬세한 조립을 커버하여 이물질에 의한 오염으로부터 보호합니다.

일반적으로 회사 로고, 영숫자 코드 및 때로는 단어가 패키지 상단에 인쇄되어 제조업체 및 유형(일반적으로 1년 1주 번호), 때로는 제조업체 및 기타 독점 정보(아마도 수정 번호, 제조 공장 코드 또는 단계 ID 코드)를 식별합니다.

패키지의 주변부에서 다이 둘레로부터 2개의 열까지 기본적으로 단일 평면에서 모든 리드를 방사형 패턴으로 배치해야 하는 필요성은 더 높은 리드 카운트를 갖는 DIP 패키지가 리드 열들 사이에 더 넓은 간격을 가져야 하는 주된 이유입니다. 그리고 실용적인 DIP 패키지가 가질 수 있는 리드의 수를 효과적으로 제한합니다. 본드 패드가 많은 매우 작은 다이(예: 15개의 인버터가 있는 칩, 32개의 리드가 필요함)의 경우에도 방사 리드를 내부에 수용하려면 더 넓은 DIP가 여전히 필요합니다. 이것이 PGA와 같은 4면 및 다열 패키지가 도입된 이유 중 하나입니다(1980년대 초반경).

대형 DIP 패키지(예: 모토로라 68000 CPU에 사용되는 DIP64)는 핀과 다이 사이의 패키지 내부에 긴 리드가 있어 고속 장치에 적합하지 않습니다.

다른 유형의 DIP 장치는 매우 다르게 제작됩니다. 이들 대부분은 성형된 플라스틱 하우징과 패키지 바닥에서 바로 밖으로 연장되는 직선 리드 또는 리드가 있습니다. 일부, 특히 LED 디스플레이의 경우, 하우징은 보통 바닥/뒷면이 개방된 중공 플라스틱 상자이며, (포함된 전자 부품 주위에) 리드가 나오는 단단한 반투명 에폭시 물질로 채워져 있습니다. DIP 스위치와 같은 다른 것들은 두 개(또는 그 이상)의 플라스틱 하우징 부품들이 접촉부들과 작은 기계 부품들의 세트 주위에서 서로 끊어지거나, 용접되거나, 접착되는 것들로 구성되며, 리드들은 플라스틱의 몰딩된 구멍들 또는 노치들을 통해 나옵니다.

변종

IC에 대한 여러 DIP 변형이 존재하며, 대부분 포장 재료에 따라 구별됩니다.

- 세라믹 듀얼 인라인 패키지(CERDIP 또는 CDIP)

- 플라스틱 이중 인라인 패키지(PDIP)

- 수축 플라스틱 이중 인라인 패키지(SPDIP) – 0.07인치(1.778mm) 리드 피치를 가진 PDIP의 조밀한 버전입니다.

- Skinny dual in-line package (SDIP 또는 SPDIP[6]) – "좁은" 0.300인치를 가리키는 데 사용되기도 합니다. (또는 300 mil) 와이드 DIP, 일반적으로 와이드 DIP 패키지에 "와이드" 0.600으로 제공되는 24개 이상의 핀을 가진 DIP의 경우와 같이 설명이 필요한 경우. "좁은" DIP 패키지에 대한 일반적인 적절한 전체 사양의 예로는 300 mil 본체 너비, 0.1 인치(2.54 mm) 핀 피치가 있습니다.

EPROM은 그 부분이 자외선에 의해 지워질 수 있도록 칩 다이 위에 투명한 석영의 원형 창으로 제조된 세라믹 DIP에서 판매되었습니다. 종종 동일한 칩이 OTP(one-time programmable) 버전으로 더 저렴한 윈도우리스 PDIP 또는 CERDIP 패키지로 판매되기도 했습니다. 윈도우 및 윈도우가 없는 패키지는 또한 EPROM 메모리를 포함하는 마이크로컨트롤러 및 기타 장치에 사용되었습니다. 윈도우 CERDIP 패키지 EPROM은 윈도우를 덮는 접착 라벨이 있는 초기 IBM PC 클론의 BIOS ROM에 사용되어 주변광 노출을 통한 의도치 않은 삭제를 방지했습니다.

성형 플라스틱 DIP는 세라믹 패키지보다 비용이 훨씬 저렴합니다. 1979년의 한 연구에 따르면 플라스틱 14핀 DIP의 비용은 미화 약 0.063달러, 세라믹 패키지의 비용은 미화 약 0.82달러인 것으로 나타났습니다.[7]

싱글인라인

단일 인라인 패키지(SIP 또는 SIL 패키지)[8]에는 연결 핀이 한 줄 있습니다. DIP만큼 대중적이지는 않지만 공통 핀으로 RAM 칩과 다중 저항을 패키징하는 데 사용되었습니다. 일반적인 최대 핀 수가 64개인 DIP에 비해 SIP는 패키지 비용이 낮은 일반적인 최대 핀 수가 24개입니다.[9]

단일 인라인 패키지의 한 변형은 히트 싱크 탭을 위해 리드 프레임의 일부를 사용합니다. 이 다중 리드 전력 패키지는 예를 들어 오디오 전력 증폭기와 같은 응용 분야에 유용합니다.

쿼드인라인

QIL 패키지라고 불리기도 하는 QIP는 DIL 패키지와 동일한 치수를 갖지만, 각 면의 리드는 4개의 솔더 패드 라인(DIL이 있는 2개 대신)에 맞게 번갈아 가며 지그재그 구성으로 구부러져 있습니다. QIL 설계는 패키지 크기를 늘리지 않고 솔더 패드 사이의 간격을 늘린 이유는 다음 두 가지입니다.

- 더 신뢰할 수 있는 납땜을 가능하게 했습니다. 지금은 사용 중인 솔더 패드 간격이 훨씬 가깝다는 점을 감안하면 오늘날 이것은 이상하게 보일 수 있지만, QIL의 전성기였던 1970년대에는 DIL 칩에 인접한 솔더 패드를 브리징하는 것이 가끔 문제가 되었습니다.

- QIL은 또한 2개의 솔더 패드 사이에 구리 트랙을 운영할 수 있는 가능성을 높였습니다. 이는 당시 표준 편면 단층 PCB에서 매우 유용했습니다.

리드 카운트 및 간격

JEDEC 표준을 따르는 일반적인 DIP 패키지는 0.1인치(2.54mm)(JEDEC MS-001BA)의 리드 간 간격(리드 피치)을 사용합니다. 행 간격은 리드 수에 따라 다르며, 0.3인치(7.62mm)(JEDEC MS-001) 또는 0.6인치(15.24mm)(JEDEC MS-011)가 가장 일반적입니다. 덜 일반적인 표준화된 행 간격에는 0.4인치(10.16mm)(JEDEC MS-010) 및 0.9인치(22.86mm)뿐만 아니라 0.3인치, 0.6인치 또는 0.75인치의 행 간격과 0.07인치(1.778mm) 리드 피치가 포함됩니다.

구소련과 동구권 국가들은 비슷한 패키지를 사용했지만, 0.1인치(2.54mm)가 아닌 2.5mm의 미터법으로 핀 대 핀 간격을 사용했습니다.

리드의 수는 항상 균등합니다. 0.3인치 간격의 경우 일반적인 리드 카운트는 8, 14, 16, 18 및 28이며, 덜 일반적인 리드 카운트는 4, 6, 20 및 24입니다. 리드 수가 짝수인 경우 일부 DIP는 미사용 NC([nb 1]not connected)를 사용하여 내부 칩으로 연결되거나 2개의 접지 핀과 같이 중복됩니다. 0.6인치 간격의 경우 일반적인 리드 카운트는 24, 28, 32 및 40이며, 덜 일반적인 리드 카운트는 36, 42, 48, 52 및 64입니다. 모토로라 68000 및 Zilog Z180과 같은 일부 마이크로프로세서는 최대 64개의 리드 카운트를 사용했습니다. 이것은 일반적으로 DIP 패키지의 최대 리드 수입니다.[10]

방향 및 리드 번호 지정

그림과 같이 리드는 핀 1부터 연속적으로 번호가 매겨집니다. 패키지의 식별 노치가 상단에 있을 때 핀 1은 장치의 왼쪽 상단 모서리입니다. 핀 1이 움푹 들어간 곳이나 페인트 점 표시로 식별되는 경우가 있습니다.

예를 들어, 노치가 상단에 있는 14개 리드 DIP의 경우 왼쪽 리드는 1에서 7(위에서 아래)까지 번호가 매겨지고 오른쪽 리드 행은 8에서 14(아래에서 위)까지 번호가 매겨집니다.

일부 DIP 장치(예: 세그먼트화된 LED 디스플레이, 릴레이 또는 리드를 히트 싱크 핀으로 대체하는 장치)에서는 리드가 생략됩니다. 나머지 리드는 모든 위치에 리드가 있는 것처럼 번호가 매겨집니다.

노치는 패키지 방향에 대한 사람의 시각적 식별을 제공할 뿐만 아니라 자동화된 칩 삽입 기계가 기계적 감지를 통해 칩의 올바른 방향을 확인할 수 있도록 합니다.[citation needed]

후예

특히 가전제품과 개인용 컴퓨터에서 현재[when?] 매우 인기 있는 표면 장착 패키지인 SOIC(Small Outline IC)는 기본적으로 표준 IC PDIP를 축소한 버전입니다. 두 번째로 구부러진 리드를 SMT 장치로 만드는 근본적인 차이는 플라스틱 하우징의 바닥면에 평행하게 평평하게 만듭니다. SOJ(Small Outline J-lead) 및 이름에 "SOP"("Small Outline Package"용)가 포함된 다른 SMT 패키지는 원래 조상인 DIP의 친척으로 간주할 수 있습니다. SOIC 패키지는 DIP의 피치가 절반이고 SOP는 DIP의 피치의 1/4입니다. (각각 0.1"/2.54mm, 0.05"/1.27mm, 0.025"/0.635mm)

PGA(Pin Grid Array) 패키지는 DIP에서 발전한 것으로 간주될 수 있습니다. 대부분의 DIP가 1980년대 초부터 중반까지 마이크로프로세서에 인기가 있었던 것과 동일한 0.1인치(2.54mm) 핀 센터를 가진 PGA. 인텔 80286부터 P5 펜티엄 프로세서를 포함하는 개인용 컴퓨터 소유자들은 마더보드의 ZIF 소켓에 삽입되는 이러한 PGA 패키지를 가장 잘 알고 있을 것입니다. 유사성은 PGA 소켓이 일부 DIP 장치와 물리적으로 호환될 수 있지만 그 반대는 거의 사실이 아닙니다.

참고 항목

- 칩 캐리어

- DIP 스위치

- 플랫팩(전자제품)

- 집적 회로 패키지 치수 목록

- NORBIT 2 (1967년 도입된 더 큰 19핀 DIP)

- 핀 그리드 배열

- QFP

- 서피스마운트_기술

- 지그재그 인라인 패키지

메모들

참고문헌

- ^ 예를 들어 보다

- ^ Dummer, G.W.A. 전자 발명 및 발견 (2기), Pergamon Press, ISBN0-08-022730-9

- ^ 잭슨, 케네스.A.; 슈뢰터, 볼프강 반도체 기술 핸드북, John Wiley & Sons, 2000 ISBN 3-527-29835-5 페이지 610

- ^ 더머, G.W.A. 전자 발명 및 발견 2기 Pergamon Press ISBN 0-08-022730-9

- ^ 2008년 4월 16일 컴퓨터 박물관 회수

- ^ 예를 들어, 마이크로칩: http://www.microchip.com/packaging

- ^ Rao R. Tummala, Eugene J. Rymaszewski, Alan G. Kloppenstein Microelectronics 포장 핸드북: 반도체포장, 스프링어, 1997 ISBN 0-412-08441-4페이지 395

- ^ "Single-in-Line Package (SIP)". EE Semi. Archived from the original on August 18, 2021.

- ^ 페흐트, M. (1994). 집적 회로, 하이브리드 및 멀티칩 모듈 패키지 설계 지침입니다. 와일리-IEE.

- ^ Kang, Sung-Mo; Leblebici, Yusuf (2002). CMOS digital integrated circuits (3rd ed.). McGraw-Hill. p. 42. ISBN 0-07-246053-9.

이 문서에는 다음의 퍼블릭 도메인 자료가 포함되어 있습니다.

이 문서에는 다음의 퍼블릭 도메인 자료가 포함되어 있습니다.

추가읽기

- Intel (1996). Packaging Databook. Mcgraw-Hill. ISBN 1-55512-254-X. OCLC 906673879.