터보 SPARC

TurboSPARC | |

| 일반 정보 | |

|---|---|

| 개시. | 전( |

| 설계자 | 후지쯔 마이크로일렉트로닉스 주식회사 |

| 성능 | |

| 최대 CPU 클럭 속도 | 160MHz~180MHz |

| 아키텍처 및 분류 | |

| 명령 집합 | SPARC V8 |

| 물리 사양 | |

| 코어 |

|

TurboSPARC는 미국 캘리포니아주 새너제이 소재 다국적 정보기술 기기 및 서비스 회사인 Fujitsu Limited의 자회사인 Fujitsu Microelectronics, Inc.(FMI)에 의해 개발된 SPARC V8 명령 집합 아키텍처(ISA)를 구현하는 마이크로프로세서입니다.주로 Sun Microsystems microSPARC-II 기반의 SPARCstation 5 워크스테이션을 업그레이드하기 위해 개발된 로우엔드 마이크로프로세서입니다.1996년 9월 30일 도입되었으며 170MHz 버전은 1,000개 [1]수량으로 499달러입니다.TurboSPARC는 1997년 말 UltraSPARC IIi에 의해 보급형 SPARC 시장에서 대부분 성공을 거뒀지만 여전히 판매되고 있다.

TurboSPARC의 사용자는 Force Computers, Fujitsu, RDI Computer, Opus Systems, Tadpole Technologies, Tatung Science and Technology 및 Themis Computers였다.후지쯔는 SPARCstation 5 업그레이드 키트에서 160MHz 버전을 사용했지만 다른 회사는 워크스테이션, 노트북 및 임베디드 컴퓨터에서 170MHz 버전을 사용했습니다.

170MHz TurboSPARC의 성능은 120MHz Intel Pentium과 비슷했지만 110MHz 마이크로SPARC-II와 비교하면 정수 성능은 2배, 부동 소수점 성능은 1.5배였습니다.

묘사

TurboSPARC는 단순한 스칼라 순서대로 설계되어 있습니다.가져오기 단계에서 16KB의 직접 매핑된 명령 캐시에서 두 개의 명령을 가져왔습니다.디코딩 단계 동안 하나의 명령이 디코딩되고 해당 오퍼랜드가 레지스터 파일에서 읽힙니다.사형 집행은 3단계에서 시작되었다.TurboSPARC에는 정수 유닛과 부동소수점 유닛이 있습니다.곱셈 및 나누기를 제외한 대부분의 정수 산술 명령에는 단일 주기 지연 시간이 있습니다.곱셈 및 나누기는 FPU에 의해 실행되었습니다. 곱셈의 지연 시간은 7사이클이고 나누기의 지연 시간은 8~33사이클입니다.divide 및 square-root를 제외한 대부분의 부동 소수점 산술 명령에는 4사이클 지연이 있습니다.

메모리 액세스는 스테이지 4중에 행해집니다.TurboSPARC에는 16KB의 데이터 캐시가 있습니다.캐시는 직접 매핑되며 라이트백 쓰기 정책을 사용합니다.데이터 캐시 히트가 발생하면 데이터는 동일한 사이클로 반환되며 5단계에서 오류를 확인합니다.6단계 동안 정수 결과 및 부하가 레지스터 파일에 기록됩니다.더 많은 사이클이 걸리는 부동소수점 명령은 7단계에서 완료되고 8단계에서 부동소수점 레지스터 파일에 작성된다.

TurboSPARC에는 L2 캐시, 메모리, AFX 인터페이스 및 SBus 인터페이스용 컨트롤러가 내장되어 있습니다.256KB, 512KB 또는 1MB의 외부 L2 캐시가 지원되었습니다.캐시는 내부 클럭 주파수의 절반 또는 3분의 1로 동작했습니다.각각 85 또는 56.67MHz는 170MHz입니다.직접 매핑되고 32바이트의 회선 크기를 가지며 쓰기 정책을 사용했습니다.패리티로 보호되었습니다.캐시는 12 ns 파이프라인 버스트 스태틱랜덤 액세스 메모리(PBSRAM)에서 구축되었습니다.메모리 컨트롤러는 8 ~256 MB의 Fast Page Mode(FPM) DRAM을 8개의 뱅크에서 지원했습니다.L2 캐시와 메모리는 72비트의 와이드 버스인 시스템버스를 사용하여 액세스했습니다.이 중 64비트는 데이터용입니다.

AFX 인터페이스를 사용하면, AFX 그래픽 카드가 메모리에 직접 액세스 할 수 있습니다.캐시 및 메모리 컨트롤러와 동일한 데이터 버스를 공유하지만 자체 제어선을 사용합니다.SBus 컨트롤러에는 독자적인 16 엔트리 입력/출력 변환 룩사이드 버퍼가 있습니다.TurboSPARC는 16.67~25MHz의 SBus 주파수를 지원했습니다.TurboSPARC는 멀티프로세서를 지원하지 않았습니다.

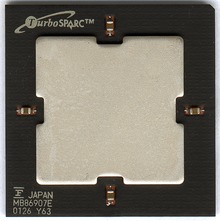

TurboSPARC는 300만 개의 트랜지스터를 포함했으며 다이 면적 132.25mm에2 [2]대해 11.5x11.5mm로 측정되었습니다.Fujitsu는 CS-60ALE 공정에서 0.35µm의 4레벨 금속상보금속산화물반도체([2]CMOS) 공정으로 제작했습니다.TurboSPARC는 416 볼 플라스틱 볼 그리드 어레이(PBGA)로 패키지화되었습니다.3.3V 전원장치를 사용했으며 최대 9W의 전력 소모가 있었습니다.

메모들

- ^ 후지쯔 마이크로일렉트로닉스, 주식회사, 후지쯔 마이크로일렉트로닉스의 새로운 TurboSPARC 프로세서가 로우엔드, 미드레인지 워크스테이션의 새로운 퍼포먼스 레벨을 확립.

- ^ a b Gwennap, "TurboSPARC는 로우엔드 업그레이드를 제공합니다", 페이지 16.

레퍼런스

- Fujitsu Microelectronics, Inc. (30 September 1996). Fujitsu Microelectronics' New TurboSPARC Processor Sets New Performance Level For Low-End, Mid-Range Workstations. Press release.

- Gwennap, Linley (18 November 1996). "TurboSPARC Offers Low-End Upgrade". Microprocessor Report, pp. 14–16.