시간/디지털 변환기

Time-to-digital converter전자 계측 및 신호 처리에서 Time-to-Digital Converter(TDC; 시간/디지털 변환기)는 이벤트를 인식하고 이벤트가 발생한 시간을 디지털로 표현하기 위한 장치입니다.예를 들어, TDC는 각 착신 펄스의 도달 시간을 출력할 수 있습니다.일부 응용 프로그램에서는 절대 시간 개념이 아닌 두 이벤트 간의 시간 간격을 측정하려고 합니다.

전자제품에서 Time-to-Digital Converters(TDC; 시간 디지털 변환기) 또는 시간 디지타이저는 시간 간격을 측정하고 이를 디지털(이진수) 출력으로 변환하는 데 일반적으로 사용되는 장치입니다.경우에 따라서는, TDC 를 Time Counter(TCS; 타임 카운터)라고도 부릅니다.

TDC는 두 신호 펄스(시작 및 정지 펄스) 사이의 시간 간격을 결정하는 데 사용됩니다.신호 펄스의 상승 또는 하강 에지가 설정된 임계값을 초과하면 측정이 시작되고 중지됩니다.이 패턴은 원자 및 고에너지 물리학에서의 비행 시간 및 수명 측정, 레이저 범위 측정 및 집적회로 테스트와 고속 데이터 [1]전송과 관련된 전자 연구와 같은 많은 물리적 실험에서 볼 수 있습니다.

어플

TDC는 고에너지 물리학 실험과 같이 측정 이벤트가 자주 발생하지 않는 애플리케이션에서 사용되며, 대부분의 검출기의 데이터 채널 수는 전자, 광자 및 이온과 같은 입자에 의해 각 채널이 간헐적으로 들뜨도록 보장합니다.

거친 측정

필요한 시간 분해능이 높지 않은 경우 카운터를 사용하여 변환할 수 있습니다.

기본 카운터

가장 간단한 구현에서 TDC는 클럭 사이클마다 증가하는 고주파 카운터입니다.카운터의 현재 내용은 현재 시간을 나타냅니다.이벤트가 발생하면 카운터 값이 출력 레지스터에 캡처됩니다.

이 방법에서는 측정이 클럭 사이클의 정수이기 때문에 측정이 클럭 주기로 양자화됩니다.해상도를 높이려면 더 빠른 클럭이 필요합니다.측정의 정확도는 클럭 주파수의 안정성에 따라 달라집니다.

일반적으로 TDC는 장기적인 안정성을 위해 수정 오실레이터 기준 주파수를 사용합니다.고안정성 결정 발진기는 일반적으로 10MHz(또는 100ns 분해능)[2]와 같은 상대 저주파수입니다.분해능을 높이기 위해 위상 잠금 루프 주파수 승수를 사용하여 더 빠른 클럭을 생성할 수 있습니다.예를 들어 수정 기준 오실레이터에 100을 곱하여 1GHz(1ns 분해능)의 클럭 속도를 얻을 수 있습니다.

카운터 테크놀로지

클럭 레이트가 높으면 카운터에 설계상의 제약이 가중됩니다.클럭 기간이 짧으면 카운트를 갱신하기 어렵습니다.예를 들어 바이너리 카운터는 기본적으로 이전 카운터 값에 추가되기 때문에 패스트캐리 아키텍처가 필요합니다.솔루션은 하이브리드 카운터 아키텍처를 사용하고 있습니다.예를 들어 Johnson 카운터는 고속 비바이너리 카운터입니다.하위 카운트를 매우 빠르게 카운트하는 데 사용할 수 있습니다. 더 일반적인 이진 카운터를 사용하여 상위 카운트를 누적할 수 있습니다.패스트 카운터는 프리스케일러라고 불리기도 합니다.

CMOS 기술로 제작된 카운터의 속도는 게이트와 채널 사이의 캐패시턴스 및 채널과 신호 트레이스의 저항에 의해 제한됩니다.양쪽의 곱은 컷오프 주파수입니다.현대 칩 기술은 여러 개의 금속 층을 허용하므로 다수의 권선이 있는 코일을 칩에 삽입할 수 있습니다.이를 통해 설계자는 원래 트랜지스터의 [citation needed]컷오프 주파수보다 높은 특정 주파수에 대해 장치를 피크할 수 있습니다.

Johnson 카운터의 피크 변형은 서브 사이클 분해능을 실현하는 이동파 카운터입니다.서브 사이클 분해능을 실현하는 다른 방법으로는 아날로그/디지털 변환기 및 버니어 Johnson [citation needed]카운터가 있습니다.

시간 간격 측정

대부분의 경우 사용자는 이벤트가 발생하는 임의의 시간을 캡처하는 것이 아니라 시작 이벤트와 중지 이벤트 사이의 시간 간격인 시간 간격을 측정합니다.

이는 시작 및 중지 이벤트의 임의 시간을 측정하고 차감하여 수행할 수 있습니다.측정값은 두 카운트만큼 차이가 날 수 있습니다.

카운터가 시작 이벤트까지 0으로 유지되고 간격 동안 카운트된 다음 중지 이벤트 후에 카운트를 중지하면 감산을 피할 수 있습니다.

조잡한 카운터는 안정적인 f [1]에서 생성된 신호를 사용하여 기준 클럭을 기반으로 합니다.시작 신호가 감지되면 카운터는 클럭 신호 카운트를 시작하고 정지 신호가 감지된 후 카운트를 종료합니다.시작과 정지 사이의 시간 T T는 다음과 같습니다.

{\ n은 수이고 0 / {\}= 은 기준 클럭의 주기입니다.

통계 카운터

시작, 정지 및 클럭 신호는 비동기적이므로 이후 2개의 클럭 펄스 간에 시작 및 정지 신호 시간의 균일한 확률 분포가 있습니다.클럭 펄스에서 시작 및 정지 신호가 분리되는 것을 양자화 오류라고 합니다.

동일한 일정 및 비동기 시간 간격에 대한 일련의 측정의 경우 카운트된 클럭 n 1 })과 n 스타일 의 두 수를 측정합니다(그림 참조).이것들은 확률과 함께 발생합니다.

(T / )( { c ( / T _ { 0} ) c、 / { 0 } c 。다음으로 시간 간격 값을 구합니다.

위에서 설명한 평균화 방법으로 거친 카운터를 사용하여 시간 간격을 측정하는 것은 p p q의 을 결정하는 데 많은 반복이 필요하기 때문에 상대적으로 시간이 걸립니다.나중에 설명한 다른 방법에 비해 거친 카운터는 매우 제한적입니다.분해능(1GHz 기준 클럭의 경우 1ns)이지만 이론적으로 무제한인 측정 범위를 만족합니다.

미세 측정

이전 섹션의 거친 카운터와는 달리,[1] 정밀도는 훨씬 높지만 측정 범위는 훨씬 작은 미세 측정 방법이 여기에 제시되어 있습니다.시간 간격 연장 또는 이중 변환과 같은 아날로그 방법 및 탭된 지연 라인 및 버니어 방법과 같은 디지털 방법을 검토 중입니다.아날로그 방법은 여전히 더 나은 정확도를 얻지만, 집적회로 기술의 유연성과 온도 변화와 같은 외부 섭동에 대한 견고성 때문에 디지털 시간 간격 측정이 선호된다.

카운터 실장의 정확도는 클럭 주파수에 의해 제한됩니다.시간을 전체 카운트로 측정할 경우 분해능은 클럭 주기로 제한됩니다.예를 들어 10MHz 클럭의 분해능은 100ns입니다.클럭 주기보다 정밀하게 분해능을 얻기 위해 시간 보간 [3]회로가 있습니다.이들 회로는 클럭 주기의 분수, 즉 클럭이벤트와 측정되는 이벤트 사이의 시간을 측정합니다.보간회로는 기능을 수행하는 데 상당한 시간이 필요한 경우가 많기 때문에 TDC는 다음 측정 전에 조용한 간격이 필요합니다.

램프 보간기

클럭 레이트가 너무 높아 카운트를 할 수 없는 경우 아날로그 방식을 사용할 수 있습니다.아날로그 방법은 종종 10 ~200 [4]ns의 간격을 측정하는 데 사용됩니다.이러한 방법에서는 일반적으로 측정 [5][6][7][8]간격 동안 충전된 캐패시터를 사용합니다.처음에는 캐패시터가 0V로 방전됩니다.시작 이벤트가 발생하면 캐패시터는 정전류1 I로 충전됩니다. 정전류는 캐패시터의 전압 v를 시간에 따라 선형적으로 증가시킵니다.상승 전압을 고속 램프라고 합니다.정지 이벤트가 발생하면 충전 전류가 정지됩니다.콘덴서 v의 전압은 시간 간격 T에 정비례하며 아날로그-디지털 변환기(ADC)를 사용하여 측정할 수 있습니다.이러한 시스템의 분해능은 1~10ps [9]범위입니다.

별도의 ADC를 사용할 수 있지만 ADC 단계는 종종 인터폴레이터에 통합됩니다.두 번째 정전류2 I은 일정하지만 훨씬 느린 속도로 캐패시터를 방전하는 데 사용됩니다(느린 램프).슬로우 램프는 패스트램프의 1000분의 1이 될 수 있습니다.이 방전은 시간 [10]간격을 효과적으로 "스트레칭"합니다. 캐패시터가 0V로 방전되는 데 걸리는 시간의 1000배가 됩니다.스트레칭 간격은 카운터를 사용하여 측정할 수 있습니다.측정은 듀얼 슬로프 아날로그 컨버터와 유사합니다.

듀얼 슬로프 변환에는 오랜 시간이 걸릴 수 있습니다.상기 방식에서는 클럭틱이 1,000개 정도 됩니다.따라서 측정 빈도가 제한됩니다(데드 타임).100MHz(10ns) 클럭에서 1ps의 분해능은 10,000의 스트레치비가 필요하며 변환 시간은 150μs입니다.[10]변환시간을 단축하기 위해 인터폴레이터 회로를 잔류 인터폴레이터 [10]기술로 2회 사용할 수 있다.Fast Ramp는 처음에 위와 같이 시간을 결정하기 위해 사용됩니다.슬로우 램프는 100분의 1에 불과하다.슬로우 램프는 클럭 기간 중 어느 시점에 제로를 통과합니다.램프가 0을 넘으면 고속 램프가 다시 켜져 교차 시간(tresidual)을 측정합니다.이것에 의해, 1만분의 1로 시간을 결정할 수 있다.

보간기는 안정적인 시스템 클럭과 함께 사용되는 경우가 많습니다.시작 이벤트는 비동기이지만 중지 이벤트는 다음 [6][8]클럭입니다.편의를 위해 100ns 클럭 시간 동안 고속 램프가 정확히 1V 상승한다고 가정해 보십시오.클럭 펄스 후 67.3ns에서 시작 이벤트가 발생한다고 가정합니다. 고속 램프 인테그레이터가 트리거되어 상승하기 시작합니다.비동기 시작 이벤트도 적어도2개의 클럭펄스를 받는 싱크로나이저를 통해 라우팅 됩니다.다음 클럭 펄스에 의해 램프가 0.327V로 상승합니다. 두 번째 클럭 펄스에 의해 램프가 1.327V로 상승하고 싱크로나이저가 시동 이벤트가 발생했음을 보고합니다.고속 램프가 정지하고 저속 램프가 시작됩니다.싱크로나이저 출력을 사용하여 카운터에서 시스템 시간을 캡처할 수 있습니다.1327 클럭이 지나면 슬로 램프는 시작점으로 돌아가며 인터폴레이터는 이벤트가 싱크로나이저가 보고하기 전에 132.7ns 발생했음을 인식합니다.

인터폴레이터는 싱크로나이저의 문제가 있어 전류 스위칭이 즉시 [11]이루어지지 않기 때문에 실제로 더 많이 관여합니다.또한 인터폴레이터는 램프 높이를 클럭 [12]주기에 맞춰 보정해야 합니다.

버니어

버니어 보간기

버니어 방법이 더 [13]복잡합니다.이 방법에는 트리거 가능한[14] 오실레이터와 일치 회로가 포함됩니다.이 경우 정수 클럭 카운트가 저장되고 발진기가 기동됩니다.트리거된 오실레이터의 주파수는 클럭 오실레이터와 약간 다릅니다.인수를 위해 트리거된 오실레이터의 주기가 클럭보다 1ns 빠르다고 가정합니다.이벤트가 마지막 클럭 이후에 67ns 발생한 경우 트리거된 오실레이터 전환은 이후의 각 클럭 펄스 이후에 -1ns씩 미끄러집니다.트리거된 오실레이터는 다음 클럭 이후 66ns, 두 번째 클럭 이후 65ns가 됩니다.일치 검출기는 트리거된 발진기와 클럭 전환이 동시에 이루어지는 시기를 찾아 추가가 필요한 분수 시간을 나타냅니다.

보간기 설계는 더 관련이 있다.트리거 가능한 클럭은 클럭에 맞게 보정해야 합니다.또한 빠르고 깨끗하게 시작해야 합니다.

버니어법

Vernier 방법은 시간 연장 방법의 디지털 버전입니다.약간 분리된 발진기 2개(f1 {1}} f2 {{2만이 시작 신호와 중지 신호가 도착하면서 신호를 시작합니다.발진기 신호의 선행 에지가 일치하면 측정이 종료되고 발진기의 주기 수( n 1{} 및 2 {}})가 원래 시간 T {{ T로 이어집니다.

안정적이고 정확한 주파수의 신뢰성이 높은 오실레이터는 여전히 매우 어렵기 때문에 약간 다른 두 개의 셀 지연 시간†(\을 사용하여 두 개의 탭 지연 라인을 통해 버니어 방식을 구현합니다. 이 설정을 차등 지연 라인 또는 버니어 지연 라인이라고 합니다.

이 예에서는 시작 신호에 관련된 첫 번째 지연 회선에 지연이 인 D-flip-flops 셀이 포함되어 있습니다.이 셀은 처음에 투과로 설정되어 있습니다.이들 셀 중 하나를 통한 시작 신호의 이행 중에는 신호가 L(\만큼 지연되고 플립 플랍 상태가 투명하게 샘플링된다.정지 신호에 속하는 두 번째 지연 라인은 지연 B < L \ \_ { } < \ { L} delay propag of of with with버퍼로 구성됩니다.정지 신호는 채널을 통해 시작 신호의 지연 라인의 플립 플랍스를 래칭합니다.정지 신호가 시작 신호를 통과하는 즉시 후자는 정지되고 남은 플립 플랍은 모두 불투명 샘플링됩니다.위 발진기의 경우와 유사하게 원하는 시간 T T는 다음과 같습니다.

n개의 셀이 투과적으로 마크되어 있습니다.

탭 지연 라인

일반적으로 탭된 지연 회선에는 지연 시간이 잘 정의된 다수 포함되어 회선을 통해 전파되면 시작 신호가 지연됩니다라인 상태는 정지 신호가 도착할 때 샘플링됩니다.예를 들어 { \ tau 의 D-flip-flop 셀 회선을 사용하면 가능합니다.시작 신호는 이 투명 플립 플랍 회선을 통해 전파되며 일정 수만큼 지연됩니다.각 플립 플랍의 출력은 즉시 샘플링됩니다.정지 신호는 모든 플립 플랍을 래칭하면서 채널을 통해 전파되며 시작 신호는 더 이상 전파될 수 없습니다.이제 시작 신호와 중지 신호 사이의 시간 간격은 투명하게 샘플링된 플립 플랍 수에 비례합니다.

하이브리드 측정

카운터는 긴 간격을 측정할 수 있지만 분해능이 제한됩니다.보간기는 분해능이 높지만 긴 구간을 측정할 수는 없습니다.하이브리드 접근방식은 긴 간격과 고해상도를 [1]모두 달성할 수 있습니다.긴 간격은 카운터를 사용하여 측정할 수 있습니다.카운터 정보는 2개의 시간 보간기로 보완됩니다.하나는 시작 이벤트와 후속 클럭 이벤트 사이의 (짧은) 간격을 측정하고, 다른 하나는 정지 이벤트와 후속 클럭 이벤트 사이의 간격을 측정합니다.기본 개념에는 몇 가지 복잡한 점이 있습니다.시작 이벤트와 정지 이벤트는 비동기 이벤트이며, 둘 다 클럭 펄스에 근접하여 발생할 수 있습니다.카운터와 인터폴레이터는 시작 클럭이벤트와 종료 클럭이벤트를 일치시키는 데 동의해야 합니다.이 목적을 달성하기 위해 동기기가 사용됩니다.

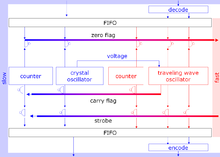

일반적인 하이브리드 방식은 너트 방식입니다.[15]이 예에서 미세 측정 회로는 싱크로나이저에 의해 감지되는 로우 카운터(Tstart, Tstop)의 시작과 정지 펄스 사이의 시간과 두 번째로 가까운 클럭 펄스를 측정합니다(그림 참조).따라서 원하는 시간 간격은

카운터 클럭 펄스의 수가 n이고0 T는 거친 카운터의 주기입니다.

역사

시간 측정은 초기부터 자연을 이해하는 데 중요한 역할을 했다.태양, 모래 또는 물로 움직이는 시계에서 시작하여 오늘날에는 가장 정밀한 세슘 공진기를 기반으로 시계를 사용할 수 있습니다.

TDC의 첫 직속 전임자는 1942년 브루노 로시에 의해 뮤온 수명을 [16]측정하기 위해 발명되었다.측정된 시간 간격 동안 지속적으로 캐패시터를 충전하는 시간-진폭 변환기로 설계되었습니다.해당 전압은 검사 중인 시간 간격에 정비례합니다.

시간을 측정 가능한 간격으로 나누는 기본 개념(예: Vernier 방법(Pierre Vernier 1584-1638) 및 시간 연장)은 여전히 최신이지만, 지난 50년 동안 구현이 많이 변경되었습니다.진공관 및 페라이트 포트 코어 변압기를 시작으로 오늘날 [17]이러한 아이디어는 상호 보완적인 금속 산화물 반도체(CMOS) 설계로 구현됩니다.

에러

- 의 정보

제시된 미세한 측정 방법에도 여전히 제거하거나 최소한 고려해야 할 오류가 있습니다.예를 들어, 시간-디지털 변환의 비선형성은 푸이소니아 분포 선원의 다수의 측정을 통해 확인할 수 있다(통계 코드 밀도 테스트).[18]균일한 분포에서 조금만 벗어나면 비선형성이 드러납니다.통계 코드 밀도 방법은 불편하게도 외부 온도 변화에 상당히 민감합니다.따라서 지연 또는 위상잠금루프(DLL 또는 PLL) 회로를 안정화하는 것이 좋습니다.

이와 유사한 방법으로 오프셋 오류(T = 0에서 0이 아닌 판독치)를 제거할 수 있습니다.

긴 시간 간격에서는 기준 클럭(지터)의 불안정성에 기인하는 에러가 큰 역할을 합니다.따라서 이러한 TDC에는 우수한 품질의 클럭이 필요합니다.

또한 강력한 추정법에 [19]의해 후처리 시 외부 노이즈원을 제거할 수 있다.

구성

TDC는 현재 물리 실험의 독립형 측정 장치 또는 PCI 카드와 같은 시스템 구성 요소로 구축되어 있습니다.이들은 이산회로 또는 집적회로 중 하나로 구성될 수 있습니다.

회로 설계는 TDC의 목적에 따라 변화합니다.이것은 데드타임이 긴 싱글샷 TDC에 매우 적합한 솔루션이 될 수도 있고, 멀티샷 TDC의 데드타임과 분해능의 균형을 맞출 수도 있습니다.

지연 발생기

Time-to-Digital 변환기는 시작 이벤트와 중지 이벤트 사이의 시간을 측정합니다.디지털-타임 변환기 또는 지연 발생기도 있습니다.지연 발생기는 숫자를 시간 지연으로 변환합니다.지연 발생기는 입력 시 시작 펄스를 받으면 지정된 지연 후 정지 펄스를 출력합니다.TDC와 지연 발생기의 아키텍처는 유사합니다.둘 다 길고 안정적인 지연에 대해 카운터를 사용합니다.둘 다 클럭 양자화 오류 문제를 고려해야 합니다.

예를 들어 Tektronix 7D11 디지털 지연은 카운터 [20]아키텍처를 사용합니다.디지털 지연은 100ns에서1초까지 100ns 단위로 설정할 수 있습니다.아날로그 회로는 0~100ns의 미세한 지연을 추가로 제공합니다.5MHz 레퍼런스 클럭은 위상 잠금 루프를 구동하여 안정적인 500MHz 클럭을 생성합니다.(미세 지연) 시작 이벤트에 의해 게이트되어 주요 양자화 오류를 결정하는 것은 이 고속 클럭입니다.패스트 클럭은 10MHz로 분할되어 메인카운터에 [21]공급됩니다.계측기 양자화 오류는 주로 500MHz 클럭(2ns 단계)에 따라 달라지지만 다른 오류도 발생합니다. 계측기는 2.2ns의 지터를 갖도록 지정됩니다.재활용 시간은 575ns입니다.

TDC가 보간법을 사용하여 1개의 클럭 주기 분해능보다 미세하게 할 수 있는 것처럼 지연 발생기도 유사한 기술을 사용할 수 있습니다.Hewlett-Packard 5359A 고해상도 시간 신시사이저는 0~160ms의 지연을 제공하며 1ns의 정밀도를 가지며 100ps의 [22]일반적인 지터를 실현합니다.이 설계에서는 200MHz에서 실행되는 트리거 위상 잠금 발진기를 사용합니다.보간은 램프, 8비트 디지털/아날로그 변환기 및 비교기로 이루어집니다.해상도는 약 45ps입니다.

시작 펄스가 수신되면 가 카운트다운하고 정지 펄스를 출력합니다.낮은 지터의 경우 동기 카운터는 최상위 비트에서 최하위 비트로 제로 플래그를 공급한 후 존슨 카운터의 출력과 결합해야 합니다.

Digital-to-Analog Converter(DAC; 디지털/아날로그 변환기)를 사용하여 서브사이클을 해결할 수 있지만 버니어 Johnson 카운터 또는 이동파 Johnson 카운터를 사용하는 것이 더 쉽습니다.

지연 발생기는 펄스 폭 변조에 사용할 수 있습니다. 예를 들어 MOSFET를 구동하여 특정 전하를 사용하여 8ns 이내에 Pockels 셀을 로드합니다.

지연 발생기의 출력은 디지털-아날로그 변환기를 게이트할 수 있으므로 가변 높이의 펄스를 생성할 수 있습니다.이를 통해 아날로그 전자제품에 필요한 낮은 수준, ECL의 경우 높은 수준, TTL의 경우 더 높은 수준에 맞출 수 있습니다.일련의 DAC가 순차적으로 게이트된 경우 전송 함수를 고려하기 위해 가변 펄스 모양이 생성될 수 있습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ a b c d e f Kalisz, Józef (February 2004), "Review of methods for time interval measurements with picosecond resolution", Metrologia, Institute of Physics Publishing, 41 (1): 17–32, Bibcode:2004Metro..41...17K, doi:10.1088/0026-1394/41/1/004

- ^ 예를 들어, Hewlett-Packard(현 애질런트) 10811 크리스털 오븐 오실레이터, http://www.hparchive.com/Manuals/HP-10811AB-Manual.pdf

- ^ 시간과 주파수 AZ, 국립 표준 기술로, 예를 들어, 100MHz은 시간축 주파수, 또한 multiplying한 것 10ns 결의안을 보며, 1ns카운터도 1GHz타임 베이스를 사용하여 건설된 적이 없게 만든다.그러나 더욱 일반적인 방법 해상도를 높이기 위해 보간을 통해 전체 주기의 숫자에 따라 제한되야 할 일이 아니다 타임 베이스 주기의 일부를 감지하는 것이다.보간법이, 그리고 심지어 20피코초 TICs 이용할 수 있다., 시간에 진입하시면서 카운터 1ns TICs하는 시키고 있다.

- ^ 칼리스 2004, 페이지 19

- ^ Reeser, Gilbert A. (May 1969), "An Electronic Counter for the 1970's" (PDF), Hewlett-Packard Journal, Hewlett-Packard, 20 (9): 9–12

- ^ a b Sasaki, Gary D.; Jensen, Ronald C. (September 1980), "Automatic Measurements with a High Performance Universal Counter" (PDF), Hewlett-Packard Journal, Hewlett-Packard, 31 (9): 21–31

- ^ Rush, Kenneth; Oldfield, Danny J. (April 1986), "A Data Acquisition System for a 1-GHz Digitizing Oscilloscope", Hewlett-Packard Journal, Hewlett-Packard, 37 (4): 4–11

- ^ a b Eskeldson, David D.; Kellum, Reginald; Whiteman, Donald A. (October 1993), "A Digitizing Oscilloscope Time Base and Trigger System Optimized for Throughput and Low Jitter", Hewlett-Packard Journal, Hewlett-Packard, 44 (5): 21–30

- ^ Kalisz 2004, 페이지 20. Kalisz는 Stanford Research Systems SR620이 이 방법을 사용한다고 말합니다.

- ^ a b c Eskeldson, Kellum & Whiteman 1993, 페이지 27은 "효과적으로 인터폴레이터는 충전 및 방전 전류의 비율에 따라 보간 또는 불확실성 간격을 확대한다"고 기술한다.

- ^ Eskeldson, Kellum & Whiteman 1993, 27페이지

- ^ Sasaki & Jensen 1980, 페이지 23은 다음과 같이 말하고 있습니다.실제로 보간기 구축에 사용되는 전류원 및 기타 회로는 온도와 시간에 따라 동작에 변화가 있을 수 있습니다.5360A의 보간기는 특수 절연 공동에 있었고 몇 가지 조정을 거쳤습니다.5335A는 온도의 영향을 받지 않고 조정이 필요 없는 자가 교정 기술을 사용합니다."

- ^ Chu, David C.; Allen, Mark S.; Foster, Allen S. (August 1978), "Universal Counter Resolves Picoseconds in Time Interval Measurements" (PDF), HP Journal, Hewlett-Packard, 29 (12): 2–11

- ^ Chu, David C. (August 1978), "The Triggered Phase-Locked Oscillator" (PDF), HP Journal, Hewlett-Packard, 29 (12): 8–9

- ^ Kalisz, J.; Pawlowski, M.; Pelka, R. (1987), "Error analysis and design of the Nutt time-interval digitiser with picosecond resolution", J. Phys. E: Sci. Instrum., 20 (11): 1330–1341, Bibcode:1987JPhE...20.1330K, doi:10.1088/0022-3735/20/11/005

- ^ "Bruno Benedetto Rossi", 조지 W. 클라크, 워싱턴 D.C. 1998, S.13

- ^ "전압 제어 발진기를 사용하는 아날로그 및 디지털 변환기의 노이즈 쉐이핑 기술", Matthew A.Z.스트레이어, 박사합성, 매사추세츠공대(2008)

- ^ Pelka, R.; Kalisz, J.; Szplet, R. (1997), "Nonlinearity correction of the integrated time-to-digital converter with direct coding", IEEE Trans. Instrumentation and Measurement, 46 (2): 449–452, doi:10.1109/19.571882

- ^ Kalisz, J.; Pawlowski, M.; Pelka, R. (March 1994), "Precision time counter for laser ranging to satellites", Rev. Sci. Instrum., 65 (3): 736–741, Bibcode:1994RScI...65..736K, doi:10.1063/1.1145094

- ^ Tektronix 7D11 Digital Delay Service Instruction Manual, Beaverton, OR: Tektronix, 1973, 070-1377-01

- ^ 10메가헤르츠는 1971년 TTL 논리가 처리할 수 있는 주파수입니다.1971년에는 고속 디지털 카운터가 드물었기 때문에 고주파 분할은 다른 기술로 처리되었습니다.첫 번째 (500MHz) 분할 스테이지에서는 5회선으로 나누기 위한 100MHz 동기 멀티비브레이터입니다.두 번째(100MHz) 단계는 이산 이미터 결합 트랜지스터로 만들어진 5링 카운터의 나눗셈입니다.마지막 단계는 플립플랍입니다.

- ^ Ferguson, Keith M.; Dickstein, Leonard R. (August 1978), "Time Synthesizer Generates Precise Pulse Widths and Time Delays for Critical Timing Applications" (PDF), HP Journal, 29 (12): 12–19

외부 링크

- US 3983481, Nutt, Ronald; Milam, Kelly & Williams, Charles W., "디지털 간격계", 1975년 8월 4일 발행, 1976년 9월 18일 발행

- US 3133189, 메릴, 배글리, 앨런 S. & 브룩스비, 메릴, "시간 간격 및 주파수 측정을 위한 전자 보간 카운터", 1960년 8월 5일 발행, 1964년 5월 12일 발행

- US 2665411, Frady, William E, Jr., 1951년 3월 15일 발행, 1954년 1월 5일 발행

- US 2665410, Burbeck, Donald W., 1951년 3월 15일 발행, 1954년 1월 5일 발행

- US 2560124, Mofenson, Jack, "Interval Measuring System", 1950년 3월 31일 발행, 1951년 7월 10일 발행

- http://www.freepatentsonline.com/8324952.html

- 진행파 CMOS

- 진행파 nFET 캐스코드

- http://www.febo.com/pages/hp5370b/

- http://www.g8wrb.org/useful-stuff/time/HP-5370B/

- http://ilrs.gsfc.nasa.gov/docs/timing/artyukh_time_interval_counter.pdf

- http://ilrs.gsfc.nasa.gov/docs/time_interval_measurements.pdf

- http://tycho.usno.navy.mil/ptti/1994/Vol%2026_22.pdf

- http://www.acam.de/fileadmin/Download/pdf/English/AN002_e.pdf

- Salvatore, Loffredo (2010), Design, construction and tests of a high resolution, high dynamic range Time to Digital Converter Universita degli studi Roma Tre, Scienze Matematichee Fische의 Scuola Dottorale

- Kalisz, Jozef; Szplet, Ryszard; Pelka, Ryszard (August 1997), "Single-Chip Interpolating Time Counter with 200-ps Resolution and 43-s Range", IEEE Transactions on Instrumentation and Measurement, IEEE, 46 (4): 851–856, doi:10.1109/19.650787, ISSN 0018-9456

- http://www.ti.com/lit/ds/symlink/tdc7200.pdf

다음과 같습니다.

다음과 같습니다.

n

n