픽셀 비주얼 코어

Pixel Visual CorePVC(Pixel Visual Core)는 Google이 [1]설계한 일련의 ARM 기반 패키지 시스템(SiP) 이미지 프로세서입니다.PVC는 모바일 디바이스와 미래의 IoT를 [2]위한 완전한 프로그램 가능한 이미지, 비전 및 AI 멀티코어 도메인 고유 아키텍처(DSA)입니다.2017년 10월 19일 선보인 구글 픽셀 2와 2 XL에 처음 등장했다.구글 픽셀 3과 3 XL에도 등장했습니다.Pixel 4부터 이 칩은 Pixel Neural Core로 대체되었습니다.

역사

구글은 이전에 퀄컴 스냅드래곤의 CPU, GPU, IPU, DSP를 구글 넥서스와 구글 픽셀 디바이스의 이미지 처리를 처리하기 위해 사용했다.컴퓨터 사진 기술의 중요성이 높아지면서 구글은 픽셀 비주얼 코어(PVC)를 개발했다.구글은 PVC가 텐서 프로세싱 유닛(TPU) 애플리케이션별 집적회로(ASIC)와 달리 완전한 프로그래밍이 가능하면서도 CPU와 GPU를 사용하는 것보다 적은 전력을 사용한다고 주장한다.실제로 기존의 모바일 디바이스는 고정기능성 화상처리 파이프라인인 화상신호처리장치(ISP)를 갖추고 있다.이와는 대조적으로 PVC에는 유연한 프로그램 가능 기능이 있으며 이미지 처리에만 국한되지 않습니다.

Google Pixel 2 및 2 XL의 PVC에는 SR3HX X726C502라는 [3]라벨이 붙어 있습니다.

Google Pixel 3 및 3 XL의 PVC에는 SR3HX X739F030이라는 라벨이 붙어 있습니다.[4]

PVC 덕분에 Pixel 2와 Pixel 3은 98과 101의 [6]모바일[5] DxOMark를 얻었습니다.후자는 싱글 렌즈 모바일 [7]DxOMark 스코어 톱으로, iPhone XR와 동률을 이뤘다.

픽셀 비주얼 코어 소프트웨어

PVC의 전형적인 화상 처리 프로그램은 할로겐화물로 기술되어 있습니다.현재는 부동소수점 연산 없이 제한된 메모리 액세스 [8]패턴으로 할라이드 프로그래밍 언어의 서브셋만 지원합니다.Halide는 사용자가 알고리즘과 그 실행 일정을 분리할 수 있는 도메인별 언어입니다.이와 같이 개발자는 대상 하드웨어 [2]아키텍처에 최적화된 프로그램을 작성할 수 있습니다.

픽셀 비주얼 코어 ISA

PVC에는 가상과 물리 두 가지 유형의 Instruction Set Architecture(ISA; 명령 세트아키텍처)가 있습니다.우선 RISC-V [2]ISA에서 영감을 얻어 고급 언어 프로그램을 가상 ISA(vISA)로 컴파일합니다.가상 ISA는 대상 하드웨어 세대에서 완전히 추상화됩니다.다음으로 vISA 프로그램은 이른바 물리 ISA(pISA)로 컴파일됩니다.이것은 VLIW ISA입니다.이 컴파일 스텝에서는 대상 하드웨어 파라미터(PE 사이즈, STP 사이즈 등)를 고려하여 메모리 이동을 명시적으로 지정합니다.vISA와 pISA의 분리를 통해 첫 번째 vISA는 크로스 아키텍처와 세대에 구애받지 않고 컴파일할 수 있으며, pISA는 오프라인 또는 JIT [8]컴파일을 통해 컴파일할 수 있습니다.

픽셀 비주얼 코어 아키텍처

Pixel Visual Core는 확장성이 뛰어난 멀티코어 에너지 효율 아키텍처로 설계되어 있습니다.코어 수는 2~[2]16개입니다.PVC의 핵심은 이미지 처리용으로 맞춤화된 프로그램 가능한 장치인 이미지 처리 장치(IPU)입니다.Pixel Visual Core 아키텍처는 SR3HX와 같은 자체 칩이거나 SOC(System on a [2]Chip)의 IP 블록으로도 설계되었습니다.

이미지 처리 장치(IPU)

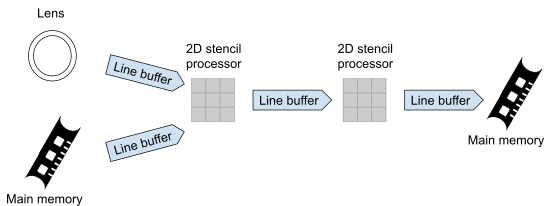

IPU 코어에는 Stencil Processor(STP; 스텐실 프로세서), Line Buffer Pool(LBP; 라인 버퍼 풀) 및 NoC가 있습니다.STP는 주로 픽셀의 작은 근방인 스텐실 계산을 수행할 수 있는 2-D SIMD 프로세서 요소(PE) 어레이를 제공합니다.STP는 수축기 어레이 및 파면 계산과 비슷하지만 소프트웨어 제어 데이터 이동이 명시적입니다.각 PE에는 2개의 16비트 연산 로직 유닛(ALU), 1개의 16비트 Multiplier-Acumulator Unit(MAC), 10개의 16비트 레지스터 및 10개의 1비트 술어 [2]레지스터가 있습니다.

Line Buffer Pool(LBP; 회선 버퍼 풀)

가장 에너지 비용이 많이 드는 동작 중 하나가 DRAM 액세스임을 고려하면 각 STP에는 데이터 인접성을 높이기 위한 임시 버퍼(LBP)가 있습니다.사용되는 LBP는 읽기 및 쓰기의 크기가 다른 2-D FIFO입니다.LBP는 단일 생산업체 멀티컨슈머 동작 모델을 사용합니다.각 LBP에는 8개의 논리 LB 메모리와 DMA 입출력 [8]동작용1개의 메모리를 탑재할 수 있습니다.메모리 시스템의 복잡성이 매우 높기 때문에 PVC 설계자는 LBP 컨트롤러를 가장 어려운 컴포넌트 [2]중 하나로 보고 있습니다.사용되는 NoC는 에너지 절약 및 파이프라인 처리 패턴 [2]보존을 위해 인접 코어와의 통신에만 사용되는 링 온 칩 네트워크입니다.

스텐실 프로세서(STP)

STP에는 2D 어레이의 PE가 있습니다.예를 들어, 풀 PE의 16x16 어레이와 심플한 PE의 4레인이 「halo」라고 불립니다.STP에는 스칼라 레인(SCL)이라고 불리는 스칼라 프로세서가 탑재되어 있습니다.스칼라 레인(SCL)은 작은 명령 메모리를 사용하여 제어 명령을 추가합니다.STP의 마지막 컴포넌트는 Sheet Generator(SHG; 시트 제너레이터)라고 불리는 로드 스토어 유닛입니다.여기서 시트는 PVC 메모리액세스 [2]유닛입니다

SR3HX 설계 개요

SR3HX PVC는 64비트 ARMv8a ARM Cortex-A53 CPU, 8x 이미지 처리 장치(IPU) 코어, 512 MB LPDDR4, MIPI, PCIe를 갖추고 있습니다.IPU 코어에는 각각 512개의 연산 로직 유닛(ALU)이 있으며, 256개의 프로세싱 엘리먼트(PE)가 16 x 16의 2차원 어레이로 배열되어 있습니다.이러한 코어는 커스텀 VLIW ISA를 실행합니다.각 처리 요소에는 2개의 16비트 ALU가 있으며 독립, 결합 및 [9]퓨즈의 3가지 방법으로 동작할 수 있습니다.SR3HX PVC는 28HPM HKMG [1]프로세스를 사용하여 TSMC에 의해 SiP로 제조됩니다.인텔과의 파트너십으로 4년 이상 설계되었습니다.(코드명:Monette Hill)[10] 구글은 SR3HX PVC가 SnapDragon [1]835보다 7~16배 에너지 효율이 높다고 주장하고 있습니다.또한 SR3HX PVC는 초당 3조 번의 작업을 수행할 수 있으므로 HDR+는 SnapDragon 835보다 [11]5배 빠르고 10분의 1 미만의 에너지로 실행할 수 있습니다.영상 처리를 위한 Halide와 기계 [11]학습을 위한 TensorFlow를 지원합니다.현재 칩은 426MHz로 동작하며, 단일 IPU는 1테라OPS [2][8]이상을 실행할 수 있습니다.

레퍼런스

- ^ a b c Cutress, Ian. "Hot Chips 2018: The Google Pixel Visual Core Live Blog (10am PT, 5pm UTC)". www.anandtech.com. Retrieved 2019-02-02.

- ^ a b c d e f g h i j Hennessy, John; Patterson, David (2017). Computer Architecture: A Quantitative Approach (Sixth ed.). Morgan Kaufmann. pp. 579–606. ISBN 978-0-12-811905-1.

- ^ "Google Pixel 2 XL Teardown". iFixit. 2017-10-19. Retrieved 2019-02-02.

- ^ "Google Pixel 3 XL Teardown". iFixit. 2018-10-16. Retrieved 2019-02-02.

- ^ "Pixel 2 DxOMark".

- ^ "Pixel 3 DxOMark".

- ^ "iPhone XR DxOMark".

- ^ a b c d "The Pixel Visual Core: Google's Fully Programmable Image, Vision and AI Processor for Mobile Devices. HotChips2018" (PDF).

- ^ "Pixel Visual Core (PVC) - Google - WikiChip". en.wikichip.org. Retrieved 2019-02-02.

- ^ "Google Partnered with Intel for the Pixel Visual Core Chip in the Pixel 2". xda-developers. 2017-10-25. Retrieved 2019-02-02.

- ^ a b "Pixel Visual Core: image processing and machine learning on Pixel 2". Google. 2017-10-17. Retrieved 2019-02-02.