플린의 분류학

Flynn's taxonomyFlyn의 분류법은 Michael J가 제안한 컴퓨터 아키텍처의 분류입니다. 플린은 1966년에[1], 1972년에 연장했습니다.[2] 분류 시스템이 고착되어 현대 프로세서와 그 기능 설계에 도구로 사용되었습니다. 멀티프로세싱 중앙처리장치(CPU)의 등장 이후, 멀티프로그래밍 컨텍스트는 분류 시스템의 확장으로 진화해 왔습니다. 1977년에 Cray-1이 발표되었기 때문에 던컨의 분류 체계에서 다루는 벡터 처리는 [3]플린의 연구에서 빠졌습니다. 플린의 두 번째 논문은 1972년에 발표되었습니다.

분류

Flyn에 의해 정의된 네 가지 초기 분류는 아키텍처에서 사용 가능한 동시 명령어(또는 제어) 스트림과 데이터 스트림의 수를 기반으로 합니다.[4] 플린은 1972년에 SIMD의 세 가지 하위 범주를 추가로 정의했습니다.[2]

| 플린의 분류학 |

|---|

| 단일 데이터 스트림 |

| 여러 데이터 스트림 |

| SIMD 서브카테고리[5] |

| 참고 항목 |

단일 명령 스트림, 단일 데이터 스트림(SISD)

명령어나 데이터 스트림에서 병렬을 사용하지 않는 순차적 컴퓨터입니다. 단일 제어 장치(CU)는 메모리에서 단일 명령 스트림(IS)을 가져옵니다. 그런 다음 CU는 적절한 제어 신호를 생성하여 단일 처리 요소(PE)가 단일 데이터 스트림(DS), 즉 한 번에 하나의 동작으로 동작하도록 지시합니다.

SISD 아키텍처의 예로는 오래된 개인용 컴퓨터(PC)와 같은 기존의 단일 프로세서 시스템(2010년까지 많은 PC에 여러 개의 코어가 있음)과 메인프레임 컴퓨터가 있습니다.

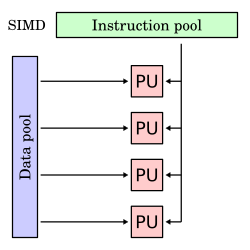

단일 명령 스트림, 다중 데이터 스트림(SIMD)

단일 명령어가 여러 다른 데이터 스트림에 동시에 적용됩니다. 명령어는 파이프라인을 통해 실행하거나 여러 기능 단위로 병렬로 실행할 수 있습니다. 플린의 1972년 논문은 SIMD를 다음 세 가지 범주로 세분화했습니다.[2]

- 어레이 프로세서 – 이들은 하나의(동일한) 명령을 받지만 각 병렬 처리 장치에는 고유의 분리되고 구별되는 메모리 및 레지스터 파일이 있습니다.

- 파이프라인 프로세서 – 이들은 하나의(동일한) 명령을 받지만 중앙 리소스에서 데이터를 읽고 각 데이터 조각을 처리한 다음 결과를 동일한 중앙 리소스에 다시 씁니다. 1972년 Flyn의 논문 그림 5에서 리소스는 메인 메모리입니다. 최신 CPU의 경우 리소스는 이제 레지스터 파일이 되었습니다.

- 연관 프로세서 – 이들은 하나의 (동일한) 지시를 받지만, 각 병렬 처리 장치에서는 실행을 수행할지 또는 건너뛸지 여부에 대한 장치 로컬 데이터를 기반으로 독립적인 결정이 내려집니다. 현대 용어에서는 이를 "전술된"(마스크된) SIMD라고 합니다.

어레이 프로세서

어레이 프로세서의 현대 용어는 "단일 명령어, 다중 스레드"(SIMT)입니다. 이것은 1972년 플린의 분류 체계에서 SIMD의 하위 범주로 구별되는 분류입니다. 자체 독립 레지스터 파일 및 메모리(캐시 및 데이터 메모리)가 있는 병렬 하위 요소로 식별할 수 있습니다. 플린의 원래 논문은 SIMT 프로세서의 두 가지 역사적인 예를 인용합니다: Solomon과 ILIAC IV.

엔비디아는 일반적으로 마케팅 자료와 기술 문서에서 이 용어를 사용하며 아키텍처의 참신성을 주장합니다.[6] Solomon은 Nvidia보다 60년 이상 앞서 있습니다.

ASP([7]Aspex Microelectronics Associative String Processor)는 마케팅 자료에서 자체를 "massive wide SIMD"로 분류했지만 비트 레벨 ALU와 비트 레벨 예측(Flyn's taxonomy: associative processing)을 가지고 있었고, 4096개의 프로세서는 각각 고유한 레지스터와 메모리(Flyn's taxonomy: array processing)를 가지고 있었습니다. 2010년에 출시된 Lineancer에는 4096개의 2비트 전용 SIMD ALU가 포함되어 있으며, 각각의 SIMD ALU는 자체 콘텐츠 주소 지정 메모리를 갖추고 있으며, 초당 8,000억 개의 명령어가 가능했습니다.[8] Aspex의 ASP 관련 어레이 SIMT 프로세서는 NVIDIA보다 20년 앞서 있습니다.[9][10]

파이프라인 프로세서

플린이 1972년 논문을 작성할 당시 많은 시스템이 파이프라인에서 읽고 쓰는 리소스로 메인 메모리를 사용하고 있었습니다. 모든 "파이프라인"이 읽고 쓰는 자원이 메인 메모리가 아닌 레지스터 파일일 때, SIMD의 현대적인 변형이 발생합니다. 예를 들면 Altivec, NEON, AVX 등이 있습니다.

이러한 유형의 레지스터 기반 SIMD에 대한 대체 이름은 "packed SIMD"[11]이고 다른 이름은 레지스터 내 SIMD(SWAR)입니다. prediction을 적용하면 연관처리가 됩니다(아래)

어소시에이션 프로세서

어소시에이티브 프로세서에 대한 현대 용어는 "predicated" (또는 masked) SIMD입니다. 예를 들어 AVX-512가 있습니다.

일부 현대 설계(특히 GPU)는 이러한 하위 범주 중 하나 이상의 특징을 갖습니다: 오늘날의 GPU는 SIMT이지만 연관성도 있습니다. 즉, SIMT 어레이의 각 처리 요소도 전제됩니다.

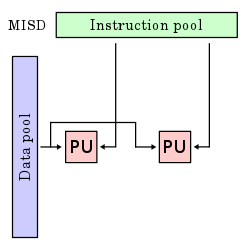

다중 명령 스트림, 단일 데이터 스트림(MISD)

여러 명령어가 하나의 데이터 스트림에서 작동합니다. 이것은 일반적으로 내결함성에 사용되는 흔하지 않은 아키텍처입니다. 이종 시스템은 동일한 데이터 스트림에서 작동하며 결과에 동의해야 합니다. 그 예로는 우주왕복선 비행 제어 컴퓨터가 있습니다.[12]

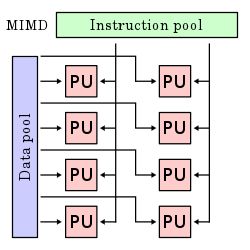

다중 명령 스트림, 다중 데이터 스트림(MIMD)

여러 자율 프로세서가 서로 다른 데이터에 대해 서로 다른 명령어를 동시에 실행합니다. MIMD 아키텍처에는 다중 코어 슈퍼스칼라 프로세서와 하나의 공유 메모리 공간 또는 분산 메모리 공간을 사용하는 분산 시스템이 포함됩니다.

분류를 비교하는 다이어그램

이 네 가지 아키텍처는 아래에 시각적으로 표시됩니다. 유니 코어 또는 멀티 코어 컴퓨터의 각 처리 장치(PU)는 다음과 같습니다.

더이상의 나눗셈

2006년[update] 기준으로 상위 10대 슈퍼컴퓨터와 대부분의 TOP500 슈퍼컴퓨터는 모두 MIMD 아키텍처를 기반으로 합니다.

비록 이것들은 플린의 작업의 일부는 아니지만, 일부는 MIMD 범주를 아래의 두 범주로 더 나누고,[13][14][15][16][17] 더 많은 세분이 고려되기도 합니다.[18]

단일 프로그램, 다중 데이터 스트림(SPMD)

여러 자율 프로세서가 서로 다른 데이터에 동일한 프로그램을 동시에 실행합니다(SIMD가 부과하는 잠금 단계가 아닌 독립적인 지점에서). 단일 프로세스, 다중 데이터라고도[17] 합니다. SPMD는 병렬 실행 모델이고 프로그램을 실행하는 여러 협력 프로세서를 가정하기 때문에 SPMD에 이 용어를 사용하는 것은 기술적으로 잘못된 것입니다. SPMD는 가장 일반적인 병렬 프로그래밍 스타일입니다.[19] SPMD 모델과 용어는 RP3팀의 Frederica Darema가 제안했습니다.[20]

여러 프로그램, 여러 데이터 스트림(MPMD)

복수의 자율 프로세서가 동시에 2개 이상의 독립적인 프로그램을 동작시키는 것을 특징으로 하는 방법. 일반적으로 이러한 시스템은 하나의 노드를 "호스트"("명시적 호스트/노드 프로그래밍 모델") 또는 "매니저"("관리자/작업자" 전략)으로 선택하고, 하나의 프로그램은 두 번째 프로그램을 모두 실행하는 다른 모든 노드에 데이터를 파밍합니다. 그런 다음 다른 노드는 결과를 관리자에게 직접 반환합니다. 그 예로는 SPU/PPU 프로세서를 탑재한 Sony PlayStation 3 게임 콘솔이 있습니다.

참고 항목

- 펑의 분류

- 헨들러의 에를랑겐 분류 체계 (ECS)

- SWAR

참고문헌

- ^ Flynn, Michael J. (December 1966). "Very high-speed computing systems". Proceedings of the IEEE. 54 (12): 1901–1909. doi:10.1109/PROC.1966.5273.

- ^ a b c Flynn, Michael J. (September 1972). "Some Computer Organizations and Their Effectiveness" (PDF). IEEE Transactions on Computers. C-21 (9): 948–960. doi:10.1109/TC.1972.5009071. S2CID 18573685.

- ^ Duncan, Ralph (February 1990). "A Survey of Parallel Computer Architectures" (PDF). Computer. 23 (2): 5–16. doi:10.1109/2.44900. S2CID 15036692. Archived (PDF) from the original on 2018-07-18. Retrieved 2018-07-18.

- ^ "Data-Level Parallelism in Vector, SIMD, and GPU Architectures" (PDF). 12 November 2013.

- ^ Flynn, Michael J. (September 1972). "Some Computer Organizations and Their Effectiveness" (PDF). IEEE Transactions on Computers. C-21 (9): 948–960. doi:10.1109/TC.1972.5009071.

- ^ "NVIDIA's Next Generation CUDA Compute Architecture: Fermi" (PDF). Nvidia.

- ^ Lea, R. M. (1988). "ASP: A Cost-Effective Parallel Microcomputer". IEEE Micro. 8 (5): 10–29. doi:10.1109/40.87518. S2CID 25901856.

- ^ "Linedancer HD – Overview". Aspex Semiconductor. Archived from the original on 13 October 2006.

- ^ Krikelis, A. (1988). Artificial Neural Network on a Massively Parallel Associative Architecture. International Neural Network Conference. Dordrecht: Springer. doi:10.1007/978-94-009-0643-3_39. ISBN 978-94-009-0643-3.

- ^ Ódor, Géza; Krikelis, Argy; Vesztergombi, György; Rohrbach, Francois. "Effective Monte Carlo simulation on System-V massively parallel associative string processing architecture" (PDF).

- ^ Miyaoka, Y.; Choi, J.; Togawa, N.; Yanagisawa, M.; Ohtsuki, T. (2002). An algorithm of hardware unit generation for processor core synthesis with packed SIMD type instructions. Asia-Pacific Conference on Circuits and Systems. pp. 171–176. doi:10.1109/APCCAS.2002.1114930. hdl:2065/10689. ISBN 0-7803-7690-0.

- ^ Spector, A.; Gifford, D. (September 1984). "The space shuttle primary computer system". Communications of the ACM. 27 (9): 872–900. doi:10.1145/358234.358246. S2CID 39724471.

- ^ "Single Program Multiple Data stream (SPMD)". Llnl.gov. Archived from the original on 2004-06-04. Retrieved 2013-12-09.

- ^ "Programming requirements for compiling, building, and running jobs". Lightning User Guide. Archived from the original on September 1, 2006.

- ^ "CTC Virtual Workshop". Web0.tc.cornell.edu. Retrieved 2013-12-09.

- ^ "NIST SP2 Primer: Distributed-memory programming". Math.nist.gov. Archived from the original on 2013-12-13. Retrieved 2013-12-09.

- ^ a b "Understanding parallel job management and message passing on IBM SP systems". Archived from the original on February 3, 2007.

- ^ "9.2 Strategies". Distributed Memory Programming. Archived from the original on September 10, 2006.

- ^ "Single program multiple data". Nist.gov. 2004-12-17. Retrieved 2013-12-09.

- ^ Darema, Frederica; George, David A.; Norton, V. Alan; Pfister, Gregory F. (1988). "A single-program-multiple-data computational model for EPEX/FORTRAN". Parallel Computing. 7 (1): 11–24. doi:10.1016/0167-8191(88)90094-4.