IBM 7030 Stretch

IBM 7030 Stretch| IBM Stretch | |

|---|---|

파리 Musée des Arts et Métier의 IBM 7030 유지보수 콘솔 | |

| 설계. | |

| 제조원 | IBM |

| 디자이너 | 진 암달 |

| 발매일 | 1961년(1961년) |

| 판매대수 | 9 |

| 가격. | 7,780,000달러 (2021년 70,550,000달러 상당) |

| 케이스 | |

| 체중 | 70,000파운드(35 쇼트톤, 32t)[1] |

| 힘 | 100 kW[1] (110 V시) |

| 시스템. | |

| 운영 체제 | MCP |

| CPU | 64비트 프로세서 |

| 기억 | 2048 킬로바이트 (262144 x 64비트)[1] |

| MIPS | 1.2 MIPS |

스트레치라고도 알려진 IBM 7030은 IBM의 첫 트랜지스터화된 슈퍼 컴퓨터였다.그것은 1961년부터 [2][3]1964년 최초의 CDC 6600이 가동되기 전까지 세계에서 가장 빠른 컴퓨터였다.

원래 Lawrence Livermore National Laboratory의 Edward Teller가 작성한 요구사항을 충족하기 위해 설계된 첫 번째 예는 1961년 Los Alamos National Laboratory에 제공되었으며, 두 번째 맞춤형 버전인 IBM 7950 Harvest는 1962년에 National Security Agency에 제공되었습니다.영국 앨더마스턴의 핵무기 연구 시설 스트레칭은 그곳의 연구원들과 AERE Harwell에 의해 많이 사용되었지만, 동적 어레이를 최초로 추가한 S2 Fortran 컴파일러가 개발된 [4][5]후에야 비로소 Chilton의 Atlas Computer Laboratory의 Feranti Atlas에 이식되었습니다.

7030은 예상보다 훨씬 느렸고 공격적인 성능 목표를 달성하지 못했습니다.IBM은 어쩔 수 없이 가격을 1,350만 달러에서 불과 778만 달러로 낮추었고, 7030은 이미 계약을 협상한 고객들을 대상으로 판매에서 철수했습니다.PC World 잡지는 Stretch를 IT [6]역사상 가장 큰 프로젝트 관리 실패 중 하나로 선정했습니다.

IBM 내부에서는 규모가 작은 Control Data Corporation에 의해 [7]가려지는 것을 받아들이기 어려워 보였습니다.프로젝트 리더인 Stephen W. Dunwell[[8]는 처음에는 "실패"[9]에 대한 자신의 역할에 대한 희생양이 되었지만 IBM System/360의 성공이 명백해지자, 그는 공식적인 사과를 받았고 1966년에 IBM [10]펠로우로 선정되었습니다.

Stretch는 자체 성능 목표를 달성하지 못했지만 1964년에 출시된 IBM System/360의 성공적인 설계 기능의 기반이 되었습니다.

개발 이력

1955년 초, 캘리포니아 대학 방사선 연구소의 에드워드 텔러 박사는 3차원 유체역학 계산을 위한 새로운 과학 컴퓨팅 시스템을 원했다.IBM과 UNIVAC는 이 새로운 시스템을 Livermore Automatic Response Calculator(LARC; Livermore Automatic Response Calculator)라고 부르기 위한 제안을 요청했습니다.IBM 임원 Cuthbert Hurd에 따르면, 이러한 시스템은 약 250만 달러의 비용이 들 것이며 1~2개의 [11]: 12 MIPS로 실행될 것이라고 합니다.배송은 계약 체결 후 2~3년 후가 될 예정이었다.

IBM에서는 John Griffith와 Gene Amdahl을 포함한 Pougkeepsie의 소규모 팀이 디자인 제안서를 작성했습니다.그들이 청혼을 마치고 막 발표하려던 순간, 랄프 팔머는 그들을 멈추고 "그것은 [11]: 12 실수입니다."라고 말했다.제안된 설계는 포인트 접점 트랜지스터 또는 표면 배리어 트랜지스터로 제작되었으며, 두 가지 모두 당시 새로 발명된 확산 트랜지스터에 [11]: 12 의해 곧 능가될 가능성이 높습니다.

IBM은 Livermore로 돌아와 계약에서 손을 뗀다고 밝히고, 대신 획기적으로 더 나은 시스템을 제안했습니다. "우리는 여러분을 위해 기계를 만드는 것이 아니라 더 나은 것을 만들고 싶습니다!정확히 얼마가 필요할지는 모르지만 100만 달러와 1년 더 걸릴 것으로 예상되며 얼마나 빨리 실행될지는 알 [11]: 13 수 없지만 초당 1000만 개의 명령을 받고 싶다고 말했다.리버모어는 감명받지 못했고, 1955년 5월 UNIVAC가 LARC 계약을 따냈다고 발표했는데, 지금은 리버모어 자동 연구 컴퓨터라고 불린다.LARC는 결국 1960년 [12]6월에 인도될 것이다.

1955년 9월 로스앨러모스 국립연구소도 LARC를 주문할 것을 우려하여 IBM은 리버모어가 거부한 디자인의 개량 버전을 기반으로 고성능 바이너리 컴퓨터에 대한 예비 제안서를 제출하였고, 이 제안서는 관심을 가지고 접수되었습니다.1956년 1월, Project Stretch가 공식적으로 시작되었습니다.1956년 11월, IBM은 "IBM 704의 최소 100배 속도"(즉, 4 MIPS)라는 공격적인 성능 목표를 가지고 계약을 따냈습니다.배달은 1960년으로 예정되어 있었다.

설계 과정에서 Stretch는 공격적인 성능 목표를 달성할 수 없었음이 분명해지면서 클럭 속도를 줄일 필요가 있었습니다. 그러나 성능 추정치는 IBM 704의 60배에서 100배에 달했습니다.1960년에 IBM 7030의 가격은 1,350만 달러로 책정되었다.1961년 실제 벤치마크에서 IBM 7030의 성능이 IBM 704의 약 30배(즉, 1.2 MIPS)에 불과하여 IBM에 상당한 당혹감을 안겨주었습니다.1961년 5월 톰 왓슨은 협상 중인 모든 7030의 가격을 778만 달러로 인하하고 추가 판매에서 제품을 즉시 철수한다고 발표했다.

부동소수점 가산시간은 1.38~1.50마이크로초, 곱셈시간은 2.48~2.70마이크로초, 분할시간은 9.00~9.90마이크로초입니다.

기술적인 영향

IBM 7030은 성공한 것으로 간주되지 않았지만, 미래의 기계에 통합된 많은 기술을 생산하여 매우 성공적이었습니다.표준 모듈러 시스템 트랜지스터 로직은 IBM 7090 라인의 과학 컴퓨터, IBM 7070 및 7080 비즈니스 컴퓨터, IBM 7040 및 IBM 1400 라인, IBM 1620 소형 과학 컴퓨터의 기초가 되었습니다. 7030은 약 170,000개의 트랜지스터를 사용했습니다.IBM 7302 Model I 코어 스토리지 장치는 IBM 7090, IBM 7070 및 IBM 7080에도 사용되었습니다.멀티프로그래밍, 메모리 보호, 일반 인터럽트, I/O용[a] 8비트 바이트는 모두 나중에 IBM System/360 컴퓨터 라인과 이후 대부분의 중앙 처리 장치(CPU)에 통합되었습니다.

Stretch가 상업적으로 실패했을 때 희생양이 된 프로젝트 매니저 Stephen Dunwell은 1964년 System/360의 경이적인 출시 성공 직후 대부분의 핵심 컨셉이 [13]Stretch에 의해 개척되었다고 지적했습니다.1966년까지 그는 사과를 받았고 IBM 펠로우로 선정되었습니다.[13] 이 펠로우에는 원하는 연구를 추진할 수 있는 자원과 권한이 주어졌습니다.

명령 파이프라인, 프리페치 및 디코딩 및 메모리 인터리빙은 IBM System/360 Model 91, 95 및 195 및 IBM 3090 시리즈와 같은 이후 슈퍼컴퓨터 설계 및 다른 제조업체의 컴퓨터에 사용되었습니다.2021년 현재[update], 이러한 기술은 인텔 Pentium과 Motorola/IBM PowerPC를 포함한 1990년대 세대를 시작으로 다양한 제조사의 많은 임베디드 마이크로프로세서 및 마이크로컨트롤러에 여전히 사용되고 있습니다.

하드웨어 구현

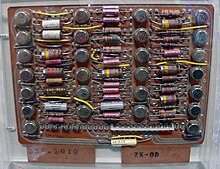

7030 CPU는 18종류의 Standard Modular System(SMS; 표준 모듈러 시스템) 카드로 이미터 결합 로직(원래는 전류 스티어링 [14]로직)을 사용합니다.그림과 같이 4,025장의 더블 카드와 18,747장의 싱글 카드를 사용하며 169,100개의 트랜지스터를 수용하여 총 21kW의 전력을 [15]: 54 필요로 합니다.차단 주파수가 100MHz 이상인 고속 NPN 및 PNP 게르마늄 드리프트 트랜지스터를 사용하며 각각 [15]: 57 최대 50mW를 사용합니다.일부 3레벨 회로는 3레벨 전압 레벨을 사용합니다.각 로직 레벨에는 약 20ns의 지연이 있습니다.크리티컬 영역에서 속도를 높이기 위해 이미터 팔로어 로직을 사용하여 지연을 약 10ns로 [15]: 55 줄입니다.

IBM 7090과 [15]: 58 동일한 코어 메모리를 사용합니다.

설치

- 1961년 4월에 Los Alamos Scientific Laboratory(LASL)가 1961년 5월에 승인되어 1971년 6월 21일까지 사용되었습니다.

- 캘리포니아 리버모어 소재 로렌스 리버모어 국립연구소는 1961년 [16]11월 인도했다.

- 미국 국가안보국은 1962년 2월 IBM 7950 하베스트 시스템의 메인 CPU로 사용되었으며, 1976년까지 사용되었던 IBM 7950 하베스트 시스템의 메인 CPU로 IBM 7955 트랙터 테이프 시스템이 교체 불가능한 마모된 캠으로 인해 문제가 발생하였습니다.

- 1962년 2월[16] 영국 올더마스턴의 핵무기 설립

- 1962년 [16]6월/7월에 배달된 미국 기상청 워싱턴 D.C.

- MITRE Corporation,[16] 1962년 12월 인도, 1971년 8월까지 사용.1972년 봄, 그것은 1982년 폐기될 때까지 물리학부에 의해 사용되었던 브리검 영 대학에 팔렸다.

- 1962년 [16]9월/10월에 인도된 미 해군 달그렌 해군 시험장.

- 1963년 [16]11월 배달된 프랑스 레네르기 아토미크 위원회.

- IBM.

Lawrence Livermore Laboratory의 IBM 7030(핵심 메모리 제외)과 MITRE Corporation/Bridham Young University IBM 7030은 현재 캘리포니아 마운틴 뷰의 컴퓨터 역사 박물관 컬렉션에 있습니다.

아키텍처

data 형식

- 고정 소수점 숫자는 길이가 가변적이며 이진수(1~64비트) 또는 10진수(1~16자리)로 저장되며 부호 없는 형식 또는 부호/크기 형식으로 저장됩니다.10진수 형식에서 숫자는 가변 길이 바이트(4~8비트)입니다.

- 부동소수점 번호에는 부호/규모 형식의 1비트 지수 플래그, 10비트 지수, 1비트 지수 기호, 48비트 크기 및 4비트 기호 바이트가 있습니다.

- 영숫자는 가변 길이이며 8비트 이하의 문자 코드를 사용할 수 있습니다.

- 바이트는 가변 길이(1~8비트)[17]입니다.

명령 형식

명령어는 32비트 또는 64비트 중 하나입니다.

레지스터

레지스터는 [18]그림과 같이 메모리의 처음 32개의 주소를 오버레이합니다.

| ! 주소 | 니모닉 | 등록하세요 | 저장 위치: |

|---|---|---|---|

| 0 | Z달러 | 64비트 제로: 항상 0으로 읽혀지며 쓰기로 변경할 수 없습니다. | 메인 코어 스토리지 |

| 1 | IT비용 | 인터벌 타이머(비트0..18): 1024Hz에서 감소, 약 8.5분마다 재활용, 0에서 인디케이터 레지스터의 "시간 신호 표시기"가 켜집니다. | 인덱스 코어 스토리지 |

| $TC | 36비트 타임클럭(비트 28..63): 1,024Hz 틱의 카운트, 비트 38..초당 63회 증가하여 ~180일마다 재활용됩니다. | ||

| 2 | $IA | 18비트 인터럽트 어드레스 | 메인 코어 스토리지 |

| 3 | 유비 | 18 비트 상한 주소(비트 0 ~17) | 트랜지스터 레지스터 |

| $LB | 18비트 하부 경계 주소(비트 32~49) | ||

| 1비트 경계제어(비트57) : 경계주소 내 또는 외부 주소 보호 여부를 결정합니다. | |||

| 4 | 64비트 유지 보수 비트: 유지 보수에만 사용 | 메인 코어 스토리지 | |

| 5 | $CA | 채널 주소(비트12..18): 읽기 전용, I/O 프로세서인 "Exchange"에 의해 설정됨 | 트랜지스터 레지스터 |

| 6 | CPUus | 기타 CPU 비트(비트 0..)18): 최대 20개의 CPU로 구성된 클러스터의 시그널링 메커니즘 | 트랜지스터 레지스터 |

| 7 | LZC달러 | 왼쪽 0이 카운트됩니다(비트 17..23): 접속 결과 또는 부동소수점 연산의 선행 제로 비트 수 | 트랜지스터 레지스터 |

| $AOC | all-one 카운트(비트 44..50): 접속 결과 또는 10진수 배수 또는 나눗셈으로 설정된 비트 수 | ||

| 8 | L달러 | 128비트 어큐뮬레이터의 왼쪽 절반 | 트랜지스터 레지스터 |

| 9 | R달러 | 128비트 어큐뮬레이터의 오른쪽 절반 | |

| 10 | SB달러 | 어큐뮬레이터 부호 바이트(비트 0.7) | |

| 11 | $IND | 인디케이터 레지스터(비트 0..19) | 트랜지스터 레지스터 |

| 12 | 마스크 | 64비트 마스크 레지스터: 비트 0..19는 항상 1, 비트는 20..쓰기 가능 47비트 48비트..63 항상 0 | 트랜지스터 레지스터 |

| 13 | $RM | 64비트 나머지 레지스터: 정수와 부동소수점 나누기 명령만으로 설정 | 메인 코어 스토리지 |

| 14 | 피트 | 64비트 팩터 레지스터: "부하 팩터" 명령에 의해서만 변경됨 | 메인 코어 스토리지 |

| 15 | $TR | 64비트 트랜짓 레지스터 | 메인 코어 스토리지 |

| 16 ... 31 | X0달러 ... 15달러 | 64비트 인덱스 레지스터(표준) | 인덱스 코어 스토리지 |

축척기 및 인덱스 레지스터는 부호 및 규모 형식으로 작동합니다.

기억

메인 메모리는 16K~256K 64비트 바이너리 워드(16K 뱅크)입니다.

메모리는 작동 특성을 안정시키기 위해 침지식 오일 가열/냉각되었습니다.

소프트웨어

「 」를 참조해 주세요.

메모들

레퍼런스

- ^ a b c BRL 보고서 1961

- ^ "Seymour Cray가 설계한 CDC 6600은 당대 두 번째로 빠른 기계인 IBM 7030 Stretch보다 거의 3배 더 빨랐습니다."Making a World of Difference: Engineering Ideas into Reality. National Academy of Engineering. 2014. ISBN 978-0309312653.

- ^ 1964년 Cray의 CDC 6600은 Stretch를 제치고 지구상에서 가장 빠른 컴퓨터가 되었습니다.

- ^ "Some Early UK FORTRAN Compilers".

- ^ "HARTRAN Overview".

- ^ Widman, Jake (October 9, 2008). "Lessons Learned: IT's Biggest Project Failures". PCWorld. Retrieved October 23, 2012.

- ^ 유명한 "Janitor" 메모에서 알 수 있듯이 IBM CEO T. J. Watson Jr는 ""Watson Jr. memo about CDC 6600". August 28, 1963.왜 우리가 업계 주도권을 잃었는가?"를 "관리인을 포함한 34명"에게 물었습니다.

- ^ "IBM Archives: Stephen W. Dunwell". IBM.

- ^ "스트래치는 상업적으로 실패한 것으로 간주되었고 던웰은 ...에 보내졌습니다."

- ^ " 그가 원하는 모든 연구를 추구할 것입니다."

- ^ a b c d Bob Evans (Summer 1984). "IBM System/360". The Computer Museum Report. pp. 8–18.

- ^ Charles Cole. "The Remington Rand Univac LARC".

- ^ a b Simmons, William W.; Elsberry, Richard B. (1988), Inside IBM: the Watson years (a personal memoir), Pennsylvania, USA: Dorrance, p. 160, ISBN 978-0805931167. The memoir of a senior IBM executive, giving his recollections of his and IBM's experience from World War II into the 1970s.

{{citation}}: CS1 maint : postscript (링크). - ^ Rymaszewski, E. J.; et al. (1981). "Semiconductor Logic Technology in IBM". IBM Journal of Research and Development. 25 (5): 607–608. doi:10.1147/rd.255.0603. ISSN 0018-8646.

- ^ a b c d Erich Bloch (1959). The Engineering Design of the Stretch Computer (PDF). Eastern Joint Computer Conference.

- ^ a b c d e f "TIMELINE OF THE IBM STRETCH/HARVEST ERA (1956-1961)". Retrieved June 13, 2021.

- ^ Mark Smotherman (July 2010). "IBM Stretch (7030) — Aggressive Uniprocessor Parallelism". clemson.edu. Retrieved 2013-12-07.

- ^ "IBM 7030 Data Processing System Reference Manual" (PDF). bitsavers.org. IBM. 1961. p. 34..38. Retrieved 2015-05-05.

- ^ Roger B. Lazarus (1978). Computing at LASL in the 1940s and 1950s. United States Department of Energy. pp. 14–15.

- ^ "The IBM 7030 FORTRAN System" (PDF). Computer History Museum. IBM Stretch Collection: International Business Machines Corporation. 1961. p. 36. Retrieved 28 February 2015.

추가 정보

- Brooks, Frederick (2010). "Stretch-ing Is Great Exercise— It Gets You in Shape to Win". IEEE Annals of the History of Computing. 32: 4–9. doi:10.1109/MAHC.2010.26. S2CID 43480009.

외부 링크

- 미니애폴리스 미네소타 대학 진 아마달 찰스 배비지 연구소 구술 역사 인터뷰Amdahl은 STARTH, IBM 701, 701A 및 IBM 704를 포함한 IBM용 여러 컴퓨터 설계에서 자신의 역할에 대해 설명합니다.그는 나다니엘 로체스터와 함께 자신의 작업 및 컴퓨터 설계 프로세스에 대한 IBM의 관리에 대해 논의합니다.

- IBM Stretch Collections @ Computer History Museum

- 7030 데이터 처리 시스템(IBM 아카이브)

- IBM Stretch(IBM 7030 데이터 처리 시스템이라고도 함)

- IBM Stretch의 조직 개요

- IBM Stretch에 대한 BRL 보고서

- 컴퓨터 시스템 계획– Project Stretch, 1962년 책.

- IBM 7030 문서(Bitsavers.org) (PDF 파일)