버퍼증폭기

Buffer amplifier

버퍼 증폭기(Buffer amplifier)는 한 회로에서 다른 회로로 전기 임피던스 변환을 제공하는 증폭기로, 첫 번째 회로의 신호 소스가 두 번째 회로의 전기 부하에 영향을 받는 것을 방지하기 위한 목적입니다. 버퍼는 전압 버퍼에 더 낮은 출력 임피던스를 제공하거나 전류 버퍼에 더 높은 출력 임피던스를 제공함으로써 비이상적인 소스를 더 이상적인 소스로 바꿉니다. 따라서 이 신호는 부하 전류로부터 '완충'됩니다.

전압 버퍼

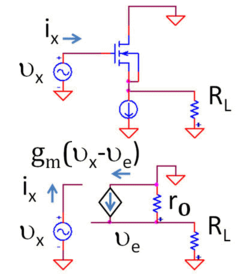

전압 버퍼 증폭기(voltage buffer amplifier)는 제1 회로의 출력 임피던스가 높은 전압 신호를 제2 회로의 출력 임피던스가 낮은 동일한 전압으로 변환하는 데 사용됩니다. 개재된 버퍼 증폭기는 전압 버퍼가 없으면 제2 회로의 전압이 제1 회로의 출력 임피던스에 의해 영향을 받기 때문에(제2 회로의 입력 임피던스보다 크기 때문에) 제2 회로가 제1 회로를 수용할 수 없고 원하는 동작을 방해하는 것을 방지합니다. 이상적인 전압 버퍼(그림 1 상단)에서 입력 임피던스는 무한대이고 출력 임피던스는 0입니다. 이상적인 버퍼의 다른 특성은: 신호 진폭에 관계없이 완벽한 선형성과 입력 신호의 속도에 관계없이 즉각적인 출력 응답입니다.

전압이 변하지 않고 전달되는 경우(전압 이득 A는v 1), 앰프는 입력 전압을 추종하거나 추적하기 때문에 전압 추종기라고도 하는 단일 이득 버퍼입니다. 전압 버퍼 증폭기의 전압 이득은 (대략적으로) 통일성일 수 있지만, 일반적으로 상당한 전류 이득과 따라서 전력 이득을 제공합니다. 그러나 전압 이득을 언급하면 이득이 1(또는 동등한 0dB)이라고 말하는 것이 일반적입니다.

예를 들어 저항 부하 R을L 구동하는 Thevenin 소스(전압 VA, 직렬 저항A R)를 생각해 보십시오. 전압 분배("로딩"이라고도 함)로 인해 부하를 가로지르는 전압은 VL RA/RL + R에A 불과합니다. 그러나 Thevenin 소스가 그림 1과 같은 단일성 이득 버퍼를 구동하면(위, 단일성 이득 포함) 증폭기에 입력되는 전압은 V이며A 증폭기 입력 저항이 무한하므로 전압 분배가 없습니다. 출력 시 종속 전압 소스는 전압 AV = V를 부하에 전달합니다. 버퍼의 출력 저항이 0이므로 전압 분배 없이도 다시 전압을 분배합니다. 결합된 원래 Thevenin 소스와 버퍼의 Thevenin 등가 회로는 Thevenin 저항이 0인 이상적인 전압 소스 V입니다A.

전류 버퍼

일반적으로 전류 버퍼 증폭기는 제1 회로의 출력 임피던스가 낮은 전류 신호를 제2 회로의 임피던스가 높은 동일한 전류로 변환하는 데 사용됩니다.[1] 개재된 버퍼 증폭기는 제2 회로가 제1 회로의 전류를 수용 불가능하게 로딩하고 원하는 동작을 방해하는 것을 방지합니다. 이상적인 전류 버퍼(그림 1 하단)에서 출력 임피던스는 무한대(이상적인 전류원)이고 입력 임피던스는 0(단락)입니다. 다시 말하지만, 이상적인 버퍼의 다른 특성은 다음과 같습니다: 신호 진폭에 관계없이 완벽한 선형성과 입력 신호의 속도에 관계없이 즉각적인 출력 응답입니다.

전류 버퍼의 경우 전류가 변하지 않고 전달되는 경우(전류 이득i β가 1), 증폭기는 다시 단일 이득 버퍼가 되며, 이는 출력 전류가 입력 전류를 따르거나 추적하기 때문에 전류 팔로워라고 합니다.

예를 들어 저항 부하 R을L 구동하는 Norton 소스(전류A I, 병렬 저항A R)를 고려합니다. 전류 분배("로딩"이라고도 함) 때문에 부하에 전달되는 전류는 IRAA/RL + R뿐입니다A. 그러나 Norton 소스가 그림 1과 같은 단일성 이득 버퍼를 구동하는 경우(아래쪽, 단일성 이득 포함), 증폭기에 입력되는 전류는 I이며 증폭기A 입력 저항이 0이므로 전류 분배가 없습니다. 출력 시 종속 전류원은 전류 β I = I를 부하에 전달합니다. 버퍼의 출력 저항은 무한하기 때문에 전류 분할 없이 다시 전류를 공급합니다. 결합된 원래 노튼 소스와 버퍼의 노튼 등가 회로는 무한한 노튼 저항을 가진 이상적인 전류원 I입니다A.

전압 버퍼 예제

Op-amp 구현

단일 이득 버퍼 증폭기는 op-amp의 출력을 반전 입력에 연결하고 신호 소스를 비반전 입력에 연결하는 것만으로 전체 직렬 음의 피드백(도 2)을 적용하여 구성될 수 있습니다(도 3). 여기서 통일성 이득은 1(즉, 0dB)의 전압 이득을 의미하지만 상당한 전류 이득이 예상됩니다. 이 구성에서는 전체 출력 전압(그림 2의 β = 1)이 반전 입력으로 피드백됩니다. 비반전 입력 전압과 반전 입력 전압의 차이는 op-amp에 의해 증폭됩니다. 이 연결은 op-amp가 출력 전압을 단순히 입력 전압과 같도록 조정하도록 강제합니다(V는out V를in 따르므로 회로 이름을 op-amp 전압 팔로워라고 합니다).

이 회로의 임피던스는 전압의 변화가 아니라 op-amp의 입력 및 출력 임피던스에서 발생합니다. op-amp의 입력 임피던스는 매우 높습니다(1M ω ~ 10T ω). 이는 op-amp의 입력이 소스를 다운로드하지 않고 소스에서 최소한의 전류만 끌어낸다는 것을 의미합니다. op-amp의 출력 임피던스가 매우 낮기 때문에 마치 완벽한 전압원인 것처럼 부하를 구동합니다. 따라서 버퍼에 대한 연결과 버퍼로부터의 연결은 모두 브리징 연결로 소스의 전력 소비, 과부하로부터의 왜곡, 크로스토크 및 기타 전자파 간섭을 감소시킵니다.

단일 트랜지스터 회로

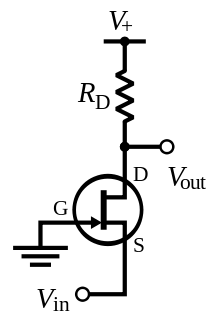

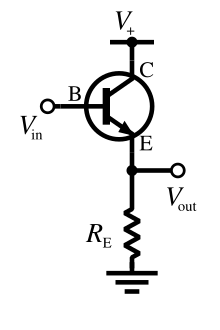

다른 유니티 게인 버퍼 증폭기는 공통-콜렉터 구성의 바이폴라 접합 트랜지스터(에미터 전압이 기본 전압을 따르므로 에미터 팔로워라고 함)를 포함합니다. 또는 출력 전압이 입력 전압을 따르므로 전압 팔로워; 공통 drain 구성의 전계 효과 트랜지스터(소스 전압이 게이트 전압을 따르므로 소스 팔로워라고 함). 출력 전압이 입력 전압을 따르므로 전압 팔로어(voltage follower); 또는 진공 튜브(cathode 팔로어) 또는 다른 능동 소자를 사용하는 유사한 구성. 이러한 모든 증폭기는 실제로 단일성보다 약간 적은 이득을 갖지만, 그 차이는 보통 작고 중요하지 않습니다.

바이폴라 전압 팔로어를 이용한 임피던스 변환

그림 4의 작은 신호 회로를 사용하면 회로를 들여다 볼 수 있는 임피던스는

(분석은 바이어스 전류에 대한 이러한 파라미터의 평가를 통해 gr = (I/V) (V/I) = β라는 관계를 사용합니다.) 일반적으로O r > > R인L 경우를 가정할 때, 버퍼를 들여다보는 임피던스는 버퍼가 없는L 부하 R보다 (β + 1)배 크며, 이는 β가 크기 때문에 상당합니다. 임피던스는 가해진 r에π 의해 더욱 증가하지만 종종π r < (β + 1) RL 이므로 가해진다고 해서 큰 차이는 없습니다.

MOSFET 전압 팔로어를 이용한 임피던스 변환

그림 5의 작은 신호 회로를 사용하면 MOSFET가 전류를 흘리지 않기 때문에 회로를 들여다볼 때 보이는 임피던스는 더L 이상 R이 아니라 (낮은 주파수에서) 무한대입니다.

주파수가 증가함에 따라 트랜지스터의 기생 용량이 작동하고 변환된 입력 임피던스가 주파수에 따라 떨어집니다.

단일 트랜지스터 증폭기 차트

단일 트랜지스터 증폭기의 일부 구성은 드라이버를 부하로부터 격리하기 위한 버퍼로 사용될 수 있습니다. 대부분의 디지털 애플리케이션에서는 NMOS 전압 팔로워(공통 드레인)가 선호되는 구성입니다.[dubious ] 이러한 증폭기는 입력 임피던스가 높기 때문에 디지털 시스템이 큰 전류를 공급할 필요가 없습니다.

| 증폭기형 | MOSFET(NMOS) | BJT(npn) | 메모들 |

|---|---|---|---|

| 공용 게이트/베이스 |  |  | 일반적으로 전류 버퍼링에 사용됩니다. |

| 공용배수/집수기 |  |  | 전압 이득은 전압 버퍼링에 사용되는 단일성에 가깝습니다. |

로직 버퍼 증폭기

비선형 버퍼 증폭기는 높은 전류가 필요한 디지털 회로에서 때때로 사용되며, 아마도 사용되는 로직 제품군의 일반 팬아웃보다 더 많은 게이트를 구동하거나 디스플레이 또는 긴 와이어 또는 기타 어려운 부하를 구동하기 위해 사용됩니다. 단일 패키지에는 여러 개의 이산 버퍼 증폭기가 포함되는 것이 일반적입니다. 예를 들어, 헥스 버퍼는 6개의 이산 버퍼 증폭기를[dubious ] 포함하는 단일 패키지이고, 옥탈 버퍼는 8개의 이산 버퍼 증폭기를 포함하는 단일 패키지입니다. 반전 버퍼와 비반전 버퍼는 각각 고전류 능력 단일 입력 NOR 또는 OR 게이트와 효과적으로 일치합니다.

스피커 배열 증폭기

대형 스피커 어레이를 구동하는 데 사용되는 대부분의 증폭기는, 록 콘서트에 사용되는 증폭기와 같이, 스피커들이 병렬로 연결된 저임피던스 스피커 어레이에 높은 전류를 공급할 수 있는 26~36dB의 전압 이득을 갖는 증폭기입니다.

운전수비대

구동 가드는 전압 버퍼를 활용하여 라인과 동일한 전압으로 버퍼에 의해 구동되는 실드로 라인을 둘러싸서 매우 높은 임피던스 신호 라인을 보호합니다. 버퍼의 근접 전압 일치는 실드가 고임피던스 라인으로 상당한 전류를 누출하는 것을 방지하는 한편 실드의 저임피던스는 신호 라인에 영향을 미칠 수 있는 임의의 미행 전류를 흡수할 수 있습니다.

현재 버퍼 예제

단순한 단일 이득 버퍼 증폭기에는 공통-베이스 구성의 바이폴라 접합 트랜지스터 또는 공통-게이트 구성의 MOSFET(출력 전류가 입력 전류를 따르므로 전류 팔로워라고 함)가 포함됩니다. 전류 버퍼 증폭기의 전류 이득은 (대략적으로) 통일성입니다.

단일 트랜지스터 회로

그림 6은 전류원(DC 이미터 전류의 경우 I로E 지정됨)으로 바이어스되고 다른 DC 전류원을 액티브 부하(DC 컬렉터 전류의C 경우 I로 지정됨)로 구동하는 바이폴라 전류 버퍼를 보여줍니다. 교류 입력 신호 전류 i는in 노턴 저항 R을S 갖는 교류 노턴 전류원에 의해 트랜지스터의 이미터 노드에 인가됩니다. AC 출력 전류 i는out 큰 커플링 커패시터를 통해 버퍼에 의해 전달되어 R을L 로드합니다. 이 커플링 커패시터는 관심 주파수에서 단락이 될 만큼 충분히 큽니다.

트랜지스터 출력 저항은 회로의 입력과 출력 측을 연결하기 때문에 출력에서 입력으로 역방향 전압 피드백이 발생하므로 이 회로는 일방적이지 않습니다. 또한 동일한 이유로 입력 저항은 출력 부하 저항에 따라 (약간) 달라지며, 출력 저항은 입력 드라이버 저항에 따라 크게 달라집니다. 자세한 내용은 공통 베이스 증폭기에 대한 기사를 참조하십시오.

참고 항목

참고문헌

- ^ "Lecture 20 - Transistor Amplifiers (II) - Other Amplifier Stages" (PDF).

A current buffer takes the input current which may have a relatively small Norton resistance and replicates the current at the output port, which has a high output resistance ... Input resistance is low ... Output resistance is high ... transform a current source with medium source resistance to an equal current with high source resistance