전원 2

POWER2 POWER2 MCM | |

| 일반 정보 | |

|---|---|

| 개시. | 1993 |

| 설계자 | IBM |

| 아키텍처 및 분류 | |

| 명령 집합 | 전원 ISA |

| 역사 | |

| 전임자 | 전원 1 |

| 후계자 | 전원 3 |

| POWER, PowerPC 및 Power ISA 아키텍처 |

|---|

| NXP(구 Freescale 및 Motorola) |

| IBM |

|

| IBM/닌텐도 |

| 다른. |

| 관련 링크 |

| 회색으로 취소됨, 이탤릭체로 기록됨 |

POWER2(원래 이름은 RIOS2)는 IBM이 POWER 명령어 세트 아키텍처를 구현한 프로세서입니다.POWER2는 POWER1의 후속 제품으로, IBM의 RS/6000 시스템에서 1993년 9월에 첫 선을 보였습니다.도입 당시 POWER2는 Alpha 21064를 능가하는 가장 빠른 마이크로프로세서였습니다.1993년에 알파 21064A가 도입되었을 때 POWER2는 선두를 잃고 2위가 되었습니다.IBM은 62.5MHz POWER2의 성능이 73.3SPECint92와 134.6SPECfp92라고 주장했습니다.

오픈 소스 GCC 컴파일러는 4.5 [1]릴리스에서 POWER1(RIOS) 및 POWER2(RIOS2)의 지원을 삭제했습니다.

묘사

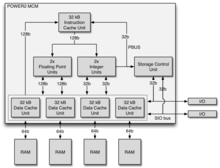

POWER1보다 향상된 기능에는 POWER 명령 세트 아키텍처(새로운 사용자 및 시스템 명령 및 기타 시스템 관련 기능으로 구성됨), 높은 클럭 레이트(55~71.5MHz), 추가 고정 소수점 단위 및 부동 소수점 단위, 더 큰 32KB 명령 캐시 및 더 큰 128KB 또는 256KB 데이터 캐시가 포함됩니다.POWER2는 데이터 캐시의 양에 따라 6개 또는 8개의 세미 커스텀 집적회로로 구성된 멀티칩 설계입니다(256KB 구성에는 8개의 칩이 필요).설계의 파티셔닝은 POWER1과 동일했습니다.명령 캐시 유닛 칩, 고정 소수점 유닛 칩, 부동 소수점 유닛 칩, 스토리지 컨트롤 유닛 칩 및 2개 또는 4개의 데이터 캐시 유닛 칩입니다.

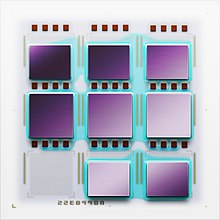

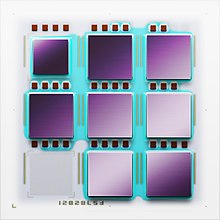

8칩 구성에는 총 2300만개의 트랜지스터와 1,215mm의2 총 다이 영역이 포함되어 있습니다.칩은 IBM이 0.72μm CMOS 공정으로 [2]제조한 것으로, 0.45μm의 유효 채널 길이와 한 층의 폴리실리콘과 네 층의 금속 [3]인터커넥트를 특징으로 합니다.칩은 64mm x 64mm 크기의 세라믹 멀티칩 모듈(MCM)에 포장되어 있습니다.

POWER2+

트랜잭션 처리에 최적화된 POWER2의 개선된 버전은 POWER2+로 1994년 5월에 소개되었습니다.트랜잭션 처리 워크로드에는 512KB, 1MB 및 2MB 용량의 L2 캐시가 추가되었습니다.이 캐시는 업계 표준 버스트 SRAM과 함께 오프패키지 방식으로 구현되었습니다.캐시는 64비트(로우엔드 시스템용) 또는 128비트 버스(하이엔드 시스템용)를 통해 POWER2+에 연결되었습니다.캐시는 직접 매핑되어 있고, 회선 크기가 128바이트이며, 쓰기 처리되었습니다.캐시 태그는 스토리지 컨트롤 유닛 칩에 포함되어 있었습니다.POWER2+는 64비트 또는 128비트 메모리 버스와 64 또는 128KB의 데이터 캐시를 갖추고 있습니다.캐시가 적기 때문에 데이터 캐시 유닛 칩이 작아지고 수정된 스토리지 제어 유닛 칩도 작아진다.6 칩 구성의 목적은 비용 절감이었습니다.따라서 칩은 MCM이 아닌 Solder Ball Connect(SBC; 솔더 볼 커넥트) 패키지로 포장됩니다.

POWER2 슈퍼칩(P2SC)

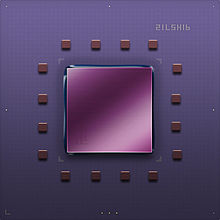

POWER2 Super Chip(P2SC)은 POWER2의 후속 제품으로 1996년 10월에[4] 출시되었습니다.IBM의 0.29μm 5층 금속 CMOS-6S 공정에서 제조된 335mm2 다이에 1500만 개의 트랜지스터를 내장한 8칩 POWER2의 단일 칩 구현입니다.첫 번째 버전은 POWER2의 71.5MHz보다 거의 2배 빠른 120MHz 또는 135MHz로 실행되었으며 메모리 및 I/O 버스는 더 높은 클럭 주파수를 지원하기 위해 절반 속도로 실행되었습니다.IBM은 이 버전의 성능이 5.5 SPECint95_base 및 14.5 SPECfp95_base라고 주장했습니다.0.25μm CMOS-6S2 프로세스로 제작된 보다 빠른 160MHz 부품이 1997년 10월 마이크로프로세서 포럼에서 발표되었습니다.

P2SC는 POWER2의 완전한 복사가 아닙니다.L1 데이터 캐시와 데이터 변환 룩사이드 버퍼(TLB) 용량은 각각 128KB와 256엔트리로 절반으로 줄었습니다.또, TLB내의 엔트리를 잠근 채로, 원래의 설계를 1개의 다이로 하기 위해서 실장하는, 거의 사용되지 않는 기능도 있습니다.

P2SC는 1998년 IBM의 RS/6000 제품군의 주력 마이크로프로세서로 POWER3에 의해 계승되었습니다.P2SC의 주목할 만한 용도는 1997년 체스에서 세계 챔피언 Garry Kasparov를 이긴 30노드 IBM Deep Blue 슈퍼컴퓨터입니다.그러나 컴퓨터의 체스 플레이 기능은 P2SC가 아닌 커스텀 VLSI 칩에서 작동하는 전문가 시스템의 결과였다.

「 」를 참조해 주세요.

메모들

- ^ "GCC 4.5 Release Series — Changes, New Features, and Fixes - GNU Project - Free Software Foundation (FSF)". gcc.gnu.org.

- ^ 구엔납 1996

- ^ 화이트 1994

- ^ Smith, Norris Parker. "IBM LAUNCHES BRAND NEW CHIP FAMILY FOR THE RS/6000 LINE". hocwire.com. Retrieved 21 December 2021.

레퍼런스

- Barreh, J. I.; Golla, R. T.; Arimilli, L. B.; Jordan, P. J. (September 1994). "POWER2 instruction cache unit". IBM Journal of Research and Development. 38 (5): 537–544. doi:10.1147/rd.385.0537.

- 볼 리처드(1997년 10월 15일).'칩빌 USA'일렉트로닉스 위클리

- DeTar, Jim(1994년 8월 22일)."IBM 상세 Power2+, DEC는 새로운 Alpha AXP를 제공합니다."전자 뉴스

- 린리 구엔납(1993년 10월 4일)."IBM, Power2로 퍼포먼스 리드 획득"마이크로프로세서 리포트

- 린리 구엔납(1996년 8월 26일)."IBM Crams POWER2를 싱글 칩에 넣습니다."마이크로프로세서 리포트

- Hicks, T. N.; Fry, R. E.; Harvey, P. E. (September 1994). "POWER2 floating-point unit: Architecture and implementation". IBM Journal of Research and Development. 38 (5): 525–536. doi:10.1147/rd.385.0525.

- 라인백, J. Robert(1993년 6월 28일)."IBM은 Unix에서 RISC Progeny를 준비합니다."전자 뉴스

- Shippy, David(1994년 8월 9일)."Power2+ 프로세서"핫칩스 6

- Shippy, D. J.; Griffith, T. W. (September 1994). "POWER2 fixed-point, data cache, and storage control units". IBM Journal of Research and Development. 38 (5): 503–524. doi:10.1147/rd.385.0503.

- Stat, Paul(1994년 1월)."Power2 Takes the Lead--현재로서는"바이트

- White, S. W.; Dhawan, S. (September 1994). "POWER2: Next generation of the RISC System/6000 family". IBM Journal of Research and Development. 38 (5): 493–502. doi:10.1147/rd.385.0493.

추가 정보

- Weiss, Shlomo; Smith, James Edward (1994). POWER and PowerPC. Morgan Kaufmann. ISBN 1558602798. - 6장에서는 POWER2 아키텍처와 프로세서에 대해 설명합니다.