인텔 8253

Intel 8253인텔 8253 및 8254는 3개의 16비트 [1]카운터를 사용하여 타이밍과 카운트 기능을 실행하는 프로그래머블인터벌타이머(PIT)입니다

825x 패밀리는 주로 인텔 8080/8085 프로세서용으로 설계되었지만 이후 x86 호환 시스템에서 사용되었습니다.825x 칩 또는 더 큰 칩에 내장된 동등한 회로는 모든 IBM PC 호환기와 Vector-06C와 같은 소련 컴퓨터에 있습니다.

PC 호환기에서는 타이머 채널0이 IRQ-0(최고 priority의 하드웨어 인터럽트)에 할당됩니다.타이머 채널1은 DRAM 리프레시에 할당됩니다(적어도 80386 이전의 초기 모델에서는).타이머 채널2는 PC 스피커에 할당되어 있습니다.

인텔 82c54 (CMOS 로직용 c)바리안트는 최대 10MHz 클럭 [1]신호를 처리합니다.

역사

8253은 1980년 인텔 "컴포넌트 데이터 카탈로그"에 기재되어 있습니다.8254는 클럭 스피드가 높은8253의 슈퍼셋으로 1982년 인텔 "컴포넌트 데이터 카탈로그"에 "잠정" 데이터 시트가 포함되어 있습니다.

8254는 HMOS에 구현되어 있으며 8253에서는 사용할 수 없는 "Read Back" 명령어가 있으며, 같은 카운터의 읽기 및 쓰기를 인터리브할 [2]수 있습니다.

최신 PC 호환성은 SoC CPU 또는 SouthBridge를 사용할 때 일반적으로 하위 호환성과 상호 [3]운용성을 위해 완전한 8254 호환성을 구현합니다.Read Back 명령어는 멀티코어 CPU 및 GPU와의 상호 운용에 필수적인 I/O 기능입니다.

변종

인텔 M8253에는 -55 °C ~ +125 °C 의 밀리터리 버전이 있습니다.또, ±10 % 5 V의 파워 [4]톨러런스도 갖추고 있습니다.이용 가능한 82C53 CMOS 버전은 Oki Electronic Industry(주)[5]에 아웃소싱되었습니다.인텔 82C54의 패키지 버전은 1986년 [6]1분기 28핀 PLCC 샘플로 제공되었습니다.

특징들

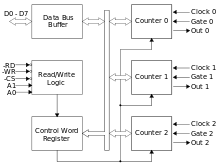

타이머에는 0 ~[7]2의 번호가 매겨진3개의 카운터가 있습니다.각 채널은 6가지 모드 중 하나로 작동하도록 프로그래밍할 수 있습니다.일단 프로그래밍되면 채널은 [1]독립적으로 작동합니다.

각 카운터에는 "CLK"(클럭 입력) 및 "GATE"라는 두 개의 입력 핀과 데이터 출력용 "OUT"이라는 한 개의 핀이 있습니다.3개의 카운터는 서로 독립된16비트 다운카운터이며 [8]CPU로 쉽게 읽을 수 있습니다.

- 데이터 버스 버퍼는 마이크로프로세서와 내부 레지스터 사이의 데이터 버스를 버퍼링하는 논리를 포함한다.8개의 입력 핀이 있으며, 보통 D7이라고 라벨이 붙어 있습니다.D0. 여기서 D7은 MSB입니다.

- 읽기/쓰기 로직에는 5개의 핀이 있습니다.이 핀은 다음과 같습니다."X"는 X가 활성 로우 신호임을 나타냅니다.

- RD: 신호 읽기

- 쓰기 신호

- CS: 칩 선택 신호

- A0, A1: 어드레스 라인

PIT의 동작모드는 상기의 하드웨어 신호를 설정함으로써 변경된다.예를 들어 제어 워드 레지스터에 쓰려면 CS=0, RD=1, WR=0, A1=A0=1을 설정해야 합니다.

- 제어 워드 레지스터에는 (마이크로프로세서를 통해) 장치로 전송되는 프로그래밍된 정보가 포함되어 있습니다.PIT의 각 채널이 논리적으로 작동하는 방식을 정의합니다.이러한 포토에의 각 액세스에는, 약 1 밀리초 걸립니다.

카운터를 초기화하려면 마이크로프로세서가 이 레지스터에 Control Word(CW; 제어워드)를 써야 합니다.읽기/쓰기 로직 블록의 핀에 적절한 값을 설정한 다음 제어 워드를 데이터/버스 버퍼 블록으로 전송하여 이를 수행할 수 있습니다.

제어 워드 레지스터에는 D7이라는 라벨이 붙은 8비트가 포함되어 있습니다.D0(D7은 MSB).복호화는 다소 복잡합니다.대부분의 값은 다음 3개의 카운터 중 하나의 파라미터를 설정합니다.

- 최상위 2비트(11비트 아님)는 명령이 적용되는 카운터 레지스터를 선택합니다.

- 다음 두 비트(00이 아닌 경우)는 카운터 레지스터에 대한 후속 읽기/쓰기 액세스에 사용할 형식을 선택합니다.이것은 보통 최하위 바이트와 최상위 바이트 간에 액세스가 번갈아 이루어지는 모드로 설정됩니다.8253과 8254의 차이점 중 하나는 읽기 및 쓰기 모두에 영향을 미치는 내부 비트가 1개 있다는 것입니다.따라서 포맷이 2바이트로 설정되어 있는 경우 lsbyte를 읽으면 다음 쓰기가 msbyte로 전송됩니다.8254는 읽기 및 쓰기에 별도의 비트를 사용했습니다.

- 다음 3비트는 카운터가 작동할 모드를 선택합니다.

- 최하위 비트는 카운터가 바이너리로 동작할지 BCD로 동작할지를 선택합니다(BCD 카운팅은 거의 사용되지 않으며 에뮬레이터 또는 사우스브리지에서 올바르게 구현되지 않을 수 있습니다).

단, 다음 두 가지 다른 형식이 있습니다.

- 지정된 타이머의 카운트를 래치합니다.다음 판독에서는 판독 시 카운터 값을 반환하는 대신 래치 명령 시 카운터 값을 반환합니다.읽기가 완료되면 나중에 읽으면 현재 카운터가 반환됩니다.latch 명령어를 사용해도 모드와 BCD 상태는 변경되지 않습니다.

- (8254 한정) 여러 타이머의 상태 및/또는 카운트를 래치합니다.그러면 비트맵을 사용하여 여러 개의 래치 명령을 동시에 실행할 수 있습니다.또한 현재 채널 구성은 카운트에 추가하여 다시 읽을 수 있습니다.

| 비트 번호/이름 | 간단한 설명 | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 SC1 | D6 SC2 | D5 RW1 | D4 RW0 | D3 M2 | D2 M1 | D1 M0 | D0 BCD | |

| 0 | 0 | 포맷 | 모드 | BCD | 카운터 0 모드 설정 | |||

| 0 | 1 | 포맷 | 모드 | BCD | 카운터 1의 모드 설정 | |||

| 1 | 0 | 포맷 | 모드 | BCD | 카운터 2 모드 설정(포트 42h) | |||

| 1 | 1 | 세어보세요 | 상황 | C2 | C1 | C0 | x | Read-back 명령어(8254 한정) |

| 계산대 | 0 | 0 | - x - | 래치 카운터 값카운터의 다음 읽기는 값의 스냅샷을 읽습니다. | ||||

| 계산대 | 0 | 1 | 모드 | BCD | 카운터 값의 낮은 바이트 읽기/쓰기만 | |||

| 계산대 | 1 | 0 | 모드 | BCD | 카운터 값의 높은 바이트 읽기/쓰기만 | |||

| 계산대 | 1 | 1 | 모드 | BCD | 2×읽기/2x낮은 바이트와 높은 바이트의 카운터 값 쓰기 | |||

| 계산대 | 포맷 | 0 | 0 | 0 | BCD | 모드 0: 단말기 카운트 시 인터럽트 | ||

| 계산대 | 포맷 | 0 | 0 | 1 | BCD | 모드 1: 하드웨어 리트리거블 원샷 | ||

| 계산대 | 포맷 | x | 1 | 0 | BCD | 모드 2: 레이트 제너레이터 | ||

| 계산대 | 포맷 | x | 1 | 1 | BCD | 모드 3: 사각파 | ||

| 계산대 | 포맷 | 1 | 0 | 0 | BCD | 모드 4: 소프트웨어 트리거 스트로브 | ||

| 계산대 | 포맷 | 1 | 0 | 1 | BCD | 모드 5: 하드웨어 트리거 스트로브(재설정 가능) | ||

| 계산대 | 포맷 | 모드 | 0 | 카운터는 16비트 바이너리 카운터(0~65535) | ||||

| 계산대 | 포맷 | 모드 | 1 | 카운터는 4자리 이진 코드 10진수 카운터(0~999)입니다. | ||||

| 1 | 1 | 세어보세요 | 상황 | C2 | C1 | C0 | x | Read-back 명령어(8254 한정) |

| 1 | 1 | 0 | 0 | C2 | C1 | C0 | x | 선택한 카운터를 다음에 읽으면 래치 상태가 다시 읽힌 다음 카운트됩니다. |

| 1 | 1 | 0 | 1 | C2 | C1 | C0 | x | 선택한 카운터를 다음에 읽으면 래치된 카운터가 다시 읽힙니다. |

| 1 | 1 | 1 | 0 | C2 | C1 | C0 | x | 선택한 카운터를 다음에 읽으면 래치 상태가 다시 읽힙니다. |

| 1 | 1 | 1 | 1 | C2 | C1 | C0 | x | 아무것도 하지 않음(일부 또는 모든 카운터에 아무것도 걸지 않음) |

| 1 | 1 | 세어보세요 | 상황 | 0 | 0 | 0 | x | 아무것도 하지 않음(카운터 없음의 래치 수 및/또는 상태) |

| 1 | 1 | 세어보세요 | 상황 | 1 | C1 | C0 | x | Read-back 명령어는 카운터 2에 적용됩니다. |

| 1 | 1 | 세어보세요 | 상황 | C2 | 1 | C0 | x | Read-back 명령어는 카운터 1에 적용됩니다. |

| 1 | 1 | 세어보세요 | 상황 | C2 | C1 | 1 | x | Read-back 명령어는 카운터 0에 적용됩니다. |

PIT를 설정할 때 마이크로프로세서는 먼저 제어 메시지를 보낸 다음 카운트 메시지를 PIT로 보냅니다.계수 프로세스는 PIT가 이러한 메시지를 수신한 후, 그리고 경우에 따라 GATE 입력 신호에서 상승 에지를 감지하면 시작됩니다.상태 바이트 형식.비트 7을 사용하면 소프트웨어가 OUT 핀의 현재 상태를 모니터링할 수 있습니다.비트 6은 카운트를 읽을 수 있는 시기를 나타냅니다.이 비트가 1일 경우 카운트 요소가 아직 로드되지 않아 프로세서에 의해 다시 읽을 수 없습니다.비트 5 ~ 0은 제어 레지스터에 마지막으로 입력된 비트와 동일합니다.

| 비트 번호/이름 | 간단한 설명 | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 산출량 상황 | D6 무효 세어보세요 | D5 RW1 | D4 RW0 | D3 M2 | D2 M1 | D1 M0 | D0 BCD | |

| 0 | 출력 핀은 0입니다. | |||||||

| 1 | 출력 핀은 1 | |||||||

| 0 | 카운터를 읽을 수 있습니다. | |||||||

| 1 | 카운터를 설정하고 있습니다. | |||||||

| 포맷 | 모드 | BCD | 제어 워드 레지스터에 정의된 카운터 모드 비트 | |||||

동작 모드

제어 워드의 D3, D2, D1 비트는 타이머의 동작 모드를 설정합니다.총 6개의 모드가 있습니다.모드 2와 3의 경우 D3 비트는 무시되므로 누락된 모드6과 7은 모드2와 3의 에일리어스입니다

모든 모드는 GATE 입력에 민감하여 GATE high가 정상 작동을 유발하지만 GATE low의 영향은 모드에 따라 달라집니다.

- Mode 0과 4: GATE가 낮을 때는 카운트가 중단되고 GATE가 높을 때는 카운트가 재개됩니다.

- Mode 1과 5: GATE의 상승 에지가 카운트를 시작합니다.GATE는 카운트에 영향을 주지 않고 낮지만 다른 상승 에지가 카운트를 처음부터 다시 시작합니다.

- 모드 2 및 3: GATE low는 클럭 펄스를 기다리지 않고 즉시 OUT High를 강제 적용하고 카운터를 재설정합니다(다음 클럭 하강 에지에서).GATE가 다시 하이 상태가 되면 카운트가 처음부터 다시 시작됩니다.

모드 0(000):터미널 카운트 시 인터럽트

모드 0은 소프트웨어 제어 하에서 정확한 시간 지연을 생성하기 위해 사용됩니다.이 모드에서는 카운터가 로드된 초기 카운트 값에서 0까지 카운트를 시작합니다.카운트 레이트는 입력 클럭 주파수와 동일합니다.

OUT 핀은 Control Word가 작성된 후 낮게 설정되며, COUNT가 프로그래밍된 후 한 클럭 사이클 후에 카운트가 시작됩니다.OUT은 카운터가 0에 도달할 때까지 낮음을 유지하며, OUT은 카운터가 새로고침되거나 Control Word가 기록될 때까지 높음으로 설정됩니다.카운터가 에워싸다0xFFFF카운트를 계속하지만 OUT 핀은 다시 변경되지 않습니다.게이트 신호는 정상 카운팅을 위해 하이 상태로 유지해야 합니다.Gate가 low가 되면 카운트가 중단되고 다시 high가 되면 카운트가 재개됩니다.

카운트 레지스터에 로드된 새 카운트의 첫 번째 바이트는 이전 카운트를 중지합니다.

모드 1(001): 프로그램 가능한 원샷

이 모드에서는 8253을 Monostable 멀티바이버레이터로 사용할 수 있습니다.GATE 입력은 트리거 입력으로 사용됩니다.

OUT은 처음에는 하이입니다.OUT은 원샷 펄스를 시작하는 트리거에 이어 클럭 펄스에서 로우로 전환되며 카운터가 0에 도달할 때까지 로우 상태를 유지합니다.OUT은 하이로 전환되며 다음 트리거 후 CLK 펄스가 발생할 때까지 하이 상태를 유지합니다.

Control Word와 초기 카운트를 작성한 후 카운터가 활성화됩니다.트리거를 실행하면 카운터가 로드되고 다음 CLK 펄스에서 OUT이 낮게 설정되므로 원샷 펄스가 시작됩니다.초기 카운트가 N이면 지속 시간 동안 원샷 펄스 N CLK 사이클이 발생합니다.

원샷은 재트리거가 가능하므로 트리거 후 N개의 CLK 펄스에 대해 OUT이 낮게 유지됩니다.카운터에 동일한 카운트를 다시 쓰지 않고도 원샷 펄스를 반복할 수 있습니다.GATE는 OUT에 영향을 주지 않습니다.원샷 펄스 중에 카운터에 새 카운트가 기록되는 경우 카운터가 다시 트리거되지 않는 한 현재 원샷은 영향을 받지 않습니다.이 경우 카운터에 새 카운트가 로드되고 새 카운트가 만료될 때까지 oneshot 펄스가 계속됩니다.

모드 2(X10): 레이트 제너레이터

이 모드에서는 디바이스는 divide-by-n 카운터로서 기능합니다.이것은 일반적으로 실시간클럭 인터럽트 생성에 사용됩니다.

다른 모드와 마찬가지로 카운트 프로세스는 COUNT 전송 후 다음 클럭사이클을 시작합니다.OUT은 카운터가 1에 도달할 때까지 하이 상태를 유지하며 1클럭 펄스에 대해 로우 상태가 됩니다.다음 사이클에서는 카운트가 새로고침되고 OUT이 다시 높아지며 전체 프로세스가 반복됩니다.

하이 펄스 사이의 시간은 카운터 레지스터의 사전 설정 카운트에 따라 달라지며, 다음 공식을 사용하여 계산됩니다.

카운터에 되는 = n f t {\ \

COUNT 레지스터의 값 범위는n\n} ~ 이며 레지스터는 0에 도달하지 않습니다.

모드 3(X11): 사각파 발생기

이 모드는 모드 2와 비슷합니다.단, 출력의 하이 클럭펄스와 로우 클럭펄스의 지속시간은 모드2와 다릅니다.

n n이 카운터에 로드된 수(COUNT 메시지)라고 하면 은 2 카운트에 대해 n2 카운트 \lfloor right에 대해서는 낮습니다.따라서 주기는 n n카운트가 .n n이 홀수일 추가 반주기는 OUT high로 소비됩니다.

모드 4(100):소프트웨어 트리거 스트로브

제어 워드와 COUNT가 로드된 후에는 카운터가 0에 도달할 때까지 출력이 높은 상태로 유지됩니다.그런 다음 카운터는 1클럭 사이클(스트로브) 동안 낮은 펄스를 생성합니다. 그런 다음 출력이 다시 높아집니다.

GATE low는 카운트를 일시 정지하고 GATE가 다시 하이로 되면 카운트가 재개됩니다.

모드 5(101):하드웨어 트리거 스트로브

이 모드는 모드 4와 비슷합니다.그러나 카운트 프로세스는 GATE 입력에 의해 트리거됩니다.

제어 워드와 COUNT를 수신하면 출력이 하이로 설정됩니다.장치가 GATE 입력에서 상승 에지를 감지하면 카운트를 시작합니다.카운터가 0에 도달하면 출력이 한 클럭 사이클 동안 로우 상태가 되고 그 후 다시 하이 상태가 되어 게이트의 다음 상승 에지에서 사이클을 반복합니다.

IBM PC 프로그래밍 팁 및 힌트

8253은 1981년 [9]출시된 이후 IBM PC 호환기에 사용되었습니다.현재 이 PIT는 x86 PC에 별도의 칩으로 포함되어 있지 않습니다.이 기능은 메인보드 칩셋의 사우스브릿지에 포함되어 있습니다.최신 칩셋에서는 이 변경은 x86 I/O 주소 공간에 있는 PIT의 레지스터에 대한 접근 속도가 현저하게 빨라지는 형태로 나타날 수 있습니다.

모든 PC 호환기는 105/88 = 1.1618MHz의 클럭 속도로 PIT를 작동시킵니다. 1⁄3 NTSColorburst 주파수이 주파수를 2로16 나누면(8253이 가능한 최대 약수) MS-DOS 및 관련 운영 체제에서 사용되는 18.2Hz 이하의 타이머 인터럽트가 발생합니다.

원래의 IBM PC에서는 Counter 0을 사용하여 타임키핑 인터럽트를 생성합니다.카운터 1(A1=0, A0=1)은 DRAM 메모리의 재충전을 트리거하는 데 사용됩니다.마지막 카운터(A1=1, A0=0)는 PC 스피커를 통해 톤을 생성하는 데 사용됩니다.

새로운 메인보드에는 ACPI(Advanced Configuration and Power Interface)를 통한 추가 카운터, 로컬 APIC(Advanced Programmable Interrupt Controller) 카운터 및 고정밀 이벤트 타이머가 포함됩니다.CPU 자체는 Time Stamp Counter(TSC; 타임스탬프 카운터) 기능도 제공합니다.

PC에서는 timer0(칩)의 주소는 포트 40h에 있습니다.43h 및 두 번째 타이머 1(칩)은 50h입니다.53시간

x86 PC에서는 많은 비디오 카드 BIOS 및 시스템 BIOS가 두 번째 카운터를 자체 사용하기 위해 재프로그래밍합니다.일반적으로 재프로그래밍은 비디오 모드 변경 시, 비디오 BIOS 실행 시, 시스템 관리 모드 및 절전 상태 변경 시, 시스템 BIOS 실행 시 발생합니다.이것에 의해, 많은 x86 시스템에서 타이머의 세컨드 카운터의 중대한 대체 사용을 방지할 수 있습니다.

x86 PC에서 시스템에 의해 사용되는 타이머는 채널0 이며 클럭은 이론적인 값인1193181.8181로 체크됩니다...Hz, 즉 시스템 클럭(14.318MHz)을 12로 나누면 발생하는 NTSC 컬러 서브캐리어 주파수의 1/3입니다.이것은 최초의 CGA PC의 홀드오버입니다.CGA PC는 1개의 석영 결정에서 필요한 주파수를 모두 추출하여 TV 출력을 실현하기 위해 이 발진기를 NTSC 컬러 서브캐리어 주파수의 여러 개로 실행해야 했습니다.

앞에서 설명한 바와 같이 채널0은 카운터로 구현됩니다.일반적으로 카운터의 초기 값은 Control에 바이트를 보낸 다음 Data I/O Port를 등록하는 방식으로 설정됩니다(포트 43h에 36h를 보낸 다음 낮은 바이트를 포트 40h에 보내고 높은 바이트에 다시 포트 40h를 보낸 값).카운터는 0까지 카운트다운한 후 하드웨어 인터럽트(IRQ 0, INT 8)를 CPU로 전송합니다.그 후 카운터는 초기값으로 리셋되어 카운트다운을 다시 시작합니다.가능한 가장 빠른 인터럽트 주파수는 0.5메가헤르츠를 조금 넘는 것입니다.가장 느린 주파수는 MS-DOS 또는 호환되는 운영체제를 실행하는 컴퓨터에서 일반적으로 사용되는 주파수로 약 18.2Hz입니다.이러한 리얼 모드 operating system에서는, BIOS 는 리얼 모드주소 0040:006c 로 수신한 INT 8 콜의 수를 축적합니다.이것은 프로그램으로 판독할 수 있습니다.

타이머가 카운트다운되면 I/O 포트를 처음에는 낮은 바이트용, 다음에는 높은 바이트용으로 두 번 읽음으로써 해당 값을 직접 읽을 수도 있습니다.단, x86 PC와 같은 프리실행 카운터 어플리케이션에서는 먼저 원하는 채널의 래치명령어를 컨트롤 레지스터에 써야 합니다.이것에 의해, 읽혀진 양쪽의 바이트가 같은 값에 속하게 됩니다.

2002년의 Microsoft 의 문서에 의하면, 「이 하드웨어에의 읽기/쓰기(8254)는 IO 포토를 개입시켜 통신할 필요가 있기 때문에, 프로그래밍에는 몇개의 사이클이 필요하기 때문에, OS 로서는 큰 코스트가 듭니다.따라서 [10]비주기적 기능은 실제로 사용되지 않습니다."

「 」를 참조해 주세요.

레퍼런스

- ^ a b c "Intel 82C54 CHMOS Programmabe Interval Timer" (PDF) (datasheet). Archived from the original (PDF) on 7 May 2016.

- ^ D.A. Godse; A.P. Godse (2007). Advanced Microprocessors. Technical Publications. p. 74. ISBN 978-81-89411-33-6.

- ^ http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf[베어 URL PDF]

- ^ Intel Corporation, "포커스 컴포넌트:군사 정보:타이머, EPROM, 무연 칩 캐리어", 솔루션, 1983년 3월/4월, 12페이지.

- ^ Intel Corporation, "NewsBit:인텔·라이센스 Oki의 CMOS 버전의 몇 가지 제품」, 솔루션, 1984년 7월/8월, 페이지 1.

- ^ Ashborn, Jim; "Advanced Packaging: A Little Goes A Long Way", Intel Corporation, Solutions, 1986년 1월 / 2월, 페이지 2

- ^ "8254/82C54: Introduction to Programmable Interval Timer". Intel Corporation. Archived from the original on 22 November 2016. Retrieved 21 August 2011.

- ^ "MSM 82c53 Datasheet" (PDF).

- ^ "Guidelines For Providing Multimedia Timer Support". 20 September 2002. Retrieved 13 October 2010.

- ^ 멀티미디어 타이머 지원 가이드라인

추가 정보

- Gilluwe, Frank Van (1997). The Undocumented PC: A Programmer's Guide to I/O, CPUs, and Fixed Memory Areas (second, illustrated ed.). Addison-Wesley. ISBN 978-0-201-47950-8.

대해

대해  대해서는 낮습니다.따라서 주기는 n

대해서는 낮습니다.따라서 주기는 n