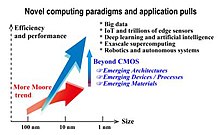

CMOS를 넘어

Beyond CMOSBeyond CMOS는 [5]CMOS 스케일링[1][2][3][4] 한계를 넘어 발열 효과에 의해 디바이스 밀도와 속도를 제한하는 미래의 디지털 로직 기술을 말합니다.

Beyond CMOS는 ITRS 2.0(2013)과 그 후속 제품인 International Roadmap for Devices and Systems의 7가지 포커스 그룹 중 하나입니다.

CMOS를 사용한 CPU는 1986년부터 출시되었습니다(예를 들어 12MHz Intel 80386).CMOS 트랜지스터 치수가 축소됨에 따라 클럭 속도도 향상되었습니다.2004년 이후 CMOS CPU 클럭 속도는 약 3.5GHz로 안정되어 있습니다.

CMOS 디바이스의 사이즈는 계속 축소되고 있습니다.인텔의 체크톡과 ITRS를 참조해 주세요.

- 2012년 22나노미터 Ivy Bridge

- 2014년 4분기에 출하된 최초의 14나노미터 프로세서입니다.

- 삼성전자는 2015년 5월 10나노미터 핀펫 [7]칩 300mm 웨이퍼를 선보였다.

CMOS 트랜지스터가 여전히 [4]3nm 이하에서 작동할지는 아직 확실하지 않습니다.3나노미터 참조.

테크놀로지 비교

2010년경 NRI(Nano Electronic Research Initiative)는 다양한 기술의 회로를 연구했습니다.[2]

Nikonov는 2012년에 ([2]이론적으로) 많은 기술을 벤치마킹하여 [8]2014년에 업데이트하였습니다.2014년 벤치마킹에는 11개의 전자 기술, 8개의 스핀트로닉 기술, 3개의 궤도 전자 기술, 2개의 강유전체 기술,[8] 1개의 스트렌트로닉 기술이 포함되었습니다.

2015 ITRS 2.0 보고서에는 RAM과 로직 게이트를 다루는 Beyond CMOS에 [9]대한 자세한 장이 포함되어 있습니다.

일부 조사 영역

- 터널 접합 장치(예: 터널 전계 효과 트랜지스터[10])

- 안티몬화 인듐 트랜지스터

- 카본 나노튜브 FET(예: CNT 터널 전계효과 트랜지스터)

- 그래핀나노리본

- 분자 전자 공학

- spintronics - 다양한 종류

- 향후의 저에너지 전자 테크놀로지, 초저방산 전도 경로 등

- 포토닉스 및 광학 컴퓨팅

- 초전도 컴퓨팅

- 고속 단일 플럭스 양자(RSFQ)

초전도 컴퓨팅 및 RSFQ

초전도 컴퓨팅에는 전자 신호 처리 및 컴퓨팅에 초전도 장치(조셉슨 접합부)를 사용하는 CMOS를 넘어선 여러 기술이 포함됩니다.사용 가능한 초전도체가 극저온 온도를 필요로 한다는 단점에도 불구하고 2005년 기술 조사에서 NSA는 고속 단일 플럭스 양자(RSFQ) 로직이라고 불리는 변종을 유망한 것으로 간주했다.보다 에너지 효율이 높은 초전도 로직 변형이 2005년부터 개발되어 대규모 [11][12]컴퓨팅용으로 검토되고 있습니다.

「 」를 참조해 주세요.

- 반도체 국제 기술 로드맵

- 디바이스 및 시스템 국제 로드맵

- 무어의 법칙

- MOSFET 스케일링

- 나노스트레인, 저전력 스위치용 압전 재료 특성화 프로젝트

- 초저전력 초전도 전자제품 이니셔티브의 EU 축소 경로인 S-PLUST

- 확률론적 상보 금속 산화물 반도체(PCMOS)

레퍼런스

- ^ CMOS를 넘어 도로 확장.Hutchby 2002

- ^ a b c Nikonov, Dmitri E.; Young, Ian A. (September 2012). "Overview of Beyond-CMOS Devices and A Uniform Methodology for Their Benchmarking". arXiv:1302.0244 [cond-mat.mes-hall].

- ^ Bernstein; et al. (2011). "Device and Architecture Outlook for Beyond CMOS Switches".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ a b "Review of Advanced and Beyond CMOS FET Technologies for Radio Frequency Circuit Design. Carta 2011" (PDF). Archived from the original (PDF) on 2015-02-23. Retrieved 2015-02-23.

- ^ Frank, D.J. (March 2002). "Power-constrained CMOS scaling limits". IBM Journal of Research and Development. 46 (2.3): 235–244. CiteSeerX 10.1.1.84.4043. doi:10.1147/rd.462.0235.

- ^ "Beyond CMOS" (PDF). The International Roadmap for Devices and Systems (2017 ed.). IEEE. 2018.

- ^ "Samsung vows to start 10nm chip production in 2016". 23 May 2015. Retrieved 16 July 2015.

- ^ a b Nikonov; Young (2015). "Benchmarking of Beyond-CMOS Exploratory – Devices for Logic Integrated Circuits". IEEE Journal on Exploratory Solid-State Computational Devices and Circuits. 1: 3–11. Bibcode:2015IJESS...1....3N. doi:10.1109/JXCDC.2015.2418033.

- ^ Beyond CMOS (PDF). International Technology Roadmap for Semiconductors 2.0 (2015 ed.).

- ^ Seabaugh (September 2013). "The Tunneling Transistor". IEEE Spectrum. IEEE. 50 (10): 35–62. doi:10.1109/MSPEC.2013.6607013. S2CID 2729197.

- ^ Holmes, D.S.; Ripple, A.L.; Manheimer, M.A. (June 2013). "Energy-efficient superconducting computing—power budgets and requirements". IEEE Trans. Appl. Supercond. 23 (3). 1701610. Bibcode:2013ITAS...2301610H. doi:10.1109/TASC.2013.2244634. S2CID 20374012.

- ^ Holmes, D.S.; Kadin, A.M.; Johnson, M.W. (December 2015). "Superconducting Computing in Large-Scale Hybrid Systems". Computer. 48 (12): 34–42. doi:10.1109/MC.2015.375. S2CID 26578755.

추가 판독치

- Banerjee, Niloy (2019-09-03). "New Door in the "Beyond CMOS" World". BISinfotech. Archived from the original on 2022-05-13. Retrieved 2022-05-13.