인텔 8255

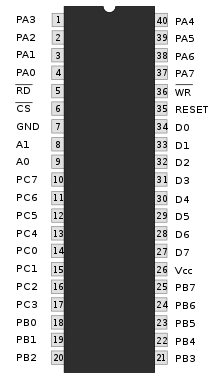

Intel 8255인텔 8255(또는 i8255) 프로그램 가능한 주변 인터페이스(PPI) 칩은 인텔 8080 마이크로프로세서를 위해 1970년대 전반기에 인텔이 개발하고 제조했다.8255는 24개의 병렬 입출력 라인에 다양한 프로그래밍 가능한 작동 모드를 제공한다.

8255는 인텔이 8085, 8086 마이크로프로세서와 그 후손들과 함께 사용하도록 설계한 MCS-85 칩 제품군의 일원이다.[1]처음에는 40핀 DIP로, 나중에는 44핀 PLCC 패키지로 출시되었다.[2]그것은 디지털 처리 시스템에서 광범위한 적용가능성을 발견했고 후에 다른 제조업체들에 의해 복제되었다.82C55는 더 빠른 속도와 더 낮은 전류 소비를 위한 CMOS 버전이다.

8255의 기능은 현재 대부분 하위 기능으로 대형 VLSI 처리 칩에 내장되어 있다.8255의 CMOS 버전은 여전히 레네사스에 의해 만들어지고[3] 있지만 대부분 마이크로컨트롤러의 I/O를 확장하는데 사용된다.

유사칩

8255는 모토로라 6800 계열의 모토로라 6820 PIA(Peripheral Interface Adapter)와 유사한 기능을 가지고 있으며, 원래 40핀 DIL로도 패키지되어 있다.8255는 24개의 I/O 핀에 4개의 프로그래밍 가능한 방향 비트를 제공한다. 하나는 포트 A(7:0)용이고 다른 하나는 포트 B(7:0), 다른 하나는 포트 C(3:0)용이고 다른 하나는 포트 C(7:4)용이다.반대로 모토로라와 MOS 칩은 16개의 I/O 핀과 4개의 제어 핀만을 제공하지만, 모토로라/MOS 칩은 모든 I/O 핀의 방향(입력 또는 출력)을 개별적으로 프로그래밍할 수 있다.둘 다 일정량의 자동 핸드셰이킹과 인터럽트 생성을 할 수 있는 구성을 가지고 있다.

다른 비교 가능한 마이크로프로세서 I/O 칩은 시그니처 2650 제품군, Z80 PIO, Western Design Center WDC 65C21(모토로라 6820/6821과 동일), MOS Technology 6522 VIA 및 6526 CIA의 2655 Programmable Peripheral Interface이다.

변형

인텔 ID8255A의 산업용 등급 버전은 US$17.55에 100 이상에 제공되었다.[4]사용 가능한 인텔 8255A-5 버전은 $6.55 $100 이상이었다.[5]이용 가능한 82C55A CMOS 버전은 오키 일렉트로닉 인더스트리에 아웃소싱되었다.[6]동유럽에서는 소련에서는 KR580VV55A로, 체코슬로바키아에서는 테슬라가 MHB8255A로 등가 회로를 제조하였다.

적용들

8255는 많은 마이크로컴퓨터/마이크로컨트롤러 시스템과 SV-328과 모든 MSX 모델과 같은 가정용 컴퓨터에서 널리 사용되었다.8255는 N8VEM과 같은 수많은 홈 빌드 컴퓨터와 함께 IBM-PC, [7]PC/XT, PC/jr 및 클론에서 사용되었다.

함수

8255는 CPU 또는 디지털 시스템에서 프로그래밍 가능한 병렬 I/O에 대한 액세스를 제공한다.[8]8255에는 24개의 입출력 핀이 있다.[9]이들은 3개의 8비트 포트(A, B, C)로 나뉜다.[10]포트 A와 포트 B는 8비트 입출력 포트로 사용할 수 있다.포트 C는 8비트 입/출력 포트 또는 2개의 4비트 입/출력 포트로 사용하거나 포트 A와 B의 핸드셰이크 신호를 생성하기 위해 사용할 수 있다.

3개의 포트는 다음과 같이 추가로 그룹화된다.

- 그룹 A는 포트 A와 포트 C의 상부로 구성된다.

- 그룹 B는 포트 B와 포트 C의 하위 부분으로 구성된다.

8개의 데이터 라인(D0–D7)을 이용할 수 있으며(8비트 데이터 버퍼 포함)은 각각 읽기 및 쓰기 작업을 위한 액티브 로우 신호인areRD(핀 5) 및 {\WR(핀 36)의 상태에서 포트나 제어 레지스터에 데이터를 읽거나 쓸 수 있다.주소 라인 A와1 A는0 아래 나열된 각 포트 또는 제어 레지스터의 데이터 레지스터에 액세스할 수 있다.

A을1 A을0 포트 선택됨 0 0 A항 0 1 B항 1 0 좌현 C 1 1 관리대장

제어신호 칩 선택 CS(핀 6)를 사용하여 8255 칩을 활성화한다.능동-낮은 신호로, 즉 CS = 0일 때 8255가 활성화된다.RESET 입력(핀 35)은 8085, 8086 등과 같이 시스템의 RESET 라인에 연결되어 있어, 시스템이 리셋되면 모든 포트가 입력 라인으로 초기화된다.이것은 포트 방향 설정의 불일치로 인해 8255 및/또는 그것에 연결된 모든 주변 장치가 파괴되는 것을 방지하기 위한 것이다.예를 들어 포트 A에서 8255에 연결된 입력 장치를 생각해 보십시오.이전 작업에서 포트 A가 출력 포트로 초기화되고 현재 구성을 사용하기 전에 8255가 재설정되지 않으면 8255와 연결된 장치가 모두 데이터를 전송하기 때문에 연결된 입력 장치나 8255 또는 둘 다 손상될 가능성이 있다.

제어 레지스터(또는 제어 논리 또는 명령어 레지스터)는 포트의 작동 모드 및 입력/출력 지정에 사용되는 8비트 레지스터다.[11]

8255의 작동 모드

8255의 두 가지 기본 작동 모드가 있다.

- 비트 설정/재설정 모드(BSR 모드)

- 입력/출력 모드(I/O 모드)

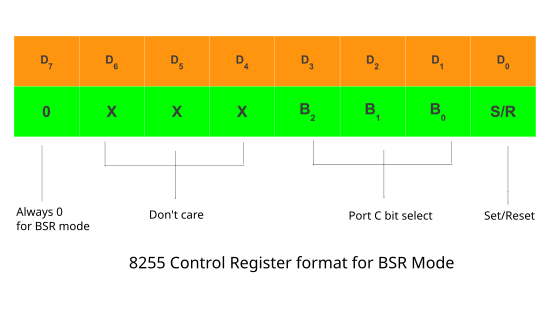

두 모드는 제어 워드 레지스터의7 D 비트에 존재하는 값을 기준으로 선택된다.D7 = 1, 8255가 I/O 모드로 동작하고, D7 = 0일 때는 BSR 모드로 동작한다.

비트 설정/재설정(BSR) 모드

비트 설정/재설정(BSR) 모드는 포트 C에서만 사용할 수 있다.포트 C(PC7 - PC0)의 각 라인은 컨트롤 워드 레지스터에 적절한 값을 기록하여 설정하거나 재설정할 수 있다.BSR 모드와 I/O 모드는 독립적이며 BSR 모드를 선택하면 I/O 모드의 다른 포트 작동에 영향을 주지 않는다.[12]

- BSR 모드의 경우7 D 비트는 항상 0이다.

- 비트6 D, D, D는54 상관없다.

- 비트3 D, D2, D는1 포트 C의 핀을 선택하는 데 사용된다.

- 비트 D는0 포트 C의 선택된 핀을 설정/재설정하는 데 사용된다.

포트 C 핀의 선택은 다음과 같이 결정된다.

| D3 | D2 | D1h | 포트 C의 비트/핀이 선택됨 |

|---|---|---|---|

| 0 | 0 | 0 | PC0 |

| 0 | 0 | 1 | PC1 |

| 0 | 1 | 0 | PC2 |

| 0 | 1 | 1 | PC3 |

| 1 | 1 | 0 | PC6 |

| 1 | 1 | 1 | PC7 |

예를 들어 PC를5 설정해야 할 경우 제어 단어에서

- BSR 모드인 만큼7 D = '0'이다.

- D4, D5, D는6 사용하지 않으므로 '0'으로 가정한다.

- PC를5 선택해야 하므로 D3 = '1', D2 = '0', D = '11'이다.

- PC를5 설정해야 하므로 D0 = '1'이다.

따라서 위의 값에 따라 0B(Hex)가 제어 워드 레지스터(CWR)에 로드된다.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

입력/출력 모드

이 모드는 제어 워드 레지스터의 D7 비트가 1일 때 선택된다.I/O 모드는 3가지로 구성된다.[13]

- 모드 0 - 단순 I/O

- 모드 1 - 스트로브 I/O

- 모드 2 - 스트로브 양방향 I/O

제어 워드 형식

- D0, D1, D, D는34 각각 포트 C 하부, 포트 B, 포트 C 상부 및 포트 A에 할당된다.이 비트가 1이면 해당 포트는 입력 포트의 역할을 한다.예를 들어, 만약0 D4 = D = 1이라면, 낮은 포트 C와 포트 A는 입력 포트의 역할을 한다.이들 비트가 0이면 해당 포트가 출력 포트로 작용한다.예를 들어 D1 = D3 = 0이면 포트 B와 상부 포트 C가 출력 포트의 역할을 한다.

- D는2 그룹 B(포트 B 및 하부 포트 C)의 모드 선택에 사용된다.D2 = 0이면 모드 0이 선택되고 D2 = 1이면 모드 1이 선택된다.

- D5&D는6 그룹 A(포트 A 및 상부 포트 C)의 모드 선택에 사용된다.선정은 다음과 같이 한다.

| D6 | D5 | 모드 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | X | 2 |

- I/O 모드인 만큼7 D = 1

예를 들어 포트 B와 상위 포트 C를 입력 포트로 초기화해야 하고 하위 포트 C와 포트 A를 출력 포트(모두 모드 0)로 초기화해야 하는 경우:

- I7/O 모드니까 D = 1.

- 모드 선택 비트, D2, D5, D6은 모드 0 작동 시 모두 0이다.

- 포트1 B와 상부 포트 C는 입력포트로 작동해야 하므로 D)D=1이다3.

- 포트4 싱크 하부 포트 C는 출력포트로 작동해야 하므로 D)D=00.

따라서 원하는 작동을 위해 제어 워드 레지스터에 "10001010" = 8A(헥스)를 장착해야 한다.

모드 0 - 단순 I/O

이 모드에서 포트는 핸드셰이킹 신호 없이도 간단한 I/O 작업에 사용할 수 있다.포트 A, 포트 B는 간단한 I/O 작업을 제공한다.두 절반의 포트 C는 추가 8비트 포트로 함께 사용하거나 개별 4비트 포트로 사용할 수 있다.포트 C의 두 반쪽은 독립적이기 때문에, 1/2은 입력 포트로, 나머지 반은 출력 포트로 초기화되도록 사용할 수 있다.

모드 0의 입출력 기능은 다음과 같다.

- 출력 포트는 래치되어 있다.

- 입력 포트는 래치되지 않고 버퍼링된다.

- 포트는 핸드셰이크 또는 인터럽트 기능이 없다.

- 포트 4개로 16가지 I/O 조합이 가능하다.

'래칭'은 비트를 저장 레지스터(플립 플롭의 배열)에 넣는 것을 의미하며, 비트는 래칭 후 입력이 바뀌어도 출력을 일정하게 유지한다.

8255의 출력은 마지막으로 기록된 데이터를 보관하기 위해 래치되어 있다.데이터가 버스에서 한 사이클 동안만 유지되기 때문에 이것이 필요하다.따라서 래칭이 없으면 쓰기 주기가 끝나는 즉시 출력이 무효가 된다.

CPU는 현재 값만 읽으면 되기 때문에 입력이 래치되지 않고 나중에 참조해야 할 경우 CPU 레지스터나 메모리에 데이터를 저장한다.포트를 읽는 동안 입력이 변경되면 결과가 불확실할 수 있다.

모드 0 – 입력 모드

- 입력 모드에서 8255는 외부 주변 포트로부터 데이터를 얻고 CPU는 데이터 버스를 통해 수신된 데이터를 읽는다.

- CPU는 먼저 CS를 낮게 만들어 8255 칩을 선택한다.그런 다음 A0 및 A 라인을1 사용하여 원하는 포트를 선택한다.

- 그런 다음 CPU는data{\RD 신호를 발행하여 시스템 데이터 버스를 통해 외부 주변 장치에서 데이터를 읽는다.

모드 0 - 출력 모드

- 출력 모드에서는 CPU가 시스템 데이터 버스를 통해 8255로 데이터를 전송한 후 외부 주변 포트가 8255 포트를 통해 이 데이터를 수신한다.

- CPU는 먼저 CS를 낮게 만들어 8255 칩을 선택한다.그런 다음 A0 및 A1 라인을 사용하여 원하는 포트를 선택한다.

- 그런 다음 CPU는 시스템 데이터 버스를 통해 선택된 포트에 데이터를 쓰기 위해style{\WR 신호를 발행한다.이 데이터는 선택한 포트에 연결된 외부 주변 장치에 의해 수신된다.

모드 1 - 스트로브 입력/출력 모드

핸드셰이크(스트로베드) 입력 또는 출력 작동에 포트 A 또는 포트 B를 사용하고자 할 때 모드 1에서 포트를 초기화한다(포트 A와 포트 B를 초기화하여 다른 모드로 작동할 수 있다(예: 포트 A는 모드 0에서, 포트 B는 모드 1에서 작동할 수 있다).포트 C의 일부 핀은 핸드셰이크 라인으로 기능한다.

이 모드의 포트 B에 대해(입력 포트 또는 출력 포트와 무관하게), PC0, PC1 및 PC2 핀은 핸드셰이크 라인으로 기능한다.

포트 A가 모드 1 입력 포트로 초기화되면 PC3, PC4, PC5가 핸드셰이크 신호로 기능한다.핀 PC6와 PC7은 입력/출력 라인으로 사용할 수 있다.

핸드셰이킹을 지원하는 모드 1은 다음과 같은 특징이 있다.

- 포트 A와 B와 같은 두 개의 포트를 8비트 I/O 포트로 사용할 수 있다.

- 각 포트는 핸드셰이크 신호로 포트 c의 3개 라인을 사용하고 나머지 2개의 신호를 I/O 포트로 사용할 수 있다.

- 인터럽트 논리가 지원된다.

- 입력 및 출력 데이터는 래치되어 있다.

입력 핸드셰이킹 신호

- 1. IBF (Input Buffer Full) - 입력 래치에 정보가 포함되어 있음을 나타내는 출력이다.

- 2. STB(Strobed Input) - 스트로브 입력은 IN 명령을 통해 마이크로프로세서에 입력될 때까지 정보를 보관하는 포트 래치에 데이터를 로드한다.

- 3. INT (Interrupt Request) - 인터럽트를 요청하는 출력이다.INT 핀은 STB 입력이 논리 1로 복귀하면 논리 1이 되고, 마이크로프로세서에 의해 포트에서 데이터가 입력되면 지워진다.

- 4. INT(Interruption Enable) - 입력도 출력도 아니며, 포트 PC4(포트 A) 또는 PC2(포트 B) 비트 위치를 통해 프로그래밍된 내부 비트다.

핸드셰이킹 신호 출력

- 1. OBF(Output Buffer Full) - 데이터가 포트 A 또는 포트 B 래치로 출력될 때마다 Low가 되는 출력이다.이 신호는 ACK 펄스가 외부 장치에서 돌아올 때마다 로직 1로 설정된다.

- 2. ACK(Aknowledge)-OBF 핀이 논리 1 수준으로 되돌아가는 원인이 된다.ACK 신호는 82C55A 포트에서 데이터를 수신했음을 나타내는 외부 장치의 응답이다.

- 3. INT (Interruption request) - 외부 장치가 신호를 통해 데이터를 수신할 때 마이크로프로세서를 자주 방해하는 신호다.이 핀은 내부 INT(Interruption enable) 비트로 인증된다.

- 4. INT (Interruption Enable) - 입력도 출력도 아니며, 내부 비트로서 INTER 핀을 활성화하거나 비활성화하도록 프로그램되어 있다.INTER A 비트는 PC6 비트를 사용하여 프로그래밍되고 INTER B는 PC2 비트를 사용하여 프로그래밍된다.

모드 2 - 스트로베드 양방향 입력/출력 모드

이 모드에서는 포트 A만 초기화할 수 있다.포트 A는 양방향 핸드셰이크 데이터 전송에 사용할 수 있다.즉, 데이터는 동일한 8개 라인(PA0 - PA7)에서 입력하거나 출력할 수 있다.핀 PC3 - PC7은 포트 A의 핸드셰이크 라인으로 사용된다.포트 C(PC0 - PC2)의 나머지 핀은 그룹 B가 모드 0에서 초기화된 경우 입출력 라인으로, 그룹 B가 모드 1에서 초기화된 경우 포트 B의 핸드셰이킹으로 사용할 수 있다.이 모드에서 8255는 시스템 버스를 슬레이브 마이크로프로세서로 확장하거나 플로피 디스크 컨트롤러로 데이터 바이트를 전송하는 데 사용될 수 있다.데이터 송신기와 수신기 사이의 적절한 데이터 흐름과 동기화를 유지하기 위해 승인 및 핸드셰이킹 신호가 제공된다.

참조

- ^ R Theagarajan (1 January 2004). Microprocessor And Its Applications. New Age International. pp. 165–. ISBN 978-81-224-1040-2. Retrieved 3 June 2012.

- ^ Embedded Systems Programming. Miller Freeman Publications. July 1996. p. 256. Retrieved 3 June 2012.

- ^ "Product page for the 82C55A". Renesas Electronics. Retrieved 26 July 2018.

- ^ Intel Corporation, "마이크로컴퓨터 구성요소:새로운 산업용 제품 라인은 산업용 애플리케이션에서 작동할 높은 신뢰도 부품에 대한 수요에 부응한다.", Intel Preview, 1979년 3월/4월, 페이지 11

- ^ Intel Corporation, "Intel 주변장치는 8086 시스템 설계 강화", Intel Preview 특별 이슈: 16비트 솔루션, 1980년 5월/6월, 페이지 22

- ^ Intel Corporation, "NewsBit:여러 제품의 CMOS 버전에 대한 Intel 라이센스 Oki", Solutions, 1984년 7월/8월, 1페이지.

- ^ Robert Jourdain (1986). Programmer's problem solver for the IBM PC, XT, & AT. Brady Communications Co. p. 3. Retrieved 3 June 2012.

- ^ Electronics world. Reed Business Pub. 1996. p. 947. Retrieved 3 June 2012.

- ^ "Intel 82c55 PPI Datasheet" (PDF).

- ^ "PCI 82C55A Datasheet" (PDF).

- ^ Byte. McGraw-Hill. 1981. p. 40. Retrieved 3 June 2012.

- ^ U. S. Shah. "11". Microprocessor & Interfacing Techniques (second ed.). Techmax Publication. pp. 11–5. ISBN 978-81-8492-305-6.

- ^ "i8255 introduction" (PDF).

외부 링크

- drew.hickmans.net, Intel 8255 IC에 대한 전체 설명

- ic-on-line.cn, 데이터시트

- sharpmz.org, 함수 개요

- intel-assembler.it, 기술 세부 정보 프로그래밍 및 코딩 예제

- bitsavers.informatik.uni-stuttgart.de, Intel 8080 Microcomputer Systems 사용자 설명서(1975년 9월)8255 칩 포함.