페이지 크기 확장

Page Size Extension컴퓨팅에서 페이지 크기 확장(PSE)은 x86 프로세서의 기능으로 기존의 4KiB 크기보다 큰 페이지를 사용할 수 있습니다.Pentium Pro는 원래 Pentium 프로세서에 도입되었지만 인텔이 Pentium [1]Pro를 출시하면서 공개 문서화되었습니다.CPUID 명령을 사용하여 x86 [2]CPU에서 PSE의 가용성을 식별할 수 있습니다.

동기

다음과 같은 시나리오를 상상해 보십시오.애플리케이션 프로그램이 1MiB 메모리 블록을 요구합니다.이 요구를 충족시키려면 페이징을 지원하고 오래된 x86 CPU에서 실행되는 운영체제는 각각 4KiB의 256페이지를 할당해야 합니다.페이지 디렉토리와 페이지 테이블을 유지하려면 1KiB의 메모리 오버헤드가 필요합니다.

이 1 MiB 메모리에 액세스하면 256 페이지엔트리의 각 엔트리가 변환 룩사이드버퍼(TLB, 후속 메모리 요구에서 고속 검색을 위해 가상 주소에서 물리 주소 변환으로 기억되는 캐시)에 캐시됩니다.TLB를 어지럽히는 것은 단일 메모리 블록에 할당될 수 있는 페이지 엔트리가 여러 개 있는 가장 큰 단점 중 하나입니다.TLB가 가득 차면 TLB 엔트리를 해방하고 페이지 디렉토리와 페이지테이블을 메모리로 "워크"해야 합니다.마지막으로 메모리에 액세스하여 새로운 엔트리를 TLB로 가져옵니다.이는 심각한 성능 저하로 페이지 크기가 큰 x86 아키텍처를 확장한 가장 큰 동기일 수 있습니다.

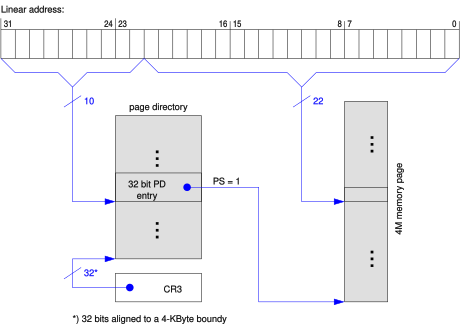

PSE 에서는, 4 KiB 페이지와 함께, 4 MiB 의 페이지 사이즈를 설정할 수 있습니다.앞에서 설명한1 MiB 요구는 1장의 4 MiB 페이지로 간단하게 실현되며 TLB 엔트리는 1장만 필요합니다.다만, 페이지 사이즈가 큰 경우는, 내부 플래그멘테이션의 단점이 있습니다.

작동

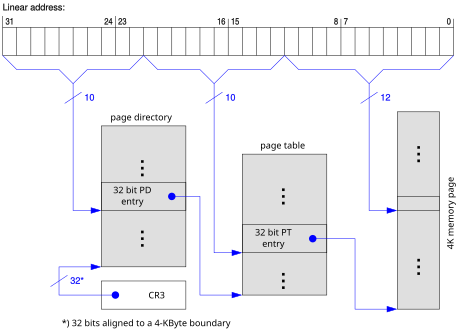

기존 32비트 보호 모드에서는 x86 프로세서는 2레벨의 페이지 변환 방식을 사용하여 제어 레지스터를 실행합니다. CR3는 단일 4KiB 길이의 페이지 디렉토리를 가리키며, 이 디렉토리는 1024 × 4바이트 엔트리로 분할되어 4KiB 길이의 페이지 테이블을 가리키며, 마찬가지로 1024 × 4바이트 엔트리로 구성됩니다.

PSE 활성화(시스템 레지스터의 비트 4, PSE를 설정)CR4)에 의해 이 방식이 변경됩니다.페이지 디렉토리의 엔트리에는 비트7의 이름이 붙은 추가 플래그가 있습니다.PS(페이지 사이즈의 경우).이 플래그는 PSE를 사용하지 않으면 무시되지만 PS가 1로 설정된 페이지 디렉토리 엔트리는 페이지테이블이 아니라 하나의 큰4 MiB 페이지를 가리키고 있습니다.PS가 0으로 설정되어 있는 페이지 디렉토리 엔트리는 PSE가 없는 경우와 같이 동작합니다.

새로운 PSE-36 기능을 CPU에서 사용할 수 있는 경우 CPUID 명령에서 체크한 바와 같이 큰 페이지를 가리키는 페이지 디렉토리 엔트리 내에서 일반 10비트 외에 4비트가 더 사용됩니다.이를 통해 36비트 주소 공간에 큰 페이지를 배치할 수 있습니다.

Physical Address Extension(PAE; 물리 주소 확장)을 사용하면 큰 페이지의 크기가 4 MiB에서2 MiB로 축소되고 PSE는 의 PSE 비트에 관계없이 항상 유효하게 됩니다.CR4.

레퍼런스

- ^ T. Shanley (1998). Pentium Pro and Pentium II System Architecture. Addison-Wesley Professional. p. 439. ISBN 978-0-201-30973-7.

- ^ Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 3A. Intel Corporation. August 2007. pp. 3-26 to 3-28.

외부 링크

- 인텔 64 및 IA-32 아키텍처 소프트웨어 개발자 매뉴얼

- Pentium 프로세서(Robert R)의 4M 페이지 크기 확장에 대해콜린스)