시그니처 8X300

Signetics 8X300| 일반 정보 | |

|---|---|

| 시작됨 | 1976년; 전 ( |

| 설계자 | 과학 마이크로 시스템(SMS) |

| 일반 제조업체 |

|

| 퍼포먼스 | |

| 최대 CPU 클럭 속도 | 8 MHz까지 |

| 데이터 폭 | 16가지 지침, 8가지 데이터 |

| 주소 폭 | 13가지 지침, 1가지 데이터 |

| 건축과 분류 | |

| 지침들 | 8 |

| 물리적 사양 | |

| 패키지 |

|

| 역사 | |

| 후계자 | 8X305 |

8X300은 사이언티픽 마이크로시스템s, Inc.에 의해 SMS 300의 두 번째 소스로 1976년부터 시그니처틱스에 의해 생산되고 판매되고 있는 마이크로프로세서다.[1][2][3][4]SMS는 SMS 300을 개발했지만, 이 제품군의 유일한 제조업체였다.1978년에 시그니틱스는 SMS 300 시리즈에 대한 권리를 구입하여 8X300으로 이름을 바꾸었다.

그것은 빠른 마이크로컨트롤러와 신호 프로세서로 설계되었고, 이 때문에 당시의 기존 NMOS 로직 마이크로프로세서와 상당히 다르다.아마도 주요한 차이점은 양극성 쇼트키 트랜지스터 기술로 구현되었고, 단 250ns의 명령어를 가져오고 해독하고 실행할 수 있다는 점이었을 것이다.데이터는 하나의 명령 사이클 동안 한 장치에서 입력, 수정 및 다른 장치로 출력될 수 있다.

1982년, 시그니틱스는 개선되고 빠른 버전인 8X305를 출시했다.이 프로세서는 군사용 애플리케이션에서 큰 인기를 끌기 시작했으며, 어드밴스트 마이크로 디바이스에 의해 AM29X305로 2차 공급되었다.결국 생산권은 2017년 현재 8X305를 여전히 제공하고 있는 랜스데일 반도체사에 매각되었다.[5]8X300의 복제품은 KM1818VM01(러시아어: к:18181818мв01)이라는 명칭으로 소련에서 제조되었다.[4]

건축

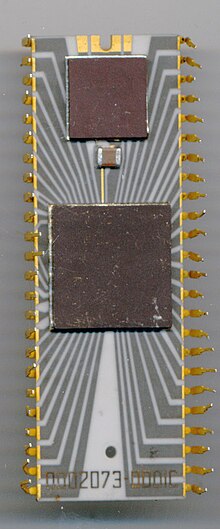

이 장치는 50핀 DIL 세라믹 패키지로 공급되었으며 단일 5V 공급 레일에서 작동된다.칩의 선택된 영역에 3V를 공급하는 온칩 전압 조절기를 완성하려면 외부 패스 트랜지스터가 필요하다.이것은 450mA 미만의 총 전류 방전을 억제하는 데 도움이 된다.

클럭 요건은 8 MHz 결정을 2개의 핀에 직접 연결하여 충족한다.또는 외부 클럭 발생기의 위상 이탈 신호를 사용할 수 있다.

두 번째 고유 기능은 프로그램 메모리에 액세스할 수 있는 전용 13비트 주소와 16비트 데이터 버스로서, 8192개의 16비트 프로그램 단어를 직접 어드레싱할 수 있다.이를 통해 ROM/PROM 프로그램 메모리를 추가 하드웨어 없이 직접 연결할 수 있다.두 번째 결합된 8비트 주소/데이터 버스인 인터페이스 벡터(IV) 버스가 데이터와 I/O에 사용된다.WC(write command)와 SC(select command)라는 두 개의 제어 신호는 다음과 같이 IV 버스의 상태를 결정한다.

- SC=1, WC=0: I/O 주소가 IV 버스에서 출력되고 있음

- SC=0, WC=1: I/O 데이터가 IV 버스에서 출력되고 있음

- SC=0, WC=0: I/O 입력 데이터가 IV 버스에서 예상됨

추가로 LB(좌측 뱅크 선택)와 RB(우측 뱅크 선택)라는 두 개의 신호는 IV 버스 주소 공간을 효과적으로 두 배로 늘렸으며, 한 뱅크의 RAM 메모리와 다른 뱅크의 I/O 포트 간 전환에 가장 많이 사용되었다.

또 다른 특이한 특징은 대부분의 마이크로프로세서의 경우와 마찬가지로 산술 논리 단위(ALU)에서 마스크, 회전, 시프트 및 병합 명령을 실행하기보다는 8X300에 별도의 마스크, 회전, 시프트 및 병합 장치가 있다는 점이다.따라서 데이터는 회전, 마스킹, 수정, 이동 및 병합될 수 있다(이 순서에 따라).

명령 집합

프로세서는 보통 8비트 데이터 바이트를 조작하지만, 마스크 유닛은 단일 비트나 다중 비트 조작을 가능하게 하여 가변 데이터 길이 프로세서가 된다.내부 데이터는 8비트 읽기/쓰기 레지스터(R1 ~ R6, R9 및 보조 레지스터(R0))에 저장된다.보조 레지스터는 ADD 또는 AND와 같은 2-오퍼랜스 지침에 사용되는 피연산자 중 하나를 보유하며, 단일 비트(읽기 전용) 오버플로 레지스터(R8)는 ADD 작업의 이월 비트를 저장한다.IV 버스의 주소 입력에는 가상 쓰기 전용 레지스터 IVL(R7)과 IVR(R15) 2세트가 사용되며, IV 버스와의 데이터 전송에는 가상 레지스터 8개 세트(R16-R23 및 R24-R31) 2세트가 사용된다.R31)가 사용된다.후자의 경우 레지스터 번호의 상위 2비트는 왼쪽 또는 오른쪽 뱅크를 선택하고, 하위 3비트는 데이터가 회전할 위치 수를 정의한다.8비트 IV 버스 버퍼는 IV 버스에서 또는 IV 버스에서 전송되는 마지막 데이터의 복사본을 보관한다.이 데이터는 병합 작업에 사용된다.

지침의 가장 중요한 3가지 비트는 opcode를 정의하고, 지침을 8가지 등급으로 나눈다.

- MOVE 명령은 선택된 레지스터의 내용을 복사하거나, IV 버스에 배치하거나, IV 버스에서 읽거나, IV 버스를 IV 버스로 전송하는 것을 허용한다.

- ADD, AND 및 XOR 클래스는 이 지침과 함께 보조 레지스터의 내용이 지침의 MOVE 부분이 실행되기 전에 소스 레지스터와 결합된다는 점을 제외하면 유사하다.

- XEC 명령은 프로그램 카운터를 늘리지 않고 다른 로컬 주소와 오프셋에서 선택한 명령을 실행할 수 있도록 한다.

- NZT 명령으로 조건부 분기가 구현될 수 있다.

- XMIT 지침은 지시사항에 명시된 8비트 이진 패턴을 지정된 레지스터 또는 IV 버스에 배치할 수 있다.그것은 즉시 하중을 가하는 명령과 비슷하다.

- JMP 명령은 8192 워드 프로그램 메모리 내의 어느 곳에도 무조건 분기를 수행한다.

명령의 나머지 13비트의 사용은 opcode에 따라 달라진다.

- MOVE, AND, ADD 및 XOR 지침: 소스 레지스터를 정의하기 위해 5비트를 사용하고, 회전 또는 마스크 작동을 정의하기 위해 3비트를 사용하고(R/L 필드), 나머지 5비트가 대상 레지스터를 정의한다.

- XEC와 NZT: 5비트를 사용하여 소스 레지스터를 정의하고, 나머지 8비트는 주소 필드를 정의한다.

- XEC: 소스 레지스터의 내용은 먼저 주소 필드에 추가되며, 그 다음 프로그램 주소의 하위 8비트로 사용된다.

- NZT: 소스 레지스터가 0이 아닌 경우 점프를 한다.점프를 할 경우, 주소 필드는 프로그램 주소의 하위 8비트로 사용된다.

- XMIT: 5비트를 사용하여 대상 레지스터를 정의하고, 나머지 8비트는 데이터를 정의한다.

- JMP: 모든 13비트는 프로그램 메모리에서 절대 주소로 사용된다.

이동, 회전, 마스크 및 병합

회전 및 마스크 장치는 레지스터 뱅크와 ALU 사이에 위치한다.따라서 모든 데이터는 원칙적으로 ALU에 들어가기 전에 회전하고 마스킹할 수 있다.

- 장치 회전:이 유닛은 opcode에 지정된 장소 수로 데이터를 오른쪽으로 회전시킨다.

- 마스크 단위:이 장치는 opcode에 지정된 하위 비트의 수를 유지하기 위해 데이터의 상위 비트를 마스킹(제로 설정)한다.

Shift 및 Merge 장치는 ALU와 IV 버스 사이에 위치하며, 따라서 IV 버스에 전송된 모든 데이터는 출력되기 전에 이동 및 병합될 수 있다.

- 시프트 단위:이 유닛은 opcode에 지정된 장소의 수를 좌측으로 이동시킨다.

- 병합 단위:이 유닛은 버퍼의 내용을 IV 버스에 배치하기 전에 IV 버스 버퍼의 opcode에 의해 지정된 비트 수를 데이터와 병합(교체)한다.

참고: 병합할 비트 수에 대한 카운트가 0이면 8비트가 모두 교체된다.

소스와 대상에 따라 다음과 같은 조합이 가능하다.

- 이동, 추가 및 XOR 지침:

- 등록할 등록(IVL 및 IVR 레지스터 포함):회전하다

- IV 버스에 등록(데이터 출력): shift 및 merge

- 등록할 IV-버스 입력: 회전 및 마스크

- IV-bus 출력에 대한 IV-bus 입력: 회전, 마스크, 시프트 및 병합

- IVL 또는 IVR 레지스터에 대한 IV-버스 입력(IV-버스 주소 출력): 회전 및 마스크

- XEC 및 NZT:

- IV-버스 입력: 회전 및 마스크

- 엑스미트

- IV-bus 데이터 출력: shift 및 merge

I/O

8X300으로 데이터를 전송하거나 전송하는 과정은 2단계로,

- 1단계: MOVE, ADD, AND, XOR 또는 XMT 명령 중 하나를 사용하고 가상 레지스터 IVL(좌측 뱅크) 또는 IVR(우측 뱅크) 중 하나를 대상으로 지정하면 IV 버스에서 명령 선택 및 뱅크 선택 신호와 함께 주소가 출력된다.

I/O 주소는 별도로 출력되므로 I/O 포트는 선택 항목을 보류(래치)해야 한다.이 작업은 별도의 주소 디코더와 래치 또는 8X32와 같이 주소 디코딩 및 래치가 통합된 I/O 포트를 사용하여 수행할 수 있다.래칭으로 인해 일단 어드레싱되면 다른 어드레스가 출력될 때까지 I/O 포트는 활성 상태를 유지하며, 다시 어드레싱할 필요 없이 여러 번 액세스할 수 있다.뱅크 선택 신호를 사용하여 추가 주소 지정 없이 빠르게 전환할 수 있는 두 개의 I/O 포트(또는 RAM 주소)를 동시에 활성화할 수 있다.

- 2단계: 데이터는 MOVE, ADD, AND 또는 XOR 명령 중 하나를 사용하고 레지스터 R16-R31 중 하나를 소스 및/또는 대상으로 지정하여 8X300으로 전송된다.선택한 레지스터는 전송에 수반되는 뱅크 선택 신호를 정의한다.

적용들

광범위한 애플리케이션 노트에서 시그네틱스는 8X300을 플로피 디스크 컨트롤러로 사용하는 방법을 보여주었다.수정된 신청서에는 8X330과 함께 8X300을 사용하는 방법이 나와 있었다.기타 설명되는 애플리케이션 참고 사항:

- 텔레타이프 멀티플렉서

- 데이터 집선 장치

- 원격 터미널 컨트롤러

- 컴퓨터 I/O 버스 에뮬레이터

- 인터페이스 RAM 메모리

시연 시스템(서류가방에 포함)과 애플리케이션 노트는 8X300이 교통 조명 제어기에서 사용되고 있음을 보여주었다.

올리베티는 8X300 이상 8X305를 M20 개인용 컴퓨터 시리즈에서 ST506 하드 디스크의 컨트롤러로 사용했다.

Convergent Technologies는 1981년에 8X300, 8X320 및 8X330을 AWS 하드 디스크 컨트롤러에 사용하였다.[6]

Western Digital은 WD1000 ST506 하드 디스크 컨트롤러에 8X300을 사용하고 WD1001 ECC 하드 디스크 컨트롤러에 8X305를 사용했다.[7]

지원 장치

- 8X01: 순환 중복 검사기

- 8X31 / 8T31: 8비트 래치 양방향 I/O 포트

- 8X32 / 8X36 / 8X42: 8비트 래치 주소 가능 양방향 I/O 포트

- 8T39: 주소 지정식 버스 확장기

- 8X41: 비동기 양방향 버스 익스텐더 및 리피터(SABER)

- 8T58: 투명 버스 확장기

- 8X320: 버스 인터페이스 레지스터 어레이

- 8X330: 플로피 디스크 포맷터/컨트롤러

- 8X350: 2048비트 양극성 RAM(256*8) 35ns 액세스 시간

- SMS360 / 8X360: 인터페이스 벡터 바이트

참조

- ^ 8X300 설계 가이드, 1980년 11월, DSPG 문서 80-102

- ^ Electronics Australia, David Edwards, Electronics Australia, 1978년 3월 고속 8비트 양극성 마이크로프로세서

- ^ 1976년 5월, 마이크로컴퓨터 다이제스트 2권 11호 /SMS 300 협약

- ^ a b "The History of the SMS300 and Signetics 8X300 Processors". CPUShack. 16 November 2010. Retrieved 5 January 2017.

- ^ "SL8X305 Microcontroller" (PDF). Lansdale Semiconductor Inc. Retrieved 20 June 2017.

- ^ AWS-220, -230, -240 Hardware Manual (PDF). Convergent Technologies, Inc. April 1982. p. 3-147.

- ^ "Western Digital Components Catalog 1983" (PDF). Retrieved 9 April 2021.