캐시 일관성 프로토콜(예)

Cache coherency protocols (examples)캐시 메모리에 대한 일관성 프로토콜의 예는 다음과 같습니다.알기 쉽게 하기 위해 다이어그램의 상태 "I"(또는 태그 누락)에서 발생한 모든 "불합격" 읽기 및 쓰기 상태 트랜잭션은 표시되지 않습니다.새로운 상태가 직접 표시됩니다.다음 프로토콜의 대부분은 역사적 가치만 가지고 있습니다.현재 사용되는 주요 프로토콜은 R-MESI 유형 / MESI 프로토콜과 HRT-ST-MESI(MOESI 유형) 또는 이들의 하위 집합 또는 확장입니다.

캐시 일관성 문제

각 프로세서, 코어 또는 노드의 전용 캐시가 사용되는 멀티프로세서 시스템, 멀티코어 및 NUMA 시스템과 같은 시스템에서는 동일한 데이터가 여러 캐시에 저장되면 일관성 문제가 발생할 수 있습니다.이 문제는 데이터가 하나의 캐시에서 수정될 때 발생합니다.이 문제는 다음 두 가지 방법으로 해결할 수 있습니다.

- 다른 캐시의 모든 복사본을 비활성화합니다(broadcast-invalidate).

- 다른 캐시의 모든 카피를 갱신합니다(쓰기 브로드캐스트).메모리는 갱신(쓰기 스루) 또는 갱신하지 않는(쓰기 백) 경우도 있습니다.

주의: 일관성은 일반적으로 데이터(오퍼랜드로서)에만 적용되며 명령에는 적용되지 않습니다(자기 수정 코드 참조).

스킴은 다음 기준에 따라 분류할 수 있습니다.

- 스누피 방식 vs 디렉토리 방식 및 공유 캐시

- 라이트 스루 프로토콜과 라이트백(소유권 기반) 프로토콜 비교

- 업데이트 vs 무효화 프로토콜

- 개입 vs 비개입

- 더티 공유 vs 더티 공유 프로토콜(MOESHI vs MESI)

데이터의 일관성을 유지하기 위해 세 가지 접근방식이 채택되었다.

- 버스 감시 또는 스누핑– 일반적으로 버스 기반 SMP에 사용– 대칭 멀티프로세서 시스템/멀티코어 시스템

- 디렉토리 베이스(메시지 패스)는 모든 시스템에서 사용할 수 있지만 일반적으로 NUMA 시스템 및 대규모 멀티코어 시스템에서 사용할 수 있습니다.

- 공유 캐시 – 일반적으로 멀티코어 시스템에서 사용

스누피 일관성 프로토콜

SMP 시스템과 같은 버스 기반 시스템에서 사용되는 프로토콜

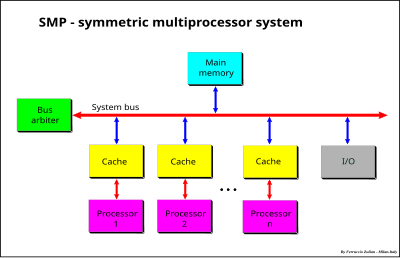

SMP – 대칭형 멀티프로세서 시스템

각 프로세서에는 프로세서와 메인 메모리 사이의 브리지 역할을 하는 자체 캐시가 있습니다.연결은 시스템 버스 또는 크로스바("xbar") 또는 주소용 버스와 데이터용 크로스바(데이터 크로스바)[1][2][3]의 두 가지 접근 방식을 혼합하여 이루어집니다.

이들 시스템의 병목현상은 트래픽과 메모리 대역폭입니다.대역폭은 대규모 데이터 버스 경로, 데이터 크로스바, 메모리 인터리빙(멀티 뱅크 병렬 액세스) 및 잘못된 데이터 트랜잭션을 사용하여 증가할 수 있습니다.트래픽은, 공유 메모리의 「필터」로서 기능하는 캐시를 사용하는 것에 의해서 삭감할 수 있습니다.즉, 캐시는 SMP 시스템의 공유 메모리의 필수 요소입니다.

공통 메모리를 공유하는 개별 캐시를 가진 멀티프로세서 시스템에서는 동일한 데이텀을 여러 캐시에 저장할 수 있습니다.데이터가 1개의 캐시에서만 변경되면 데이터 일관성 문제가 발생할 수 있습니다.

여러 프로세서에 대한 일관성을 유지하기 위한 프로토콜을 캐시 일관성 프로토콜이라고 합니다.

보통 SMP에서 일관성은 "Bus watching" 또는 "Snoopy" 접근법에 기반합니다(피너츠의 문자 Snoopy 이후).

스누핑 시스템에서는 모든 캐시가 버스 트랜잭션을 감시(또는 스누핑)하여 데이터를 대행 수신하고 해당 캐시에 복사본이 있는지 확인합니다.

캐시 [4]간의 데이터 일관성을 유지하기 위해 다양한 캐시 일관성 프로토콜이 사용됩니다.

이러한 프로토콜은 일반적으로 캐시 상태(3~5 및 7 이상)와 이들 사이의 트랜잭션에 따라 분류되지만, 이로 인해 혼동이 발생할 수 있습니다.

이 정의는 이러한 정의들이 만들어내는 행동으로서 중요하고 필수적인 정보가 부족하기 때문에 불완전하다.이러한 작업은 프로세서 또는 버스에서 실행할 수 있습니다(예: 개입, 무효화, 브로드캐스트, 업데이트 등).액션의 유형은 구현에 따라 달라집니다.동일한 상태와 동일한 트랜잭션 규칙을 가진 프로토콜은 다를 수 있습니다. 예를 들어 수정되지 않은 데이터에 대한 공유 간섭이 있는 프로토콜 MESI와 개입 없이 MESI(아래 참조)가 있습니다.상태가 다른 프로토콜은 실질적으로 동일한 프로토콜일 수 있습니다. 예를 들어 4-상태 MESI 일리노이 및 5-상태 MESI(R-MESI) IBM / MESIF-Intel 프로토콜은 동일한 기능의 다른 구현일 뿐입니다(아래 참조).

가장 일반적이고 인기 있는 프로토콜은 MESI와 5-state MOESHI라는 약자로 알려진 4-state 캐시로 간주되며, 이는 단지 사용된 상태의 이름에서 파생된 용어로 발음하기 위한 것입니다.다른 프로토콜은 동일한 상태 또는 하위 집합을 사용하지만 구현은 다르고 종종 다르지만 동등한 용어를 사용합니다.MESI, MOESHI 또는 이들 중 하위 집합이라는 용어와 함께 일반적으로 특정 프로토콜 대신 프로토콜 클래스를 참조합니다.

캐시 상태

상태 MESI와 MOESHI는 보통 다른 이름으로 불립니다.

- M=Macebook 또는 D=Macebook 또는 DE=Macebook-Exclusive 또는 EM=Macebook 수정됨

- 1개의 캐시에서만 변경 가능– 교환 시 기입이 필요합니다.

- 데이터는 하나의 캐시에만 저장되지만 메모리 내의 데이터는 업데이트되지 않습니다(메모리, 클린하지 않음).

- O=Owner 또는 SD=Shared Dirty 또는 SM=Shared Modified 또는 T=Distributed

- 교환 시 변경, 공유, 소유, 기입이 필요합니다.

- 데이터는 여러 캐시에 저장될 수 있지만 메모리 내의 데이터는 업데이트되지 않습니다(메모리, 클린되지 않음).하나의 캐시만 "소유자"이고 다른 캐시는 "유효"(S/V/SC)로 설정됩니다.버스 읽기 요청 시 데이터는 메모리 대신 "소유자"에 의해 제공됩니다.

- E=Color 또는 R=Color 또는 VE=Valid-Exclusive 또는 EC=Color Clean 또는 Me=Color

- clean, 1개의 캐시에만 있습니다.

- 데이터는 1개의 캐시에만 저장되며 메모리에 클린됩니다.

- S=공유 또는 V=유효 또는 SC=공유 클린

- I = i i i.

- 캐시 행이 잘못되었습니다.캐시 행이 존재하지 않는 경우(태그 매칭이 없는 경우) 무효로 간주됩니다.따라서 무효 데이터는 데이터는 존재하지만 무효 또는 캐시 내에 존재하지 않는 것을 의미합니다.

특수 상태:

- F=Forward 또는 R=Forward

- MESI 프로토콜의 추가 상태

- 마지막으로 읽은 데이터일부 확장 MESI 프로토콜(MESI 또는 R-MESI IBM,[5][6] MESIF – Intel[7][8])에서 사용되는 수정되지 않은 공유 데이터의 "소유자"인 특수한 "유효한" 상태입니다.R/F 상태는 값이 깨끗하지만 여러 캐시 간에 공유될 때 "간섭"을 허용하기 위해 사용됩니다.이 캐시는 개입(공유 개입)을 담당합니다.버스 읽기 요청에서는 데이터가 메모리 대신 이 캐시에 의해 공급됩니다.MERSI와 MESIF는 서로 다른 용어(R이 아닌 F)를 가진 동일한 프로토콜입니다.R을 「shared last」(SL)[9][10]라고 하는 경우가 있습니다.

- 상태 R = 최근은 MERSI = R-MESI 프로토콜뿐만 아니라 다른 여러 프로토콜에서도 사용된다.이 상태는 다른 상태와 조합하여 사용할 수 있습니다.예를 들어 RT-MESI, HR-MESI, HRT-MESI,[6][11][12] HRT-ST-MESI 등입니다.이 상태를 사용하는 모든 프로토콜은 R-MESI 유형으로 간주됩니다.

- H=MESI – H-MESI([11]MESI 프로토콜의 표준 상태)

- Hover(H) 상태를 사용하면 캐시 엔트리의 대응하는 값이 비활성 복사본인 경우에도 캐시 행이 디렉토리의 주소 태그를 유지할 수 있습니다.유효한 「읽기」또는 「쓰기」조작에 의해 버스상에서 대응하는 값(주소 태그 매칭)이 발생했을 경우, 엔트리는 유효한 카피로 갱신되어 S 로 그 상태가 변화한다.

- 이 상태는 다른 상태와 조합하여 사용할 수 있습니다.예를 들어 HR-MESI, HT-MESI, HRT-MESI,[6][11][12] HRT-ST-MESI입니다.

다양한 일관성 프로토콜

| 프로토콜 | |

|---|---|

| SI 프로토콜 | 기입 스루 |

| MSI 프로토콜 | 시냅스 프로토콜[4] |

| MEI 프로토콜 | IBM 파워PC 750,[13] MPC7400[6] |

| MES 프로토콜 | 반딧불 프로토콜[4] |

| MESI 프로토콜 | Pentium II,[14] PowerPC, 인텔 Harpertown (Xeon 5400) |

| MOSI 프로토콜 | 버클리 의정서[4] |

| 모에시 프로토콜 | AMD64,[15] MOESHI,[16] T-MESI IBM[12] |

| 사용된 용어 | |

|---|---|

| 일리노이 의정서 | D-VE-S-I(= 확장 MESI)[4][17] |

| 1회 쓰기 또는 우선 쓰기 | D-R-V-I(= MESI) |

| 버클리 의정서 | D-SD-V-I(= MOSI) |

| 시냅스 프로토콜 | D-V-I(= MSI) |

| 반딧불 프로토콜 | D-VE-S(= MES) DEC[4] |

| 드래곤 프로토콜 | D-SD(SM?)-SC-VE(= MOES) Xerox[4] |

| Bull HN ISI 프로토콜 | D-SD-R-V-I(= MOESHI)[20] |

| MERSI (IBM) / MESIF (Intel) 프로토콜 | |

| HRT-ST-MESI 프로토콜 | H=폭발, R=폭발,T=Matrix, ST=Shared-Tagged – IBM[11][12] – 주의: 주요 용어는 SD-D-R-V-I와 MOESI이므로 둘 다 사용됩니다. |

| POWER4 IBM 프로토콜 | Mu-T-Me-M-S-S-IL(L2 7개 스테이트)[9]

(*) 특수 상태– 로드 및 스토어 더블워드 예약 요청 (64비트 구현용) |

스누피 일관성 작업

- 버스 트랜잭션

- 데이터 특성

- 캐시 조작

버스 트랜잭션

주요 조작은 다음과 같습니다.

- 기입 스루

- 라이트백

- 쓰기 할당

- 할당하지 않고 쓰기

- 캐시 개입

- 공유 개입

- 더러운 개입

- 무효화

- 라이트 브로드캐스트

- 개입 브로드캐스트

기입 스루

- 캐시 라인은 캐시 및 MM 또는 MM(write no-allocate)에서만 업데이트됩니다.

- 구현이 간단하고 대역폭을 많이 사용합니다.싱글 쓰기에 적합합니다.

라이트백

- 데이터는 캐시에만 기록됩니다.데이터는 캐시에서 데이터가 교체되거나 다른 캐시에 의해 필요할 때만 MM에 다시 쓰기가 됩니다(쓰기 정책 참조).

- 같은 캐시 라인상의 멀티 기입에 적합합니다.

- 중간 솔루션:Write Through는 첫 번째 쓰기, Write-Back은 다음 쓰기(Write-Once 및 Bull HN ISI[20] 프로토콜)입니다.

쓰기 할당

할당하지 않고 쓰기

- 누락 시 데이터는 캐시를 포함하지 않고 MM으로만 작성되며, Bull HN ISI 프로토콜과 마찬가지로 D 또는 SD 캐시(소유자 업데이트)에 있는 "소유자"에 작성됩니다(MM에 있는 경우).

- Write-no-Alocate는 보통 Write Through와 관련지어집니다.

- 캐시 개입

- (또는 간단히 "방지")

- – 공유 개입 – 공유 클린 개입 (수정되지 않은 데이터에 대한)

- – Read Miss에서 데이터는 MM 대신 소유자 E 또는 R/F 또는 S에 의해 제공됩니다(Illinois, IBM R-MESI 유형 및 Intel MESIF 프로토콜 참조).

- – 공유 개입 – 공유 클린 개입 (수정되지 않은 데이터에 대한)

- – 더러운 개입(수정된 데이터에 대한)

- – 읽기 오류 시 데이터는 MM이 아닌 M(D) 또는 O(SD) 소유자 또는 E(R)(*)에 의해 제공됩니다(예: MOESHI 프로토콜, RT-MESI 등).

- – 더러운 개입(수정된 데이터에 대한)

- (*) – 원래 제안서의 MOESHI 프로토콜[16] 및 기타 일부 구현에서는 E(R)에 해당되지 않습니다.

- 무효화

- – Write Hit with S(V) 또는 O(SD)(공유) 상태에서는 버스 트랜잭션이 전송되어 다른 캐시 상의 모든 복사가 비활성화됩니다(Write-Invalidate).

- 쓰기 브로드캐스트(쓰기 업데이트)

- – 참고 – 다른 캐시에 대한 업데이트 작업을 스너핑이라고도 합니다.캐시는 버스를 스누핑하고 캐시에 히트가 있는 경우 이 캐시는 버스상에서 전송되는 데이터를 스너핑하여 캐시를 업데이트합니다.또한 H in (H-MESI) 상태의 갱신은 스나핑으로 정의할 수 있습니다.첫 번째 경우에는 쓰기 브로드캐스트 동작에서, 두 번째 경우에는 읽기 동작과 쓰기 동작 모두에서 이 문제가 발생합니다.

- 개입 브로드캐스트

- 쓰기 무효 vs 브로드캐스트

- - 무효화가 일반적인 해결책입니다.

data 특성

캐시된 데이터에는 다음 세 가지 특징이 있습니다.

- 유효성

- 배타성

- 소유권

- 유효성

- – 무효가 아닌 캐시 라인, 즉 MOES/D-SD-R-V.

- 배타성

- – 데이터는 M(D) 또는 E(R) 상태의 1개의 캐시(데이터 공유 없음)에서만 유효하며, MM은 M(D)의 경우 깨끗하지 않고 E(R)의 경우 깨끗하지 않습니다.

- 소유권

- 는 MM(간섭)대신에 프로토콜에 따라 – 요청 데이터 공급할 책임이 큰 캐시 –는 개입이 될 수 있S-E-M modified일리노이 주에서, 또는 R/F-E-M R-MESI형/MESIF 또는 M(D)또는 O(SD)또는 또한 E에(R)MOESI-type 프로토콜(예를 들어에서(*)AMD64,[16]불 HN ISI[20]"리드 미스"작업 빌로우를 보– 캐시 해야 한다.w).

(*) – 구현에 따라 달라집니다.

주의: MOESHI 프로토콜의 보다 제한적인 "소유자" 정의와 보다 일반적인 정의를 혼동하지 마십시오.

캐시 조작

캐시 조작은 다음과 같습니다.

- 읽기 히트

- 읽기 미스

- 기입 적중

- 기입 미스

- 읽기 히트

- – 캐시에서 데이터를 읽습니다.상태는 변하지 않습니다.

- – 경고: 이것은 명백한 작업이기 때문에 이후 더 이상 검토되지 않으며, 상태 트랜잭션 다이어그램에서도 고려되지 않습니다.

- 읽기 미스

- – 데이터 읽기 요청이 버스로 전송됩니다.

- – 다음과 같은 상황이 있습니다.

- 데이터는 MM으로만 저장됨

- – 데이터는 MM에서 읽습니다.

- – 캐시가 E(R) 또는 S(V)로 설정됩니다.

- – "데이터 공유 없음" 검출에 특수 버스 회선("공유 회선")이 사용되는 경우 E(R)Write-Once 및 Bull HN ISI 프로토콜을 제외한 E(R) 상태의 모든 프로토콜에 사용됩니다(아래 "Write Hit" 참조).

- 데이터 MM과 S에서 R-MESI에 국가나 R/F에 형식/MESIF 프로토콜(V)하나 이상의 캐시에 저장되어 있다.

- –에는 세가지 상황 있습니다.

- – 일리노이 프로토콜 – 네트워크를 우선적으로 하지 않고 임의의 임시는 S복사본을 소유권을 할당하는 데 사용됩니다.

-데이터 선택한 캐시로 공급됩니다.캐시를 요청하는 것 S(MM와 공유한 개입이 깨끗한)설정됩니다. - – R-MESI형/MESIF 프로토콜은 복사본 R/F 상태(주인 공유)에 있–.

– 데이터는 R/F 캐시로 공급됩니다.보내는 것은 캐시 S의 및 의뢰 캐시 R/F( 읽기의"소유권"을 놓치다 항상 마지막 요청 캐시에서 찍은 사진이다)– 공유 개입 세트가 바뀌어 있다. - – 모든 또 다른 경우 데이터가 메모리에 의해 및 의뢰 캐시 S(V)설정된다 공급된다.

- 데이터 MM와 E(R)상태에서 캐시 일부분에서 저장되어 있다.

- – 데이타는 E(R)캐시 또는 MM으로, 프로토콜에 따라 공급된다.

E(R)부터 확장 modified(예를 들어 일리노이, 펜티엄(R)2세[14]에 –), R-MESI형/MESIF과 같은 MOESI 구현(예를 들어 AMD64)에서.

– 그 요청 캐시와 E)캐시 S(V)또는 내가곳의 MEI의 프로토콜에 의해 변경된다 S(V), 또는 R/F R-MESI에 형식/MESIF 프로토콜 설정됩니다. - 데이터가 MM로 공급됩니다 모든 또 다른 경우 –.

- 데이터 미디어에 더 많은 캐시가 깨끗하지 않에서 수정.

- 프로토콜 MOESI형 – 데이터 M(D)(SD)또는 O형에 저장된과 S(V)의 다른 캐시.

- – 데이터는 "소유자" M(D) 또는 O(SD)에서 요청 캐시에 전송됩니다.요구 캐시는 S(V)로 설정되며, M(D)은 O(SD)로 변경됩니다.

- – MM이 업데이트되지 않습니다.

- 프로토콜 MESI 유형 및 MEI – 데이터는 M(D)에 저장되고 다른 캐시는 S(V) 상태에 저장됩니다.

- – 두 가지 솔루션이 있습니다.

- – 데이터는 M(D) 캐시에서 요청 캐시로 전송되며 MM(일리노이, Pentium(R) II 등)에도 전송됩니다.

- – 요청 트랜잭션이 중지되고 데이터가 M(D) 캐시에서 MM으로 전송된 후 대기 트랜잭션이 진행되며 MM에서 데이터를 읽을 수 있습니다(예: MESI 및 MSI Synapse 프로토콜).

- – 모든 캐시가 S(V)로 설정됩니다.

- 기입 적중

- – 데이터가 캐시에 기록됩니다.

- – 다음과 같은 상황이 있습니다.

- S(V) 또는 R/F 또는 O(SD) 캐시(공유)

- – 쓰기 무효

- – 카피백

- – 데이터는 캐시에 기록되고 비활성 트랜잭션은 버스로 전송되어 다른 모든 캐시를 비활성화합니다.

- – 캐시가 M(D)으로 설정됩니다.

- – 라이트 스루(Write-Once, Bull HN ISI)

- – 데이터는 캐시 및 MM으로 기록되며 다른 모든 캐시는 비활성화됩니다.캐시는 R(E)로 설정됩니다.

- – 카피백

- – 쓰기 방송(예: Firefly, Dragon)

- - 데이터는 캐시에 쓰여지고 브로드캐스트 트랜잭션이 버스로 전송되어 복사본이 있는 다른 모든 캐시를 업데이트합니다.

- – "공유 회선"이 꺼져 있으면 캐시가 M(D)으로 설정되고, 그렇지 않으면 O(SD)로 설정됩니다.다른 모든 복사본은 S(V)로 설정됩니다.

- E(R) 또는 M(D) 상태의 캐시(외부)

- – 쓰기는 다른 작업 없이 로컬에서 수행할 수 있습니다.상태가 설정(또는 유지) M(D)

- 기입 미스

- – 쓰기 할당

- – Write-no-allocate

- – 데이터는 MM 또는 Bull HN ISI 프로토콜과 마찬가지로 캐시를 우회하여 D(M) 또는 SD(O) 캐시에만 전송됩니다.

일관성 프로토콜

- – 경고 – 간단하게 하기 위해 I 상태(또는 태그 누락)에서 발생한 모든 읽기 및 쓰기 "실패" 상태의 트랜잭션은 그림에 표시되지 않습니다.그들은 새로운 상태에 대해 직접 묘사된다.

- – 주의 – 다음 프로토콜의 대부분은 역사적 가치만을 가지고 있습니다.현재 사용되는 주요 프로토콜은 R-MESI 유형 / MESIF 및 HRT-ST-MESS(MOESI 유형) 또는 이것의 하위 집합이다.

————————————————————————————————————————

MESI 프로토콜

상태 MESI = D-R-V-I

- – 버스 "공유 회선"을 사용하여 다른 캐시에서 "공유" 복사를 검출합니다.

- 프로세서 조작

- 읽기 미스

- 대체 실장은 표준 MESI(개입 없음)와 확장 MESI(개입 있음)의 2가지가 있습니다.

- 1 – MESI '개입 없음'(전원 등)PC 604 [24])

- – 캐시에 M 복사본이 있는 경우 트랜잭션은 중지되고 M 캐시가 MM을 업데이트할 때까지 기다립니다. 그러면 트랜잭션은 계속 진행되며 MM에서 데이터를 읽을 수 있습니다. 두 캐시는 모두 S로 설정됩니다.

- – 그렇지 않으면 MM에서 데이터를 읽습니다. "공유 회선"이 "on"인 경우 캐시는 S로 설정되고 그렇지 않으면 E로 설정됩니다.

- 2 – M 및 E로부터의 MESI "간섭" (Pentium (R) II 등)

- – 캐시에 M 또는 E 복사본(외부)이 있는 경우 데이터는 M 또는 E(간섭)에서 요청 캐시에 공급됩니다.송신 캐시가 M인 경우는, 데이터도 동시에 MM(복사백)으로 기입됩니다.모든 캐시는 S로 설정됩니다.

- – 그렇지 않으면 MM에서 데이터를 읽습니다. "공유 회선"이 "on"인 경우 캐시는 S로 설정되고 그렇지 않으면 E로 설정됩니다.

- 기입 적중

- – 캐시가 M 또는 E(배타적)인 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.

- – 그렇지 않으면 데이터가 캐시에 기록되고 비활성 트랜잭션이 버스로 전송되어 다른 모든 캐시가 비활성화됩니다.

- – 캐시는 M으로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- – M이 '개입 없음'인 경우 데이터는 MM(복사)으로 전송됩니다.

- – M과 "간섭"의 경우 데이터가 요청 캐시 및 MM(복사)으로 전송됩니다.

- – 요청 캐시에 전송되는 데이터(*)와 "간섭"의 경우

- – 상태가 S로 변경(또는 유지)됩니다.

- 버스 읽기 – (RWITM)

- – "버스 읽기"와 같이

- – 캐시가 "Invalid"(I)로 설정됩니다.

- 버스 트랜잭션 무효화

- 캐시가 "Invalid"(I)로 설정되어 있습니다.

- 운용

- – 쓰기 할당

- – 개입: M ~E (*)

- – 쓰기 무효

- – 카피백: M 교환품

- (*) – 확장 MESI

————————————————————————————————————————

모에시 프로토콜

상태 MEOSI = D-R-SD-V-I = T-MESI IBM[12]

- – 버스 "공유 회선"을 사용하여 다른 캐시에서 "공유" 복사를 검출합니다.

- 프로세서 조작

- 읽기 미스

- – 다른 캐시에 M, O 또는 E(*) 복사본이 있는 경우 해당 캐시에 의해 데이터가 제공됩니다(간섭).요청 캐시는 set S, M은 O, E는 S로 변경됩니다.

- – 그렇지 않으면 MM에서 데이터를 읽습니다.

- – "shared line"이 "on"인 경우 요청 캐시는 S, 그렇지 않으면 E로 설정됩니다.

- 기입 적중

- – 캐시가 M 또는 E(배타적)인 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.

- – O 또는 S(공유)의 경우 "비활성화" 트랜잭션이 버스로 전송되어 다른 모든 캐시가 비활성화됩니다.

- – 캐시가 설정(또는 유지)되어 있다.M

- 기입 미스

- – RWITM 작업이 버스로 전송됩니다.

- – "소유자" 또는 MM에서 Read Miss와 마찬가지로 데이터가 공급되고 캐시가 작성(갱신)됩니다.

- – 캐시는 M으로 설정되며 다른 모든 캐시는 I로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- – 캐시가 M, O 또는 E(*)인 경우 데이터는 요청 캐시(간섭)로 전송됩니다.캐시가 E일 경우 상태는 S로 변경되며, 그렇지 않을 경우 설정(또는 유지)되어 있습니다.오

- – 그렇지 않으면 상태가 변경되거나 S로 유지됩니다.

- 버스 읽기 – (RWITM)

- – 캐시가 M, O 또는 E(*)인 경우 데이터가 버스로 전송됩니다(간섭).

- – 캐시가 "Invalid"(I)로 설정됩니다.

- 버스 트랜잭션 무효화

- – 캐시가 "Invalid"(I)로 설정됩니다.

- 운용

- 쓰기 할당

- 개입: M-O-E에서 (*)

- 쓰기 무효

- 카피백: M-O 교환

- – (*) E에 따라 구현

————————————————————————————————————————

일리노이 의정서

상태 MESI = D-R-V-I[4]

- – 특징:

- 운용

- - 쓰기 할당

- - 개입: M-E-S에서

- - 쓰기 무효

- - 카피백: M 교환품

————————————————————————————————————————

Write-Once(또는 Write-First) 프로토콜

상태 D-R-V-I(MESI)

- – 특징:

- – "공유 회선" 사용 안 함(표준 버스 또는 변경 불가능한 버스 프로토콜)

- – 상태 V에서 먼저 쓰기 적중 시 끝까지 쓴 후 다시 복사

- 프로세서 조작

- 읽기 미스

- – 다른 캐시에 D 복사본이 있는 경우 데이터는 이 캐시(간섭)에 의해 제공되며 동시에 MM(복사-백)으로도 기록됩니다.

- – 그렇지 않으면 MM에서 데이터를 읽습니다.

- – 모든 캐시가 V로 설정됩니다.

- 기입 적중

- – 캐시가 D 또는 R(배타적)인 경우 다른 작업을 수행하지 않고 로컬에서 쓰기를 수행할 수 있으며 상태는 D로 설정(또는 유지)됩니다.

- – 그렇지 않으면 V(첫 번째 쓰기 적중) 데이터가 캐시에 기록되고 MM(쓰기 통과)로 기록되므로 다른 모든 캐시가 비활성화됩니다(쓰기-비활성화).– 캐시는 R로 설정됩니다.

- 기입 미스

- – 읽기 오류와 비슷하지만 "invalidate" 명령어(RWITM)와 D 상태의 쓰기 적중(업데이트).캐시는 D로 설정되며 다른 모든 캐시는 "Invalid"(I)로 설정됩니다.

- – 주의 – Write Through는 "Write Miss"에서만 수행됩니다.이 경우 다른 캐시를 무효화하기 위해 어떤 경우에도 버스 트랜잭션이 필요하며, 따라서 이 사실을 이용하여 MM을 업데이트할 수 있습니다. 대신 "Write Hit"에서는 더 이상의 트랜잭션이 필요하지 않으므로 캐시가 다시 업데이트될 경우 "Write Through" 작업이 무용지물이 됩니다.

- 버스 트랜잭션

- 버스 읽기

- – 캐시가 D일 경우 데이터는 요청 캐시(간섭) 및 MM(복사백)으로 전송됩니다.캐시가 V로 설정되었습니다.

- – 그렇지 않으면 상태가 변경되거나 V 상태로 유지됩니다.

- 버스 읽기 – (RWITM)

- – 캐시가 D인 경우 데이터가 버스로 전송됩니다(간섭).

- – 캐시가 "Invalid"(I)로 설정됩니다.

- 버스 트랜잭션 무효화

- – 캐시가 "Invalid"(I)로 설정됩니다.

- 운용

- 쓰기 할당

- 개입: D부터

- Write Through: V 상태의 첫 번째 쓰기 적중

- 쓰기 무효

- 카피백: D 교환

————————————————————————————————————————

Bull HN ISI 프로토콜

(불허니웰 이탈리아)

상태 D-SD-R-V-I(MOESHI)

특허받은 프로토콜(F. Zulian)[20]

- – 특징:

- – Write-Once 프로토콜의 MOESI 확장

- - D 또는 SD 업데이트로 미스에 대한 쓰기 금지

- - RWITM 사용 안 함

- - '공유회선' 사용 안 함

- 프로세서 조작

- 읽기 미스

- - "공유회선"을 "온"으로 하여 "소유자" D 또는 SD에서만 개입하고 R에서는 개입하지 않는 MOESHI와 유사합니다.

- 기입 적중

- - 캐시가 MOESHI와 같이 D 또는 R일 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.캐시가 D로 설정되어 있다(또는 그대로 있다)

- - Write-Once와 마찬가지로 SD 또는 V(첫 번째 쓰기)의 경우 데이터는 캐시에 기록되며 MM(쓰기 스루)로 기록되므로 다른 모든 캐시가 비활성화됩니다(쓰기-비활성화). 캐시는 R로 설정됩니다.

- - 기입 미스

- - 데이터가 캐시를 바이패스하여 버스로 전송됩니다(Write-no-allocate).

- - "소유자" 복사본 D 또는 SD가 있는 경우 "소유자"가 갱신됩니다(Write-no-Alocate – Owner updating 참조). 다른 캐시는 비활성화됩니다."소유자"는 D로 설정(또는 그대로)되어 있습니다.메모리 '더러운' 상태 그대로

- - 그렇지 않으면 데이터가 MM으로 전송되어 다른 모든 캐시가 비활성화됩니다(Write-Invalidate).

- - 기입 미스

- 버스 트랜잭션

- 버스 읽기

- - '오너' D 또는 SD만의 개입을 수반하는 MOESHI와 같다.

- 버스 읽기(쓰기 업데이트/쓰기 무효)

- - 캐시가 D 또는 SD이면 캐시가 갱신되고, 그렇지 않으면 "비활성"(I)으로 설정됩니다.

- 운용

- Write-No-Alocate: 미적용시

- 쓰기 업데이트: 실패 시

- Write Through: 첫 번째 쓰기에서는 다시 복사

- 쓰기 업데이트/쓰기 무효

- 개입: SD-D에서

- Copy-Back(복사백): D 교환 또는 SD 교환(비활성화

- 관찰 - O-E(SD-R) 트랜잭션이 있는 유일한 프로토콜이며, 누락 시 할당되지 않은 쓰기를 사용하는 프로토콜이기도 합니다.

————————————————————————————————————————

시냅스 프로토콜

상태 D-V-I(MSI)[4]

- - 특징:

- - 이 프로토콜의 특징은 각 캐시 라인이 MM인 단일 비트 태그를 가지고 있으며, 이는 캐시가 D 상태임을 나타냅니다.

- - 이 비트는 D 캐시가 업데이트 전에 MM의 응답을 억제할 정도로 빠르게 응답하지 않을 경우 발생할 수 있는 레이스 상태를 방지합니다.

- - 데이터는 항상 MM에서 가져옵니다.

- - '공유회선' 사용 안 함

- - 이 프로토콜의 특징은 각 캐시 라인이 MM인 단일 비트 태그를 가지고 있으며, 이는 캐시가 D 상태임을 나타냅니다.

- 프로세서 조작

- 읽기 미스

- - 다른 캐시에 D카피가 있는 경우 읽기 트랜잭션은 거부됩니다(확인 없음).D 복사본이 다시 MM에 기록되고 V에서 상태가 변경된 다음 요청 캐시가 새 읽기 트랜잭션을 재발송하고 MM에서 데이터를 읽습니다.

- - 그렇지 않으면 MM에서 데이터를 읽습니다.

- - 캐시가 V로 설정되어 있습니다.

- 기입 적중

- 캐시가 D일 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.

- - 그렇지 않으면 V가 Read Miss와 마찬가지로 메모리로부터의 데이터 전송을 포함하여 RWITM(Invalidate Command)을 추가합니다.이 프로토콜은 무효화 트랜잭션을 지원하지 않으므로 이 작업은 다른 V 복사본을 무효화하기 위해서만 수행됩니다.

- - 캐시는 D로 설정됩니다.다른 모든 캐시 복사본은 "Invalid"(I)로 설정됩니다.

- 기입 미스(RWITM)

- - Read Miss와 비슷하지만 invalidate 명령어를 사용합니다.캐시 행은 MM에서 가져온 다음 캐시가 작성(업데이트)됩니다.캐시는 D로 설정됩니다.다른 모든 캐시는 "Invalid"(I)로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- - 캐시가 D이면 데이터가 MM(복사백)으로 전송됩니다.캐시가 V로 설정되었습니다.

- - 그렇지 않으면 상태가 V로 유지됩니다.

- 버스 읽기(RWITM)

- - 캐시가 D일 경우 데이터가 MM(복사)으로 전송됩니다.

- - 캐시(D 또는 V)가 "Invalid"(I)로 설정됩니다.

- 운용

- 쓰기 할당

- 개입: 개입 없음

- 기입 무효: (RWITM)

- 무효 트랜잭션 없음

- 카피백: D 교환

————————————————————————————————————————

버클리 의정서

상태 D-SD-V-I(MOSI)[4]

- - 특징:

- - E 상태가 없는 MOESHI와 동일

- - '공유회선' 사용 안 함

- 프로세서 조작

- 읽기 미스

- - 데이터는 "소유자" 즉, D에서 제공되거나 MM에서 SD에서 제공되며, SD에서 D가 변경됩니다.

- - 캐시가 V로 설정되어 있습니다.

- 기입 적중

- - 캐시가 D(외부)일 경우 다른 작업 없이 로컬에서 쓰기가 가능합니다.

- - 그렇지 않으면(SD 또는 V), "비활성화" 트랜잭션이 버스로 전송되어 다른 캐시가 비활성화됩니다.

- - 캐시가 D로 설정되어 있다(또는 남아 있다)

- 기입 미스

- - RWITM 작업이 버스로 전송됩니다.

- - Read Miss와 마찬가지로 데이터는 "소유자", "D" 또는 "SD" 또는 "MM"에서 가져와 캐시를 업데이트합니다.

- - 캐시는 D로 설정됩니다.다른 모든 캐시는 I로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- 캐시가 D 또는 SD일 경우 데이터를 요청 캐시에 보냅니다(간섭).캐시가 SD로 설정되어 있거나 남아 있다.

- - 그렇지 않으면 캐시가 V에 남습니다.

- 버스 읽기 – (RWITM)

- - 캐시가 D 또는 SD일 경우 데이터가 버스로 전송됩니다(간섭).

- - 캐시가 "Invalid"(I)로 설정되어 있습니다.

- 버스 트랜잭션 무효화

- - 캐시가 "Invalid"(I)로 설정되어 있습니다.

- 운용

- 쓰기 할당

- 개입: D-SD에서

- 쓰기 무효

- 카피백: D-SD 교환

————————————————————————————————————————

파이어플라이(DEC) 프로토콜

상태 D-VE-S(MES)[4]

- - 특징:

- - "비활성" 상태 없음

- - "Write-Broadcasting" + "Write Through"

- - '공유회선'의 사용

- - "Write-Broadcasting"을 통해 "Invalid" 상태를 피할 수 있습니다.

- - 모든 캐시에서 동시 개입(공유 및 더러운 개입 - 수정된 데이터를 수정하지 않은 경우)

- - 이 프로토콜에는 동기식 버스가 필요합니다.

- 프로세서 조작

- 읽기 미스

- - 다른 캐시는 "소유자"로, 다른 모든 캐시와 버스 상의 날짜(동시 개입 - 버스 타이밍이 모두 같은 사이클로 응답하도록 고정됨)를 동시에 제공합니다.그렇지 않으면 데이터는 MM에서 공급됩니다.

- - 캐시 D가 있는 경우 MM(Copy Back)에도 데이터가 동시에 전송됩니다.

- - 다른 캐시에 복사본이 있는 경우 "공유 회선"이 "켜짐"으로 설정됩니다.

- - "Shared line"이 "on"인 경우 모든 캐시가 S로 설정됩니다.그렇지 않으면 요청 캐시는 VE로 설정됩니다.

- 기입 적중

- - 캐시가 D 또는 VE(외부)일 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있으며 캐시는 D로 설정됩니다.

- - 그렇지 않으면 "Write-broadcasting"이 버스로 전송되어 다른 모든 캐시와 MM(Write-Through)을 업데이트합니다.

- - 다른 캐시에 복사본이 있는 경우 "공유 회선"이 "켜짐"으로 설정됩니다."Shared line"이 "off"로 설정되어 있으면 캐시는 VE로 설정됩니다.그렇지 않으면 모든 캐시는 S로 설정됩니다.

- 기입 미스

- - 조작은 2단계로 이루어집니다.Miss를 읽고 Write Hit을 읽습니다.

- - 데이터가 캐시(공유회선 "on")에서 온인 경우, "Write-Broadcasting"이 버스로 전송되어 다른 모든 캐시와 MM(Write Through)을 업데이트합니다.모든 캐시는 S로 설정됩니다.

- - 그렇지 않으면 캐시가 D로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- - 히트 시(D, VE, S)는 버스로 전송되며(간섭), D의 경우 데이터도 MM으로 입력되며 캐시는 S로 설정됩니다.

- 버스 읽기

- - 치면(D, VE 또는 S) 데이터가 버스로 전송됩니다(간섭).

- - 모든 캐시가 S로 설정됩니다.

- 쓰기 브로드캐스트

- - 캐시가 새로운 데이터로 갱신됩니다.상태는 S인 채로 있습니다.

- 운용

- 쓰기 할당

- 개입: D-VE-S에서 (모든 유효한 캐시에서)

- 라이트 브로드캐스트– 라이트 스루

- Copy-Back: 캐시 D와의 교환 및 트랜잭션 시

————————————————————————————————————————

Dragon(Xerox) 프로토콜

상태 D-SD-VE-SC(MOES)[4]

참고 – 상태 SC는 "깨끗하다"는 용어에도 불구하고 다른 프로토콜의 S 상태와 마찬가지로 "깨끗하다"거나 "더럽다"고 할 수 있습니다.SC와 S는 동등합니다.

- - 특징:

- - "비활성" 상태 없음

- - '쓰기 브로드캐스트' ('쓰기 스루' 없음)

- - '공유회선'의 사용

- - "Write-Broadcasting"을 통해 "Invalid" 상태를 피할 수 있습니다.

- 프로세서 조작

- 읽기 미스

- - 데이터는 "소유자" 즉, D에서 제공되거나 MM에서 SD에서 제공되며, SD에서 D가 변경됩니다.

- - "shared line"이 "on"인 경우 캐시는 SC, VE로 설정됩니다.

- 기입 적중

- 캐시가 D 또는 VE(배타적)일 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.캐시가 D로 설정되어 있다(또는 그대로 있다)

- - 그렇지 않으면 SD 또는 SC(공유) 데이터가 캐시에 기록되고 "쓰기 브로드캐스트"가 버스로 전송되어 다른 모든 캐시가 업데이트됩니다.MM은 업데이트되지 않습니다(쓰기 스루 없음).

- - 다른 캐시에 복사본이 있는 경우 "공유 회선"이 "켜짐"으로 설정됩니다.

- - "공유 회선"이 "on"인 경우 캐시는 SD로 설정되며, 그렇지 않은 경우 D로 설정됩니다.가능한 다른 모든 캐시는 SC로 설정됩니다.

- 기입 미스

- - Read Miss와 마찬가지로 데이터는 "소유자", "D" 또는 "SD" 또는 "MM"에서 가져와 캐시를 업데이트합니다.

- - 다른 캐시에 복사본이 있는 경우 "공유 회선"이 "켜짐"으로 설정됩니다.

- - "공유 회선"이 "on"인 경우 업데이트된 데이터는 다른 캐시로 브로드캐스트되고 상태는 SD로 설정됩니다.다른 모든 캐시는 SC로 설정됩니다.

- - 그렇지 않으면 캐시는 D입니다.

- 버스 트랜잭션

- (버스 읽기)

- 캐시가 D 또는 SD일 경우 데이터를 요청 캐시에 보냅니다(간섭).캐시가 SD로 설정되어 있다(또는 남아 있다)

- - 그렇지 않으면 캐시는 SC로 남습니다.

- (버스 읽기)

- 버스 읽기

- - 캐시가 D 또는 SD일 경우 데이터가 버스로 전송됩니다(간섭).

- - 캐시가 SC로 설정되어 있다.

- 쓰기 브로드캐스트

- - 캐시가 새로운 데이터로 갱신됩니다.캐시는 SC 그대로입니다.

- 운용

- 쓰기 할당

- 개입: D-SD에서 (VE에서가 아님)

- 라이트 브로드캐스트

- 카피백: D-SD 교환

————————————————————————————————————————

MERSI (IBM) / MESIF (Intel) 프로토콜

MERSI 또는 R-MESI 상태

상태 MESIF

특허받은 프로토콜 – IBM (1997년)–[6] Intel ( 2002년)[8]

- - MERSI와 MESIF는 동일한 프로토콜입니다(이름만 R이 아닌 F)

- - 특징:

- - '공유회선'의 사용

- 운용

- 쓰기 할당

- 개입: M-E-R/F에서

- 쓰기 무효

- 카피백: M의 교환

————————————————————————————————————————

MESI와 MOESHI

MESI와 MOSESI는 가장 인기 있는 프로토콜입니다.

MOSHI는 MESI 프로토콜의 확장이기 때문에 보다 정교하고 성능이 뛰어나다는 것이 일반적인 의견이다.이는 표준 MESI, 즉 "공유 개입 없음"을 사용하는 MESI와 비교한 경우에만 해당됩니다.MESI Illinois 또는 이에 상응하는 5개 주 프로토콜 MERSI/MESIF와 같이 "공유 개입"이 있는 MESI는 MOESI 프로토콜보다 훨씬 더 높은 성능을 발휘한다.

MOESHI에서 캐시 투 캐시 조작은 수정된 데이터에 대해서만 이루어집니다.MESI Ilinois 유형 및 MERSI/MESIF 프로토콜에서는 캐시 간 작업이 수정된 데이터를 사용하여 항상 수행됩니다.수정된 데이터의 경우, "소유자" M에 의해 개입이 이루어지지만, 다른 캐시(MERSI/MESIF의 R/F 캐시 또는 일리노이 타입으로 선택된 캐시)로 이행되기 때문에 소유권이 상실되지 않는다.유일한 차이점은 MM을 업데이트해야 한다는 것입니다.그러나 MOESHI에서도 교환 시 이 트랜잭션은 다른 수정이 없을 경우 나중에 해야 합니다.그러나 이는 MOESHI 프로토콜을 위한 클린 데이터의 경우처럼 간섭이 없기 때문에 메모리 트랜잭션에 비해 작은 제한입니다.(예: "MOESHI(상하이)와 MESIF Nehalem-EP 사이의 성능 평가"[21] 참조)

최신 시스템에서는 R-MESI/MESI 프로토콜만 사용하거나 MESI와 MOSI 프로토콜의 향상된 병합인 보다 완전한 RT-MESI, HRT-ST-MESI 및 POWER4 IBM 프로토콜만 사용합니다.

주의: 캐시 투 캐시는 멀티프로세서/멀티코어 시스템 간에 직접 연결되어 있는 경우 효율적인 접근 방식이지만 표준 MESI가 선호되는 NUMA 시스템과 마찬가지로 원격 캐시에 있는 경우가 적습니다.POWER4 IBM 프로토콜의 "공유 개입"은 원격 모듈 간에는 적용되지 않고 "로컬"로만 이루어집니다.

————————————————————————————————————————

RT-MESI 프로토콜

- 특징:

- - MESI와 MOSESI의 병합

- - 공유 개입 + 더러운 개입 (깨끗한 데이터와 더러운 데이터 모두)

- - 새로운 상태의 R-MESI 프로토콜과 동일한 기능, O 상태에 상당함유, O 상태에 상당하는 기능

- - '더러운 소유자'로의 이행

- - "소유자"(공유 또는 더티 모두)는 항상 마지막 요청 캐시입니다(새로운 "소유자"(LRU)는 이전 캐시와 비교하여 곧 할당 해제될 가능성이 낮습니다).

- - '소유자'는 T, M, E, R(S를 제외한 모든 것)

- - '공유회선'의 사용

프로세서 조작

- 읽기 미스

- - 다른 캐시에 M 또는 T(더티 오너십) 복사본이 있는 경우 해당 캐시에 의해 데이터가 공급됩니다(더티 개입).요청 캐시는 T로 설정되며 이전 M 또는 T는 S로 변경됩니다.

- - 다른 캐시에 E 또는 R(공유소유) 복사본이 있는 경우 해당 캐시에 의해 데이터가 공급됩니다(공유 개입).요청 데이터가 R로 설정되고 S에서 E 또는 R이 변경됩니다.

- - 그렇지 않으면 MM에서 데이터를 읽고 캐시를 R로 설정합니다.

- 기입 적중

- - 캐시가 M 또는 E(배타적)인 경우 다른 작업 없이 로컬에서 쓰기를 수행할 수 있습니다.

- - 그렇지 않으면 T, R 또는 S(공유)가 "비활성화" 트랜잭션을 버스로 전송하여 다른 모든 캐시를 비활성화합니다.

- - 캐시는 M으로 설정(또는 그대로)되고 다른 캐시는 모두 I로 설정됩니다.

- 기입 미스

- - RWITM 작업이 버스로 전송됩니다.

- - Read Miss와 마찬가지로 "소유자" 또는 MM으로부터 데이터를 공급받아 캐시에 데이터를 기입(업데이트)합니다.

- - 캐시는 M으로 설정되고 다른 캐시는 모두 I로 설정됩니다.

- 버스 트랜잭션

- 버스 읽기

- 캐시가 T, M, R, E일 경우 데이터를 요청 캐시에 보냅니다(간섭).

- - 캐시가 S로 설정되어 있다(또는 남아 있다)

- 버스 읽기 – (RWITM)

- - 캐시가 T, M, R, E일 경우 데이터를 요청 캐시에 보냅니다(간섭).

- - 캐시가 "Invalid"(I)로 설정되어 있습니다.

- 버스 트랜잭션 무효화

- - 캐시가 "Invalid"(I)로 설정되어 있습니다.

- 운용

- 쓰기 할당

- 개입: T-M-R-E에서

- 쓰기 무효

- 카피백: T-M 교환

————————————————————————————————————————

RT-ST-MESI 프로토콜

RT-MESI 프로토콜의[12] 개선 사항이며 HRT-ST-MESI 프로토콜의[11] 하위 집합입니다.

- ST = 공유 태그 부착

- - "Shared-Tagged" 상태를 사용하면 태그 부착 캐시 라인 할당 해제 후에도 개입을 유지할 수 있습니다.

- - T 치환(캐시라인 할당 해제) 시 MM에 데이터를 다시 써야 "소유권"이 상실됩니다.이를 피하기 위해 새로운 상태T S를 사용할 수 있다.Read Miss에서는 이전 T가 S가 아닌 S로T 설정됩니다T.S는 T 할당 해제 시 소유권을 대체할 후보입니다.T "복사" 트랜잭션은 T에서 상태를 변경하는 S 캐시에T 의해 중지됩니다(MM 업데이트 없음).다른 캐시로부터 새로운 읽기가 발생했을 경우, 이 마지막 읽기를 T로 설정하고, S에서는T 이전 T를 변경하며, S에서는 이전T S를 변경한다.

STT1 상태, S, ST2, … S를Tn 더 많이 사용하면 추가적인 개선을 얻을 수 있습니다.

- - Read Miss에서는 S에서T1 T를 변경하고 다른 S의Ti 모든 지수를 "1"씩 증가시킨다.

- - T할당 해제 시 S는T1 "Copy Back" 트랜잭션을 정지하고 T에서 상태를 변경하며 다른Ti S의 모든 지수를 "1" 감소시킨다.

- - 예를 들어Tk S의 경우 체인이 중단되고 지수가 "k"인 모든 S는Ti S의 관점에서T 자동으로 느슨해지며, S로 설정되어T 있는 경우에도 사실상 단순한 S 상태로 간주됩니다.이 모든 것은 S만이T1 개입하여 차단하고 T로 대체하기 때문입니다.예를 들어, TypeT1 TT3, S, S를T4 S로T2 교체한 경우 T를 교체하면 S가 없는T1 T, ST2, S가T3 됩니다.

————————————————————————————————————————

HRT-ST-MESI 프로토콜

IBM 특허 취득 HRT-ST-MESI 프로토콜[11][12]

- 상태 = 잘못된 태그(*) – 잘못된 데이터

- H 상태 = 유효한 태그 – 잘못된 데이터

- 캐시 초기화 시 I 상태가 설정되며 프로세서의 읽기 또는 쓰기 실패 후에만 상태가 변화합니다.이 상태에서는 더 이상 반환되지 않습니다.

- H는 I 상태와 동일한 기능을 가지고 있지만 디렉토리의 태그와 일치하는 버스 트랜잭션을 캡처하고 데이터 캐시를 업데이트할 수 있습니다.

- 최초 사용 후 I는 기능상 H로 대체된다.

- - 주요 기능은 다음과 같습니다.

- - 회신 쓰기

- - T-M-R-E로부터의 깨끗한 데이터 공유와 더러운 데이터 양쪽에 대한 개입

- - 태그 부착(공유 태그 부착) 상태 예약

- - 잘못된 Hover(Hover) 자동 업데이트

(*) – 주의:정의용 태그는 항상 유효하지만 캐시 라인의 첫 번째 업데이트까지 비활성화된 것으로 간주됩니다.이는 이 라인이 아직 필요없고 사용되지 않은 경우에도 캐시를 업데이트하지 않도록 하기 위해서입니다.

————————————————————————————————————————

POWER4 IBM 프로토콜

상태 M-T-Me-S-I -Mu-SL = RT-MESI+Mu[9]

- - '공유회선'의 사용

- 멀티코어/모듈 시스템에서 사용– 멀티 L2 캐시

- 이 프로토콜은 다중 모듈 시스템에서 다중 L2 캐시를 사용하는 시스템의 RT-MESI 프로토콜과 동일합니다.

- SL - RT-MESI의 R에 해당하는 "공유된 마지막"

- Me - "유효한 독점" = E

- Mu: 요청되지 않은 변경 상태

- - 특수 상태 – 로드 및 스토어 더블워드 예약 요청 (64비트 구현용)

- S로부터의L 「공유 개입」은, 같은 모듈의 L2 캐시간에만 행해집니다.

- T로부터의 '더티 개입'은 같은 모듈의 L2 캐시 사이에서만 이루어집니다.

- 운용

- - 쓰기 할당

- - 개입 : M-T-VE-SL = M-O-E-SL

- - 쓰기 무효

- - 카피백 : M-T 교환

- - 주의: T 및 SL – 로케일 모듈에만 개입

————————————————————————————————————————

프로토콜에 대한 일반적인 고려 사항

경우에 따라서는 가장 효율적이고 완전한 프로토콜이 HRT-ST-MESI 프로토콜인 것으로 판명되었습니다.

- - 회신 쓰기

- - 공유 클린 데이터보다 더러운 데이터 모두 개입

- - Tagged 상태의 예약 상태(Shared-Tagged)

- - 비활성 H(Hover) 상태 자동 업데이트

레퍼런스

- ^ 공유 메모리를 탑재한 멀티프로세서 시스템– http://www.freepatentsonline.com/5701413.html

- ^ 크로스바 인터커넥트 유닛을 갖춘 멀티프로세서 컴퓨터 시스템에서 데이터를 전송하는 방법– http://www.google.com/patents/EP0923032A1?cl=en

- ^ PowerScale Bus Arbitration Protocol 사양 및 검증:LOTOS에 대한 산업 실험, 제2장, 제4페이지– ftp://ftp.inrialpes.fr/pub/vasy/publications/cadp/Chehaibar-Garavel-et-al-96.pdf

- ^ a b c d e f g h i j k l m n o p , Archibald, J. 및 Baer, 1986 – 캐시 일관성 프로토콜: 멀티프로세서 시뮬레이션 모델을 사용한 평가.ACM 트랜스컴퓨터시스템 4, 4(1986년 3월), 273-298 – http://ctho.org/toread/forclass/18-742/3/p273-archibald.pdf

- ^ a b MPC7400 RISC 마이크로프로세서 사용자 매뉴얼– http://pccomponents.com/datasheets/MOT-MPC7400.PDF

- ^ a b c d e f g 데이터 및 지침에 대해 최근에 읽은 상태의 캐시 일관성 프로토콜 – IBM 특허 – http://www.google.com/patents/US5996049

- ^ a b 인텔 ® QuickPath 인터커넥트 소개– http://www.intel.ie/content/dam/doc/white-paper/quick-path-interconnect-introduction-paper.pdf

- ^ a b 멀티프로세서 시스템 캐시 일관성에서의 포워드 스테이트– 인텔 - https://www.google.com/patents/US6922756

- ^ a b c d "POWER4 System Microarchitecture", http://www.cc.gatech.edu/~bader/COURS/UNM/ece637-Fall 2003/papers/TDF02.pdf 2013-11-07 아카이브 완료

- ^ IBM PowerPC 476FP L2 Cache 핵심 데이터북 – https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/8D5342097498C81A852575C50078D867/$file/L2CacheController_v1.5_ext_Pub.pdf

- ^ a b c d e f g 인사 상태를 포함한 Cache 일관성 프로토콜 – IBM 특허 – https://www.google.com/patents/US6275908

- ^ a b c d e f g h 수정된 값에 대한 태그 부착 상태를 포함한 Cache 일관성 프로토콜 – IBM 특허 – http://www.google.com/patents/US6334172

- ^ MPC750UM/D 12/2001 Rev.1 MPC750 RISC 마이크로프로세서 패밀리 사용자 매뉴얼– http://www.freescale.com/files/32bit/doc/ref_manual/MPC750UM.pdf

- ^ a b c d Pentium Pro 및 Pentium II 시스템 아키텍처 페이지 160 – Di T.Shanley – https://books.google.com/books?id=MLJClvCYh34C&pg=PA160&lpg=PA160&dq=Pentium+protocol+cache&source=bl&ots=gaOu-EvaTy&sig=QQEM1krp-H_0KUhi5Ti2bmxU2kU&hl=it&sa=X&ei=Zt6KT7icG8TE4gShzaDwCQ&ved=0CDcQ6AEwAg#v=onepage&q=Pentium%20protocol%20cache&f=false

- ^ AMD64 테크놀로지– AMD64 아키텍처 프로그래머 매뉴얼 제2권 : 시스템 프로그래밍– http://developer.amd.com/wordpress/media/2012/10/24593_APM_v21.pdf Wayback Machine에서 2016-03-03 아카이브 완료

- ^ a b c Sweazey, P. 및 Smith, A. J. 호환되는 캐시 일관성 프로토콜 클래스 및 IEEE Futurebus에 의한 지원.제13회 컴퓨터 아키텍처 국제 심포지엄의 속행록.IEEE. New York, 1986, 페이지 414-423). – http://pdf.aminer.org/000/419/524/a_class_of_compatible_cache_consistency_protocols_and_their_support.pdf

- ^ 마크 S. 파파마르코스와 자낙 H. 파텔.ISCA '84: 제11회 컴퓨터 아키텍처 국제 심포지엄 진행, 348-354페이지, 뉴욕, 뉴욕, 미국, 1984.ACM – http://www.researchgate.net/publication/220771512_A_Low-Overhead_Coherence_Solution_for_Multiprocessors_with_Private_Cache_Memories/file/50463519b8d139e451.pdf

- ^ a b 캐시 메모리를 사용하여 프로세서 메모리트래픽을 참조해 주세요.컴퓨터 아키텍처에 관한 제10회 연례 국제 심포지엄 - ISCA '83의 속행.컴퓨터 아키텍처에 관한 국제 심포지엄:스웨덴 스톡홀름, 1983년 6월 13-17일 페이지 127-128 – http://courses.cs.vt.edu/cs5204/fall11-kafura/Papers/TransactionalMemory/Goodman-SnoopyProtocol.pdf

- ^ a b 고급 컴퓨터 건축, 2E 한 젊은이. 301– 디 황 교수 –https://books.google.com/books?id=m4VFXr6qjroC&pg=PA301.

- ^ a b c d 캐시 기억과 관련 일관성 프로토콜, 발명가 Ferruccio Zulian, 불 HN ISI–http://www.google.com/patents/EP0396940B1?cl=en.

- ^ a b x86-64 Multicore SMP 시스템에 캐시 건축과 Coherency 프로토콜 비교 –http://people.freebsd.org/~lstewart/articles/cache-performance-x86-2009.pdf.

- ^ a b 인텔 Nehalem 컴퓨터 아키텍처 캐시 구성 및 메모리 관리 http://gec.di.uminho.pt/Discip/MInf/cpd1011/PAC/material/nehalemPaper.pdf

- ^ David Kanter (2007-08-28), "The Common System Interface: Intel's Future Interconnect", Real World Tech: 5, retrieved 2012-08-12

- ^ 소규모 대칭 멀티프로세서 시스템에서 멀티스레드 애플리케이션을 위한 MESI Cache 일관성 프로토콜 최적화 – http://tibrewala.net/papers/mesi98/ 웨이백 머신에서 2016-10-22 아카이브