전계효과 트랜지스터

Field-effect transistor

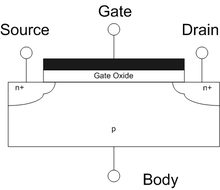

전계효과 트랜지스터(FET)는 전계를 사용하여 반도체의 전류 흐름을 제어하는 트랜지스터의 한 종류입니다.FET(JFET 또는 MOSFET)는 소스, 게이트 및 드레인 3개의 단자를 가진 장치입니다.FET는 게이트에 전압을 인가하여 전류 흐름을 제어하고, 게이트는 드레인 및 소스 간의 전도성을 변화시킵니다.

FET는 단극 트랜지스터라고도 합니다.단극 트랜지스터는 싱글 캐리어 타입의 동작을 수반하기 때문입니다.즉, FET는 동작 시에 전하 캐리어로서 전자(n채널) 또는 홀(p채널) 중 하나를 사용합니다(둘 다 사용되지는 않습니다).다양한 유형의 전계효과 트랜지스터가 존재합니다.전계효과 트랜지스터는 일반적으로 저주파수에서 매우 높은 입력 임피던스를 나타냅니다.가장 널리 사용되는 전계효과 트랜지스터는 MOSFET(금속 산화물 반도체 전계효과 트랜지스터)입니다.

역사

전계효과 트랜지스터(FET)의 개념은 1925년[1] 오스트리아-헝가리 물리학자 줄리어스 에드가 릴렌펠트와 1934년 오스카 헤이엘에 의해 처음 특허를 얻었지만, 그들은 그 개념을 바탕으로 실용적인 반도체 소자를 만들 수 없었다.트랜지스터 효과는 17년 특허가 만료된 직후인 1947년 벨 연구소에서 윌리엄 쇼클리 밑에서 일하는 동안 존 바딘과 월터 하우저 브래튼에 의해 관찰되고 설명되었다.쇼클리는 처음에 반도체의 전도성을 조절하여 작동하는 FET를 구축하려고 시도했지만, 주로 표면 상태, 매달림 결합, 게르마늄 및 구리 화합물 재료의 문제 때문에 성공하지 못했습니다.기능하는 FET를 구축하지 못한 이면에 있는 불가사의한 이유를 이해하려고 하는 과정에서, 바딘과 브래튼은 대신 1947년에 포인트 접점 트랜지스터를 발명했고,[2][3] 1948년에는 쇼클리의 양극 접합 트랜지스터가 그 뒤를 이었다.

성공적으로 제작된 첫 번째 FET 소자는 접합 전계효과 트랜지스터(JFET)[2]였습니다.JFET는 1945년 [4]하인리히 웰커에 의해 처음 특허를 받았다.채널이 짧은 JFET의 일종인 정적 유도 트랜지스터(SIT)는 일본의 기술자인 니시자와 준이치와 Y에 의해 발명되었다.1950년 와타나베.1952년 쇼클리가 JFET에 대해 이론적으로 처리한 후, 실용적인 JFET가 조지 F에 의해 만들어졌습니다.1953년 [5]데이시와 이안 M. 로스.그러나 [6]JFET는 일반적으로 접합 트랜지스터에 영향을 미치는 문제가 여전히 있었습니다.접합 트랜지스터는 대량 생산 기준으로 제조하기 어려운 비교적 부피가 큰 장치였기 때문에 많은 특수 용도에 한정되었습니다.절연 게이트 전계효과 트랜지스터(IGFET)는 접합 트랜지스터의 잠재적 대안으로 이론화되었지만, 연구자들은 주로 외부 전계가 물질 [6]안으로 침투하는 것을 막는 성가신 표면 상태 장벽 때문에 작동하는 IGFET를 만들 수 없었습니다.1950년대 중반까지 연구자들은 FET 개념을 대부분 포기하고 대신 양극 접합 트랜지스터([7]BJT) 기술에 집중했습니다.

MOSFET 기술의 기초는 윌리엄 쇼클리, 존 바딘, 월터 브래튼의 연구에 의해 구축되었다.쇼클리는 1945년에 독립적으로 FET 개념을 구상했지만 작동 장치를 만들 수 없었다.다음 해 바딘은 표면 상태의 관점에서 그의 실패를 설명했다.바딘은 표면 상태 이론을 반도체에 적용했고(표면 상태에 대한 이전 연구는 1939년 쇼클리와 1932년 이고르 탐에 의해 이루어졌다) 반도체 표면에 끌어당기는 여분의 전자 때문에 외부 장이 표면에서 막혔다는 것을 깨달았다.전자는 반전층을 형성하는 국소적인 상태에 갇히게 됩니다.바딘의 가설은 표면 물리학의 탄생을 알렸다.그 후 바딘은 쇼클리가 FET 설계에서 상상했던 매우 얇은 반도체 층 대신 반전층을 사용하기로 결정했다.그의 이론을 바탕으로 1948년 바딘은 반전층을 가진 절연 게이트 FET(IGFET)인 MOSFET의 시조 특허를 취득했다.반전층은 소수 캐리어들의 흐름을 제한하여 변조와 전도성을 증가시키지만, 전자 전달은 게이트의 절연체 또는 반전층 위에 퇴적된 산화물의 품질에 의존합니다.바딘의 특허와 반전층의 개념은 오늘날 CMOS 기술의 기초를 형성하고 있습니다.1976년 쇼클리는 바딘의 표면 상태 가설을 "반도체 프로그램에서 가장 중요한 연구 아이디어 중 하나"[8]라고 설명했다.

바딘의 표면 상태 이론 이후 세 사람은 표면 상태의 영향을 극복하려고 노력했다.1947년 후반, 로버트 기브니와 브래튼은 표면 상태의 영향을 극복하기 위해 금속과 반도체 사이에 전해질을 사용할 것을 제안했다.FET 장치는 작동했지만 증폭은 잘 되지 않았습니다.바딘은 더 나아가 반전층의 전도성에 초점을 맞추자고 제안했다.추가 실험을 통해 더 나은 결과를 얻기 위해 전해질을 고체 산화물로 대체했습니다.그들의 목표는 산화층을 관통하여 반전층에 도달하는 것이었다.그러나 바딘은 실리콘에서 게르마늄으로 전환하고 그 과정에서 산화물이 실수로 씻겨 내려갈 것을 제안했다.그들은 완전히 다른 트랜지스터인 포인트 접점 트랜지스터를 우연히 발견했다.릴리안 호데슨은 "브래튼과 바딘이 게르마늄 대신 실리콘으로 작업했다면 성공적인 전계효과 트랜지스터를 우연히 발견했을 것"이라고 주장한다.[8][9][10][11][12]

1950년대 전반의 말, 바딘, 브래튼, 킹스턴, 모리슨 등의 이론적이고 실험적인 작업에 따라, 표면 상태에는 두 가지 유형이 있다는 것이 더욱 분명해졌다.빠른 표면 상태는 벌크 및 반도체/산화물 인터페이스와 관련이 있는 것으로 확인되었습니다.표면 상태가 느린 것은 주위로부터의 산화물에 의한 원자, 분자 및 이온의 흡착으로 인해 산화물층과 관련이 있는 것으로 밝혀졌다.후자는 훨씬 더 많고 휴식 시간이 더 긴 것으로 밝혀졌다.당시 Philo Farnsworth와 다른 사람들은 원자적으로 깨끗한 반도체 표면을 만드는 다양한 방법을 생각해냈다.

1955년 칼 프로쉬와 링컨 데릭은 실수로 실리콘 웨이퍼의 표면을 이산화규소 층으로 덮었다.그들은 산화층이 실리콘 웨이퍼에 특정 도판트를 막는 동시에 다른 도판트를 허용함으로써 반도체 표면에 대한 산화의 소극적인 효과를 발견한다는 것을 보여주었다.이들의 추가 작업은 산화층의 작은 개구부를 식각하여 도판트를 실리콘 웨이퍼의 선택된 영역으로 확산시키는 방법을 시연했습니다.1957년, 그들은 연구 논문을 발표했고 그들의 연구를 요약한 그들의 기술을 특허 취득했다.그들이 개발한 기술은 산화물 확산 마스킹으로 알려져 있으며, 나중에 MOSFET 소자의 제조에 사용될 것입니다.벨 연구소에서, 프로슈의 기술의 중요성을 즉시 깨달았다.그들의 연구 결과는 1957년에 출판되기 전에 BTL 메모의 형태로 Bell Labs에 회람되었습니다.Shockley Semiconductor에서 Shockley는 1956년 12월에 Jean Hoerni를 [6][13][14]포함한 모든 고위 직원들에게 그들의 기사의 프리프린트를 배포했다.

1955년에 이안 먼로 로스는 FeFET 또는 MFSFET에 대한 특허를 신청했다.그 구조는 현대의 반전 채널 MOSFET와 비슷했지만, 산화물 대신 유전체/절연체로 강유전체 재료가 사용되었습니다.그는 그것을 기억의 형태로 상상했다, MOSFET보다 몇 년 전에.1957년 2월, 존 월마크는 일산화 게르마늄이 게이트 유전체로 사용되는 FET 특허를 신청했지만, 그는 그 아이디어를 추구하지 않았다.같은 해 출원된 다른 특허에서 그는 이중 게이트 FET를 기술했다.1957년 3월 Bell Labate의 연구 과학자인 Ernesto Labate는 실험실 수첩에서 나중에 제안된 MOSFET와 유사한 장치를 고안했지만 Labate의 장치는 이산화규소를 [15][16][17][18]절연체로 명시적으로 사용하지 않았습니다.

금속산화물반도체FET(MOSFET)

FET 연구의 획기적인 발전은 1950년대 후반 [3]이집트 엔지니어 모하메드 아탈라의 연구로 이루어졌다.1958년에 그는 깨끗한 실리콘 표면에서 얇은 실리콘 산화물을 성장시키면 표면 상태가 중화된다는 것을 보여주는 실험적인 연구를 발표했다.실리콘 집적회로의 양산을 [19][20]가능하게 하면서 반도체 산업에 중요한 수단이 된 표면 패시베이션(surface passivation)으로 알려져 있다.

금속 산화물 반도체 전계효과 트랜지스터(MOSFET)는 1959년 [21][22]모하메드 아탈라와 다원 칸에 의해 발명되었다.MOSFET는 바이폴라 트랜지스터와 JFET를 [2]대체하여 디지털 전자 개발에 [23][22]지대한 영향을 미쳤다.MOSFET는 높은 확장성,[24] 훨씬 낮은 전력 소비 및 양극성 접합 [25]트랜지스터보다 높은 밀도로 고밀도 집적회로를 [26]구축할 수 있었습니다.또한 MOSFET는 [27]JFET보다 높은 전력을 처리할 수 있습니다.MOSFET는 다양한 [6]용도로 소형화되고 대량 생산될 수 있는 최초의 진정한 콤팩트 트랜지스터였습니다.따라서 MOSFET는 컴퓨터, 전자,[20] 통신 기술(스마트폰 [28]등)에서 가장 일반적인 유형의 트랜지스터가 되었다.미국 특허상표청은 이를 "전세계의 삶과 문화를 변화시킨 획기적인 발명품"[28]이라고 칭한다.

MOSFET용 반도체 소자 제작 공정인 CMOS(Complementary MOS)는 1963년 [29][30]페어차일드 반도체에서 치탕사(Chih-Tang Sah)와 프랭크 완라스가 개발했다.플로팅 게이트 MOSFET에 대한 첫 보고서는 1967년 [31]다원 칸과 사이먼 스제에 의해 작성되었다.이중 게이트 MOSFET는 1984년 세키가와 토시히로 전기기술연구소 연구원과 하야시 [32][33]유타카 연구원에 의해 처음 시연되었다.3D 비평면 멀티게이트 MOSFET의 일종인 Fin Field-Effect Transistor(핀 [34][35]전계효과 트랜지스터)는 1989년 히타치 중앙연구소 다이히사모토 교수팀의 연구에서 비롯됐다.

기본 정보

FET는 주로 다수 캐리어에 의해 전류가 흐르는 다수 차지 캐리어 장치 또는 주로 소수 [36]캐리어 흐름에 의해 전류가 흐르는 소수 차지 캐리어 장치일 수 있습니다.이 장치는 전하 캐리어, 전자 또는 홀이 소스에서 드레인까지 흐르는 활성 채널로 구성됩니다.소스 및 드레인 단자 도체는 오믹 접점을 통해 반도체에 연결됩니다.채널의 전도율은 게이트 및 소스 터미널에 인가되는 전위의 함수입니다.

FET의 3개의 단자는 다음과 같습니다.[37]

- 송신원(S). 캐리어가 채널로 들어가는 데 사용됩니다.기존에는 S에서 채널로 들어가는 전류는 I에 의해S 지정된다.

- 드레인(D)을 통해 캐리어가 채널을 빠져나갑니다.종래, D로 채널에 들어가는 전류는 I에D 의해 지정된다.드레인-소스 전압은 V입니다DS.

- 채널 컨덕터빌리티를 변조하는 단자인 게이트(G).G에 전압을 인가함으로써 I을 제어할D 수 있다.

터미널에 대한 정보

모든 FET에는 BJT의 이미터, 컬렉터 및 베이스에 대략 대응하는 소스, 드레인 및 게이트 단자가 있습니다.대부분의 FET에는 바디, 베이스, 벌크 또는 기판이라고 불리는4번째 단자가 있습니다.이 네 번째 단자는 트랜지스터를 바이어스하여 동작시키는 역할을 합니다.회로 설계에서 바디 단자를 단순하지 않게 사용하는 경우는 드물지만 집적회로의 물리적 레이아웃을 설정할 때 그 존재가 중요합니다.게이트의 크기(그림에서 길이 L)는 소스와 드레인 사이의 거리입니다.폭은 다이어그램의 단면에 수직인 방향으로 트랜지스터의 연장입니다(즉, 화면 안/밖).일반적으로 너비는 게이트 길이보다 훨씬 큽니다.게이트 길이가 1µm이면 상한 주파수는 약 5GHz, 0.2µm은 약 30GHz로 제한됩니다.

터미널 이름은 해당 기능을 나타냅니다.게이트 단말기는 물리적 게이트의 개폐를 제어하는 것으로 간주할 수 있습니다.이 게이트는 소스와 드레인 사이의 채널을 만들거나 제거하여 전자가 통과하도록 허용하거나 통과를 차단합니다.소스단자에서 드레인단자로의 전자류는 인가전압의 영향을 받는다.본체는 단순히 게이트, 소스 및 드레인이 있는 반도체의 대부분을 가리킵니다.일반적으로 본체 단자는 FET 유형에 따라 회로 내에서 가장 높거나 가장 낮은 전압에 연결됩니다.송신 게이트나 캐스코드 회로 등, 그러한 구성을 가지지 않는 FET 를 사용하는 경우가 있습니다만, 소스는 회로내의 최고 또는 최저의 전압에 접속되어 있는 경우가 많기 때문에, 바디 단자와 소스 단자가 함께 접속되어 있는 경우가 있습니다.

BJT와 달리 대부분의 FET는 전기적으로 대칭적입니다.따라서 소스 단자와 드레인 단자는 작동 특성 또는 기능의 변화 없이 실제 회로에서 상호 교환할 수 있습니다.인쇄 회로 레이아웃 고려사항 등 다른 이유로 FET의 물리적 방향이 결정되었기 때문에 개략도 및 회로에서 FET가 "뒤로" 연결되어 있는 것처럼 보일 경우 이는 혼란스러울 수 있습니다.

전류에 대한 게이트 전압의 영향

FET는 게이트 단자와 소스 단자에 인가되는 전압(또는 전압 부족)에 의해 생성되고 영향을 받는 "전도 채널"의 크기와 모양에 영향을 줌으로써 소스에서 드레인까지의 전자(또는 전자 구멍)의 흐름을 제어합니다(간단히 하기 위해 이 설명은 본체와 소스가 연결되어 있다고 가정합니다).이 전도성 채널은 전자가 소스로부터 드레인까지 흐르는 "스트림"입니다.

n채널 FET

n채널의 "depletion-mode"디바이스에서 음의 게이트-소스 전압은 디폴트 영역의 폭을 넓히고 측면에서 채널을 잠식하여 채널을 좁힌다.활성 영역이 확장되어 채널이 완전히 닫히면 소스에서 드레인까지 채널의 저항이 커지고 스위치처럼 FET가 효과적으로 꺼집니다(전류가 매우 적은 경우 오른쪽 그림 참조).이를 "핀치 오프"라고 하며, 발생하는 전압을 "핀치 오프 전압"이라고 합니다.반대로 양의 게이트 대 소스 전압은 채널 크기를 증가시키고 전자를 쉽게 흐르게 합니다(전도 채널이 있고 전류가 큰 경우 오른쪽 그림 참조).

n채널의 '인핸스먼트 모드' 디바이스에서는 트랜지스터 내에 도전채널이 자연스럽게 존재하지 않으므로 이를 작성하기 위해서는 정의 게이트 대 소스 전압이 필요하다.양전압은 체내에서 자유롭게 떠다니는 전자를 게이트 쪽으로 끌어당겨 전도성 채널을 형성합니다.하지만 먼저, FET의 몸에 첨가된 도판트 이온에 대항하기 위해 게이트 근처에 충분한 전자를 끌어당겨야 합니다. 이것은 고갈 영역이라고 불리는 이동 캐리어가 없는 영역을 형성하며, 이것이 발생하는 전압을 FET의 임계값 전압이라고 합니다.게이트 대 소스 전압이 추가로 상승하면 더 많은 전자가 소스 대 드레인 채널을 활성화할 수 있는 게이트로 끌어당깁니다. 이 과정을 반전이라고 합니다.

p채널 FET

p채널 '감전모드' 디바이스는 게이트에서 체내로의 정전압이 게이트 절연체/반도체 계면에 전자를 강제함으로써 공핍층을 넓히고 고정적으로 대전된 수용체 이온의 캐리어 프리 영역을 노출시킨다.

반대로 p채널 "확장 모드" 장치에서는 전도 영역이 존재하지 않으므로 전도 채널을 생성하기 위해 음전압을 사용해야 합니다.

채널에 대한 드레인-소스 전압의 영향

증강 모드 또는 고갈 모드 장치의 경우, 게이트 대 소스 전압보다 훨씬 낮은 드레인 대 소스 전압에서 게이트 전압을 변경하면 채널 저항이 변경되고 드레인 전류는 드레인 전압에 비례합니다(소스 전압 참조).이 모드에서 FET는 가변 저항기처럼 작동하며 FET는 선형 모드 또는 ohmic [38][39]모드에서 작동한다고 합니다.

드레인-소스 전압이 증가하면 소스 간 전압 전위의 기울기로 인해 채널 형상에 현저한 비대칭 변화가 발생합니다.반전 영역의 모양은 채널의 드레인 엔드 부근에서 "핀치오프"됩니다.드레인 대 소스 전압이 더 높아지면 채널의 핀치오프 지점이 드레인에서 소스로 이동하기 시작합니다.FET는 포화 [40]모드라고 불리며, 일부 저자는 바이폴라 트랜지스터 작동 [41][42]영역과 더 잘 유사하기 위해 액티브 모드라고 부릅니다.포화 모드 또는 ohmic과 포화 사이의 영역은 증폭이 필요할 때 사용됩니다.드레인 전류가 드레인 전압과 거의 선형적이지 않은 경우에도 중간 영역은 오믹 영역 또는 선형 영역의 일부로 간주될 수 있습니다.

게이트 투 소스 전압에 의해 형성된 도전 채널이 포화 모드 중에 소스와 드레인 사이에 더 이상 접속되지 않아도 캐리어가 흐르는 것을 막지는 않는다.다시 n채널 인핸스먼트 모드 디바이스라고 하면 p형 본체에 도전채널과 드레인 및 소스 영역을 둘러싼 고갈 영역이 존재한다.채널을 구성하는 전자는 드레인-소스 전압에 의해 드레인 쪽으로 끌리면 고갈 영역을 통해 채널 밖으로 자유롭게 이동합니다.고갈 영역에는 캐리어가 없고 실리콘과 유사한 내성이 있습니다.드레인-소스 전압이 증가하면 드레인에서 핀치오프 지점까지의 거리가 증가하여 인가되는 드레인-소스 전압에 비례하여 고갈 영역의 저항이 증가합니다.이 비례적인 변화로 인해 드레인-소스 전류는 선형 작동 모드에서의 오믹 동작과는 달리 드레인-소스 전압의 변화와 무관하게 상대적으로 고정된 상태를 유지합니다.따라서 포화 모드에서 FET는 저항 대신 정전류 소스로 작동하며 효과적으로 전압 증폭기로 사용할 수 있습니다.이 경우 게이트-소스 전압에 따라 채널을 통과하는 정전류 레벨이 결정됩니다.

구성.

FET는 다양한 반도체로 구성될 수 있으며, 이 중 실리콘이 가장 일반적입니다.대부분의 FET는 기존의 벌크 반도체 처리 기술을 사용하여 단결정 반도체 웨이퍼를 활성 영역 또는 채널로 사용합니다.

보다 특이한 바디 재료로는 유기 반도체를 기반으로 하는 박막 트랜지스터 또는 유기 전계효과 트랜지스터(OFET)의 비정질 실리콘, 다결정 실리콘 또는 기타 비정질 반도체가 있습니다. OFET 게이트 절연체 및 전극도 유기 재료로 만들어집니다.FET는 탄화규소(SiC), 비화갈륨(GaAs), 질화갈륨(GaN), 비화인듐(InGaAs) 등 다양한 소재를 사용해 제조된다.

2011년 6월, IBM은 그래핀 기반 FET를 집적 [43][44]회로에 성공적으로 사용했다고 발표했습니다.이들 트랜지스터는 표준 실리콘 [45]FET보다 훨씬 높은 약 2.23GHz 컷오프 주파수를 사용할 수 있습니다.

종류들

FET의 채널은 n형 반도체 또는 p형 반도체를 생산하기 위해 도핑된다.드레인 및 소스는 확장 모드 FET의 경우 채널과 반대 유형의 도핑되거나 고갈 모드 FET에서와 유사한 유형의 도핑될 수 있습니다.전계효과 트랜지스터는 채널과 게이트 사이의 절연 방법으로도 구별됩니다.FET의 종류는 다음과 같습니다.

- MOSFET(금속 산화물 반도체 전계효과 트랜지스터)는 게이트와 본체 사이에 절연체(일반적으로2 SiO)를 사용합니다.이것은 지금까지 가장 일반적인 유형의 FET입니다.

- DGMOSFET(Dual-Gate MOSFET; 듀얼게이트 MOSFET) 또는 DGMOS(절연 게이트가 2개인 MOSFET).

- IGBT(절연 게이트 바이폴라 트랜지스터)는 전력 제어를 위한 장치입니다.쌍극성 주전도 채널과 결합된 MOSFET와 유사한 구조를 가지고 있습니다.이러한 전압은 일반적으로 200~3000V의 드레인-소스 전압 범위에 사용됩니다.전원 MOSFET는 여전히 1 ~200V의 드레인 투 소스 전압에 적합한 장치입니다.

- JLNT(Junctionless nanowire transistor)는 전계효과 트랜지스터(FET)의 일종으로 채널은 1개 또는 복수의 나노와이어이며 접점이 없습니다.

- MNOS(금속-질화물-산화물-반도체 트랜지스터)는 게이트와 본체 사이에 질화물-산화물층 절연체를 사용합니다.

- ISFET(이온 민감 전계 효과 트랜지스터)를 사용하여 용액의 이온 농도를 측정할 수 있습니다. 이온 농도(예+: H, pH 전극 참조)가 변화하면 트랜지스터를 통과하는 전류도 이에 따라 변경됩니다.

- BioFET(생물학적으로 민감한 전계효과 트랜지스터)는 ISFET 기술을 기반으로 하는 센서/바이오센서의 한 종류로, 하전된 분자가 존재할 경우 BioFET 표면의 정전장 변화로 인해 트랜지스터를 통해 측정 가능한 전류 변화가 발생합니다.여기에는 효소변형FET(EnFET), 면역변형FET(ImmunoFET), 유전자변형FET(GenFET), DNAFET(Cell-based BioFET), 딱정벌레/칩FET(BeetleFETs) 및 이온채널 [46]결합에 기초한 FET가 포함된다.

- DNAFET(DNA 전계효과 트랜지스터)는 일치하는 DNA 가닥을 검출하기 위해 단일 가닥 DNA 분자로 만들어진 게이트를 사용함으로써 바이오센서 역할을 하는 특수 FET입니다.

- 고밀도 프로세서 칩에 사용되는 finFET(GAFET 또는 게이트 올라운드 FET 포함)

- JFET(접합 전계 효과 트랜지스터)는 역방향 바이어스 p-n 접점을 사용하여 게이트를 차체에서 분리합니다.

- DEPFET는 완전히 방전된 기판에서 형성된 FET로 센서, 앰프 및 메모리 노드 역할을 동시에 수행합니다.이미지(광자) 센서로 사용할 수 있습니다.

- FREDFET(고속 후진 또는 고속 복구 에피택셜 다이오드 FET)는 차체 다이오드의 매우 빠른 복구(끄기)를 제공하도록 설계된 특수 FET로, 전기 모터, 특히 중출력 브러시리스 DC 모터와 같은 유도 부하를 구동하는 데 편리합니다.

- HIGFET(구조 절연 게이트 전계 효과 트랜지스터)는 현재 [47]주로 연구에 사용됩니다.

- MODFET(변조 도프 전계효과 트랜지스터)는 활성 영역의 단계적 도핑에 의해 형성된 양자 우물 구조를 사용하는 고전자 이동성 트랜지스터입니다.

- TFET(터널 전계효과 트랜지스터)는 대역간 [48]터널링을 기반으로 합니다.

- TQFET(토폴로지 양자 전계 효과 트랜지스터)는 인가된 [49]전계를 사용하여 2D 재료를 무방산 위상 절연체('ON' 상태)에서 기존 절연체('OFF' 상태)로 전환합니다.

- HEMT(High-electron-mobility transistor)는 HFET(Heterrostructure FET)라고도 불리며 AlGaAs와 같은 3원 반도체에서 밴드갭 공학을 사용하여 만들 수 있습니다.완전히 고갈된 광대역 갭 소재는 게이트와 차체 사이의 이격을 형성합니다.

- MESFET(금속-반도체 전계효과 트랜지스터)는 JFET의 p-n 접합부를 쇼트키 장벽으로 대체하며 GaAs 및 기타 III-V 반도체 재료에 사용됩니다.

- NOMFET는 나노 입자 유기 메모리 전계 효과 트랜지스터입니다.[50]

- GNRFET(그래핀나노리본전계효과트랜지스터)는 [51]채널로 그래핀나노리본을 사용한다.

- VeSFET(수직 슬릿 전계 효과 트랜지스터)는 반대쪽 모서리에서 소스와 드레인 사이를 연결하는 좁은 슬릿이 있는 정사각형 모양의 접점 없는 FET입니다.두 개의 게이트가 다른 쪽 모서리를 차지하고 있으며 [52]슬릿을 통해 전류를 제어합니다.

- CNTFET(카본 나노튜브 전계효과 트랜지스터).

- OFET(유기전계효과 트랜지스터)는 채널에 유기 반도체를 사용한다.

- 양자전계효과트랜지스터(QFET)는 양자터널링을 활용해 기존 트랜지스터의 전자전도 영역을 없애 트랜지스터 작동 속도를 크게 높인다.

- SB-FET(Shottky-Barrier 전계효과 트랜지스터)는 금속 소스 및 드레인 접점 전극이 있는 전계효과 트랜지스터로 소스 채널 [53][54]및 드레인 채널 인터페이스에서 모두 쇼트키 장벽을 생성합니다.

- GPET는 바이오센서 및 화학센서로 사용되는 매우 민감한 그래핀 기반의 전계효과 트랜지스터입니다.그래핀의 2차원 구조 및 물리적 특성으로 인해 GPET는 감도를 높이고 감지 애플리케이션에서[55] '허위 양성'의 발생을 줄입니다.

- Fe FET는 게이트 사이에 강유전체(강유전체)를 사용하여 바이어스가 없는 경우에도 트랜지스터가 상태를 유지할 수 있습니다. 이러한 장치는 비휘발성 메모리로 사용될 수 있습니다.

- VTFET(Vertical-Transport Field-Effect Transistor)는 2021년에 IBM이 고밀도 및 [56]저전력화를 위해 핀FET를 수정한 것입니다.

이점

전계효과 트랜지스터는 게이트 대 드레인 전류 저항이 100MΩ 이상으로 높아 제어와 흐름 사이에 높은 절연도를 제공한다.베이스 전류 노이즈는 쉐이핑[clarification needed] 시간이 [57]경과함에 따라 증가하므로 일반적으로 FET는 바이폴라 접합 트랜지스터(BJT)보다 노이즈가 적고 VHF 및 위성 수신기의 튜너 및 저노이즈 앰프 등의 노이즈에 민감한 전자제품에서 볼 수 있습니다.비교적 방사선에 대한 면역이 있다.드레인 전류가 0일 때 오프셋 전압이 없으며 우수한 신호 초퍼입니다.일반적으로 BJT보다 [37]열 안정성이 우수합니다.

FET는 게이트 전하에 의해 제어되기 때문에 게이트가 닫히거나 열리면 바이폴라 정션 트랜지스터 또는 비래칭 릴레이와 같이 추가적인 전력 소모가 없습니다.이것에 의해, 극히 저전력 스위칭이 가능하게 되어, 다른 타입의 스위치에 비해 열방산 요구가 감소하기 때문에, 회로의 소형화가 가능하게 됩니다.

단점들

전계효과 트랜지스터는 바이폴라 접합 트랜지스터에 비해 상대적으로 낮은 게인-대역폭 곱을 가진다.MOSFET는 과부하 전압에 매우 민감하기 때문에 설치 [58]시 특별한 취급이 필요합니다.게이트와 채널 사이에 있는 MOSFET의 취약한 절연층은 정전기 방전 또는 취급 시 임계값 전압에 대한 변화에 취약합니다.이것은, 통상, 디바이스를 적절한 설계의 회로에 설치한 후에는 문제가 되지 않습니다.

FET는 보통 매우 낮은 "on" 저항을 가지며 높은 "off" 저항을 가집니다.그러나 중간 저항은 중요하므로 전환 중에 FET가 대량의 전력을 소산할 수 있습니다.따라서 효율은 스위칭을 빠르게 할 수 있지만, 이로 인해 과도현상이 발생하여 미유인덕턴스를 자극하고 게이트에 결합되어 의도하지 않은 스위칭을 일으킬 수 있습니다.따라서 FET 회로는 매우 신중한 레이아웃이 필요하며 스위칭 속도와 전력 소산 간의 교환이 필요할 수 있습니다.또한 전압 정격과 "켜짐" 저항 사이에는 트레이드오프가 있으므로 고전압 FET는 상대적으로 "켜짐" 저항이 높기 때문에 전도 [59]손실이 발생합니다.

장애 모드

전계효과 트랜지스터는 특히 제조업체가 정의한 온도 및 전기적 한계 내에서 작동할 경우 비교적 견고합니다(적절한 감쇠).그러나 최신 FET 장치에는 종종 차체 다이오드가 포함될 수 있습니다.차체 다이오드의 특성을 고려하지 않으면 FET에서 느린 차체 다이오드 동작이 발생할 수 있으며, 이 경우 기생 트랜지스터가 켜지고 FET가 [60]꺼질 때 방전에서 소스로 고전류가 유입될 수 있습니다.

사용하다

이 섹션은 어떠한 출처도 인용하지 않습니다.(2018년 9월 (이 및 ) |

가장 일반적으로 사용되는 FET는 MOSFET입니다.CMOS(Complementary Metal Oxide Semiconductor) 공정 기술은 현대 디지털 집적회로의 기반이다.이 프로세스 기술은 (일반적으로 "확장 모드") p 채널 MOSFET와 n 채널 MOSFET가 직렬로 연결되어 한쪽이 켜지면 다른 한쪽이 꺼지는 구성을 사용합니다.

FET에서 전자는 선형 모드에서 작동할 때 채널을 통해 어느 방향으로든 흐를 수 있습니다.드레인 터미널과 소스 터미널의 명명 규칙은 다소 자의적입니다. 왜냐하면 디바이스는 일반적으로 (항상 그렇지는 않지만) 소스부터 드레인까지 대칭으로 구축되어 있기 때문입니다.따라서 FET는 경로 간에 아날로그 신호를 전환하는 데 적합합니다(멀티플렉싱).예를 들어 이 개념으로 솔리드 스테이트 믹싱 보드를 구성할 수 있습니다.FET는 일반적으로 앰프로 사용됩니다.예를 들어 입력 저항이 크고 출력 저항이 낮기 때문에 공통 드레인(소스 팔로어) 구성에서 버퍼로 효과적입니다.

IGBT는 빠른 전환 및 전압 차단 기능이 중요한 내연기관 점화 코일을 전환하는 데 사용됩니다.

소스 게이트 트랜지스터

소스 게이트 트랜지스터는 디스플레이 화면과 같은 대규모 전자 장치의 제조 및 환경 문제에 더 강력하지만 FET보다 [61]작동 속도가 느립니다.

「 」를 참조해 주세요.

레퍼런스

- ^ Lilienfeld, J.E. "전류를 제어하는 방법 및 장치" 미국 특허 No. 1,745,175(파일: 1926년 10월 8일, 발행: 1930년 1월 28일).

- ^ a b c Lee, Thomas H. (2003). The Design of CMOS Radio-Frequency Integrated Circuits (PDF). Cambridge University Press. ISBN 9781139643771. Archived from the original (PDF) on 2019-12-09. Retrieved 2019-07-20.

- ^ a b Puers, Robert; Baldi, Livio; Voorde, Marcel Van de; Nooten, Sebastiaan E. van (2017). Nanoelectronics: Materials, Devices, Applications, 2 Volumes. John Wiley & Sons. p. 14. ISBN 9783527340538.

- ^ Grundmann, Marius (2010). The Physics of Semiconductors. Springer-Verlag. ISBN 978-3-642-13884-3.

- ^ Nishizawa, Jun-Ichi (1982). "Junction Field-Effect Devices". In Sittig, Roland; Roggwiller, P. (eds.). Semiconductor Devices for Power Conditioning. Springer. pp. 241–272. doi:10.1007/978-1-4684-7263-9_11. ISBN 978-1-4684-7265-3.

- ^ a b c d Moskowitz, Sanford L. (2016). Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. p. 168. ISBN 9780470508923.

- ^ "The Foundation of Today's Digital World: The Triumph of the MOS Transistor". Computer History Museum. 13 July 2010. Retrieved 21 July 2019.

- ^ a b Howard R. Duff (2001). "John Bardeen and transistor physics". AIP Conference Proceedings. Vol. 550. pp. 3–32. doi:10.1063/1.1354371.

- ^ Hans Camenzind (2005). Designing Analog Chips.

- ^ ULSI Science and Technology/1997. 1997. p. 43. ISBN 9781566771306.

- ^ Lillian Hoddeson (1994). "Research on crystal rectifiers during World War II and the invention of the transistor". History and Technology. 11 (2): 121–130. doi:10.1080/07341519408581858.

- ^ Michael Riordan, Lillian Hoddeson (1997). Crystal Fire: The Birth of the Information Age. ISBN 9780393041248.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ Christophe Lécuyer; David C. Brook; Jay Last (2010). Makers of the Microchip: A Documentary History of Fairchild Semiconductor. pp. 62–63. ISBN 978-0262014243.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ Claeys, Cor L. (2003). ULSI Process Integration III: Proceedings of the International Symposium. The Electrochemical Society. pp. 27–30. ISBN 978-1566773768.

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. p. 324. ISBN 978-3540342588.

- ^ Stefan Ferdinand Müller (2016). Development of HfO2-Based Ferroelectric Memories for Future CMOS Technology Nodes. ISBN 9783739248943.

- ^ B.G Lowe; R.A. Sareen (2013). Semiconductor X-Ray Detectors. ISBN 9781466554016.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. p. 22. ISBN 978-0801886393.

- ^ "Martin Atalla in Inventors Hall of Fame, 2009". Retrieved 21 June 2013.

- ^ a b "Dawon Kahng". National Inventors Hall of Fame. Retrieved 27 June 2019.

- ^ "1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum.

- ^ a b Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 321–3. ISBN 9783540342588.

- ^ "960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum.

- ^ Motoyoshi, M. (2009). "Through-Silicon Via (TSV)". Proceedings of the IEEE. 97 (1): 43–48. doi:10.1109/JPROC.2008.2007462. ISSN 0018-9219. S2CID 29105721.

- ^ "Transistors Keep Moore's Law Alive". EETimes. 12 December 2018. Retrieved 18 July 2019.

- ^ "Who Invented the Transistor?". Computer History Museum. 4 December 2013. Retrieved 20 July 2019.

- ^ Duncan, Ben (1996). High Performance Audio Power Amplifiers. Elsevier. p. 177. ISBN 9780080508047.

- ^ a b "Remarks by Director Iancu at the 2019 International Intellectual Property Conference". United States Patent and Trademark Office. June 10, 2019. Retrieved 20 July 2019.

- ^ "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Retrieved 6 July 2019.

- ^ 1960년에 출원된 미국 특허 3,102,230, 1963년에 발행된

- ^ D. Kahng과 S. M. Sze, "떠다니는 게이트와 메모리 장치에 대한 그것의 적용", The Bell System Technical Journal, vol. 46, no. 4, 1967, 페이지 1288–1295

- ^ Colinge, J.P. (2008). FinFETs and Other Multi-Gate Transistors. Springer Science & Business Media. p. 11. ISBN 9780387717517.

- ^ Sekigawa, Toshihiro; Hayashi, Yutaka (1 August 1984). "Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate". Solid-State Electronics. 27 (8): 827–828. Bibcode:1984SSEle..27..827S. doi:10.1016/0038-1101(84)90036-4. ISSN 0038-1101.

- ^ "IEEE Andrew S. Grove Award Recipients". IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Retrieved 4 July 2019.

- ^ "The Breakthrough Advantage for FPGAs with Tri-Gate Technology" (PDF). Intel. 2014. Retrieved 4 July 2019.

- ^ Jacob Millman (1985). Electronic devices and circuits. Singapore: McGraw-Hill International. p. 397. ISBN 978-0-07-085505-2.

- ^ a b Jacob Millman (1985). Electronic devices and circuits. Singapore: McGraw-Hill. pp. 384–385. ISBN 978-0-07-085505-2.

- ^ Galup-Montoro, C.; Schneider, M.C. (2007). MOSFET modeling for circuit analysis and design. London/Singapore: World Scientific. p. 83. ISBN 978-981-256-810-6.

- ^ Norbert R Malik (1995). Electronic circuits: analysis, simulation, and design. Englewood Cliffs, NJ: Prentice Hall. pp. 315–316. ISBN 978-0-02-374910-0.

- ^ Spencer, R.R.; Ghausi, M.S. (2001). Microelectronic circuits. Upper Saddle River NJ: Pearson Education/Prentice-Hall. p. 102. ISBN 978-0-201-36183-4.

- ^ Sedra, A. S.; Smith, K.C. (2004). Microelectronic circuits (Fifth ed.). New York: Oxford University Press. p. 552. ISBN 978-0-19-514251-8.

- ^ PR Gray; PJ Hurst; SH Lewis; RG Meyer (2001). Analysis and design of analog integrated circuits (Fourth ed.). New York: Wiley. pp. §1.5.2 p. 45. ISBN 978-0-471-32168-2.

- ^ Bob Yirka (10 January 2011). "IBM creates first graphene based integrated circuit". Phys.org. Retrieved 14 January 2019.

- ^ Lin, Y.-M.; Valdes-Garcia, A.; Han, S.-J.; Farmer, D. B.; Sun, Y.; Wu, Y.; Dimitrakopoulos, C.; Grill, A; Avouris, P; Jenkins, K. A. (2011). "Wafer-Scale Graphene Integrated Circuit". Science. 332 (6035): 1294–1297. Bibcode:2011Sci...332.1294L. doi:10.1126/science.1204428. PMID 21659599. S2CID 3020496.

- ^ Belle Dumé (10 December 2012). "Flexible graphene transistor sets new records". Physics World. Retrieved 14 January 2019.

- ^ Schöning, Michael J.; Poghossian, Arshak (2002). "Recent advances in biologically sensitive field-effect transistors (BioFETs)" (PDF). Analyst. 127 (9): 1137–1151. Bibcode:2002Ana...127.1137S. doi:10.1039/B204444G. PMID 12375833.

- ^ freepatentsonline.com, HIGFET 및 방법 - Motorola]

- ^ Ionescu, A. M.; Riel, H. (2011). "Tunnel field-effect transistors as energy-efficient electronic switches". Nature. 479 (7373): 329–337. Bibcode:2011Natur.479..329I. doi:10.1038/nature10679. PMID 22094693. S2CID 4322368.

- ^ Dumé, Isabelle (12 December 2018). "Topological off-on switch could make new type of transistor". Physics World. IOP Publishing. Retrieved 16 January 2022.

- ^ "Organic transistor paves way for new generations of neuro-inspired computers". ScienceDaily. January 29, 2010. Retrieved January 14, 2019.

- ^ Sarvari H.; Ghayour, R.; Dastjerdy, E. (2011). "Frequency analysis of graphene nanoribbon FET by Non-Equilibrium Green's Function in mode space". Physica E: Low-dimensional Systems and Nanostructures. 43 (8): 1509–1513. Bibcode:2011PhyE...43.1509S. doi:10.1016/j.physe.2011.04.018.

- ^ Jerzy Ruzyllo (2016). Semiconductor Glossary: A Resource for Semiconductor Community. World Scientific. p. 244. ISBN 978-981-4749-56-5.

- ^ Appenzeller, J, et al. (November 2008). "Toward Nanowire Electronics". IEEE Transactions on Electron Devices. 55 (11): 2827–2845. Bibcode:2008ITED...55.2827A. doi:10.1109/ted.2008.2008011. ISSN 0018-9383. OCLC 755663637. S2CID 703393.

- ^ Prakash, Abhijith; Ilatikhameneh, Hesameddin; Wu, Peng; Appenzeller, Joerg (2017). "Understanding contact gating in Schottky barrier transistors from 2D channels". Scientific Reports. 7 (1): 12596. arXiv:1707.01459. Bibcode:2017NatSR...712596P. doi:10.1038/s41598-017-12816-3. ISSN 2045-2322. OCLC 1010581463. PMC 5626721. PMID 28974712.

- ^ Miklos, Bolza. "What Are Graphene Field Effect Transistors (GFETs)?". Graphenea. Retrieved 14 January 2019.

- ^ IBM Research, 2021년 12월 2배 성능의 혁신적인 새로운 칩 아키텍처 'VTFET' 공개

- ^ VII.5 트랜지스터 노이즈

- ^ Allen Mottershead (2004). Electronic devices and siraj circuits. New Delhi: Prentice-Hall of India. ISBN 978-81-203-0124-5.

- ^ Bhalla, Anup (2021-09-17). "Origins of SiC FETs and Their Evolution Toward the Perfect Switch". Power Electronics News. Retrieved 2022-01-21.

- ^ 전계효과 트랜지스터(FET)의 느린 차체 다이오드 고장: 도입 사례

- ^ Sporea, R.A.; Trainor, M.J.; Young, N.D.; Silva, S.R.P. (2014). "Source-gated transistors for order-of-magnitude performance improvements in thin-film digital circuits". Scientific Reports. 4: 4295. Bibcode:2014NatSR...4E4295S. doi:10.1038/srep04295. PMC 3944386. PMID 24599023.

외부 링크

- PBS 전계효과 트랜지스터

- 반도체 및 트랜지스터(MOSFET) WeCanFigure 작동 방식ThisOut.org

- 접합 전계 효과 트랜지스터

- CMOS 게이트 회로

- CMOS 아날로그 스위치에서의 래치업과의 싸움에서 이기다

- 이론 및 실제에서의 전계효과 트랜지스터

- 전압 제어 저항으로서의 전계 효과 트랜지스터

- "The FET (field effect transistor)". rolinychupetin (L.R.Linares). March 30, 2013 – via YouTube.